Xilinx 7系列FPGA收发器架构之共享功能(四)

引言:GTX/GTH收发器在FPGA上电和配置后必须进行初始化,GTX/GTH收发器的发送器(TX)和接收器(RX)可以独立和并行初始化。本文内容相对枯燥,操作细节较多,但对于深入理解收发器具有重要意义。通过本文可以了解一下内容:

- FPGA GTX/GTH收发器初始化和复位流程

- FPGA GTX/GTH收发器TX全局初始化和复位及TX组件复位操作

- FPGA GTX/GTH收发器RX全局初始化和复位及RX组件复位操作(简述)

1.FPGA GTX/GTH收发器初始化概述

FPGA GTX/GTH收发器初始化包含两个部分:

- 初始化驱动TX/RX的PLL

- 初始化TX/RX数据路径(PMA+PCS)

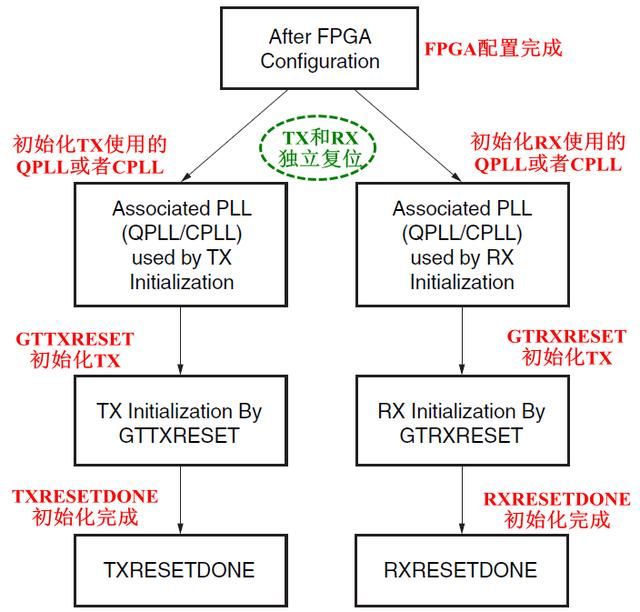

TX/RX数据路径初始化使用的QPLL/CPLL时钟必须首先初始化,即只有在QPLL/CPLL锁定定后,才能进行TX/RX初始化。GTX/GTH收发器初始化流程图如图1所示。

图1、GTX/GTH收发器初始化流程图

GTX/GTH收发器使用状态机控制TX和RX初始化,允许PMA先初始化,PCS后初始化。同样,也允许正常操作时PMA、PCS和其内部的功能模块独立复位。收发器提供两种类型复位:

- 初始化复位:该服用用来执行GTX/GTH完成初始化,用在器件上电和配置时。正常操作时,GTTXRESET和GTRESET也用来复位GTX/GTH的TX和RX。

- 组件复位:该复位用来复位特殊事件或者收发器某些子部分,如PCS、PMA复位等。

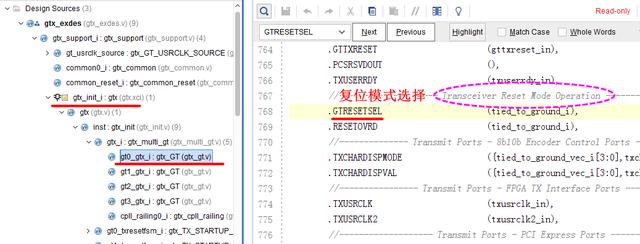

1.2 复位模式

GTX/GTH收发器有两种复位模式:顺序模式和单一模式。GTX/GTH收发器初始化复位必须使用顺序模式,所有的组件复位可以为顺序模式或者单一模式,但TX复位只能用单一模式,因此推荐使用顺序模式复位。

图2、复位模式

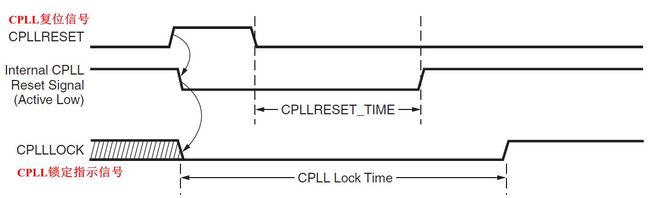

1.3 CPLL复位

在FPGA逻辑检测到参考时钟触发沿时CPLL一直处于关电状态。每个收发器有三个端口(Port)用来CPLL复位,如图3所示。CPLLRESET插入一个参考时钟高电平进行复位CPLL,CPLL复位完成后,CPLLLOCK用于指示复位完成。在图4中,我们可以看到,在gtx_gt.v文件中例化了CPL复位端口号。

图3、CPLL复位时序图

图4、CPLL复位端口

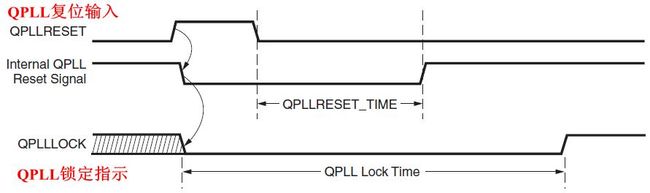

1.4 QPLL复位

QPLL复位和CPLL复位类似,QPLL在使用前必须进行复位。收发器的Quad也有三个专用的端口(Port)用于QPLL复位,含义类似CPLL,如图5所示。

图5、QPLL复位时序图

图7、QPLL复位端口

1.5 GTX/GTH收发器TX部分初始化和复位

1.5.1 GTX/GTH收发器TX初始化和复位状态机

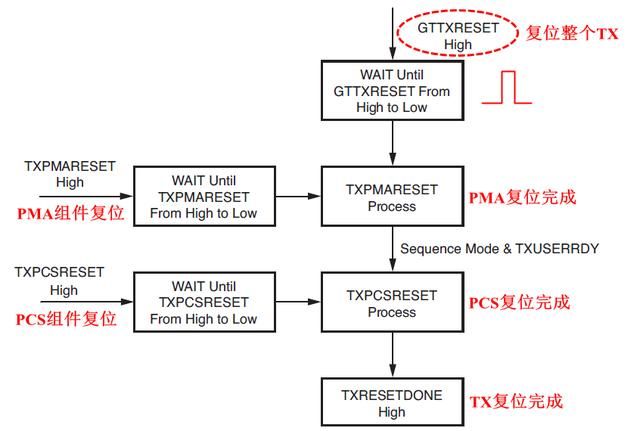

GTX/GTH收发器TX复位由如图8所示的状态机控制。通过执行一个GTTXRESET高开始复位TX,自动执行一个完整异步TX复位,包括PMA和PCS复位。只有当TXUSERRDY为高电平时,PCS才进行复位,而TXUSERRDY为高必须满足一下条件:

- 所有使用的时钟必须稳定或锁定

- 用户接口准备好发送数据到GTX/GTH发送器

图8、GTX/GTH收发器TX复位状态机顺序

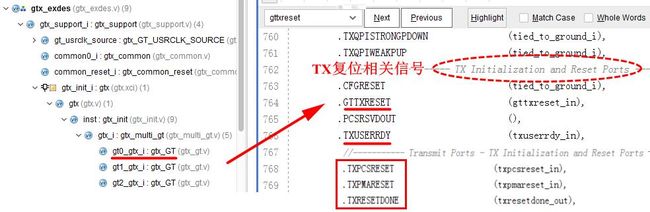

图9、GTX/GTH收发器TX复位信号端口

1.5.2 配置完成后的GTX/GTH收发器TX复位响应

图8所示的复位信号不会自动开始,它必须满足以下条件:

- GTRESETSEL必须为低电平(选择顺序复位模式)

- GTTXRESET必须使用

- 在TXRESETDONE拉高之前,TXPMARESET和TXPCSRESET信号必须一直为低

- 在使用的PLL锁定前,GTTXRESET必须一直为高

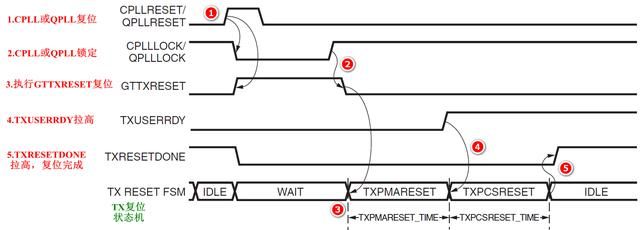

图10显示了GTX/GTH收发器TX在FPGA配置后的初始化时序图,复位先后顺序按照图中序号进行。

图10、GTX/GTH收发器TX在FPGA配置后的初始化时序图

1.5.3 GTTRESET脉冲复位后GTX/GTH收发器复位响应

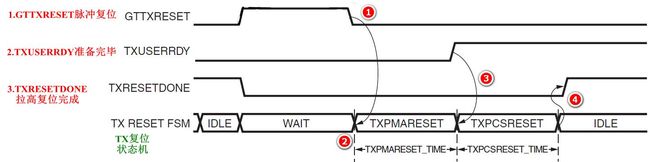

GTTRESET脉冲复位后的GTX/GTH收发器响应类似1.6小节中所描述,只不过不会引起CPLL或者QPLL复位。复位过程如图11所示。

图11、GTTRESET脉冲复位后GTX/GTH收发器复位响应

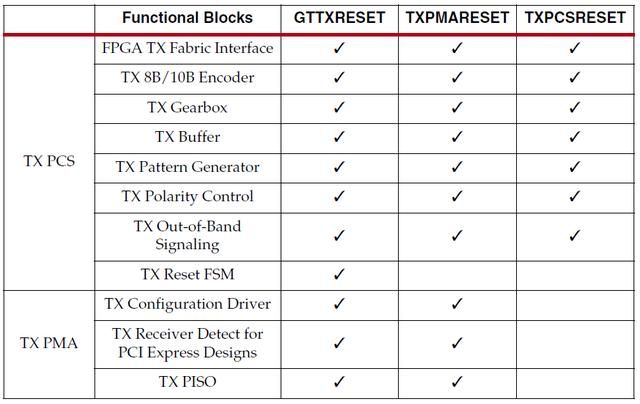

1.5.4 GTX/GTH收发器TX组件复位

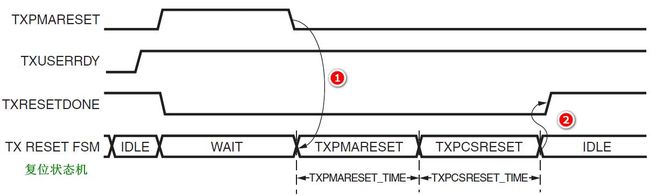

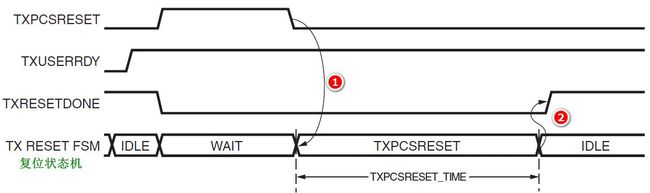

TX组件复位主要为PMA和PCS组件复位,两者复位较为简单,与前面分析方法也很类似,不再进行详细分析。图12和图13分别给出PMA和PCS复位时序图。

图12、TX组件PMA复位时序图

图13、TX组件PCS复位时序图

图12给出了GTTXRESET复位、PMA复位和PCS复位作用的组件范围。

图12、TX三种复位作用范围

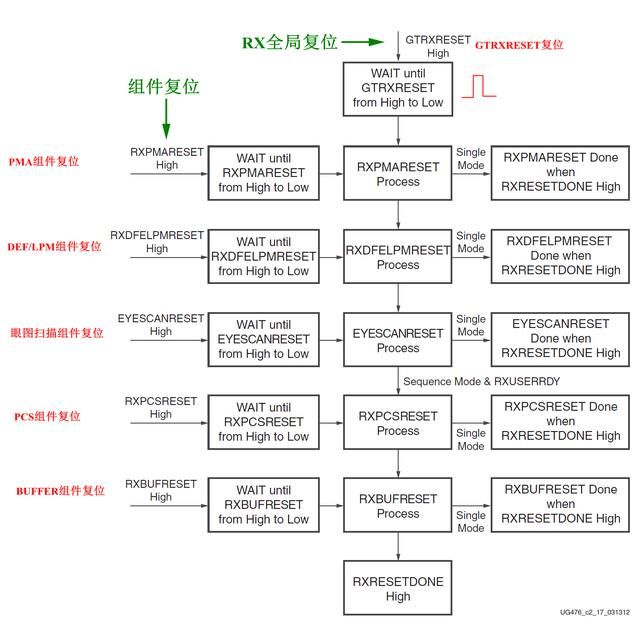

1.6 GTX/GTH收发器RX部分初始化和复位

GTX/GTH收发器RX部分初始化和TX部分初始化分析方法类似,相对于TX,RX复位涉及的组件较多,复位稍微复杂,但初始化和复位过程差别不大,不再进行更详细分析。图13显示了GTX/GTH收发器RX复位状态机顺序图。

图13、GTX/GTH收发器RX复位状态机顺序图

延伸阅读:Xilinx 7系列FPGA收发器架构之共享功能(三)

更多其他技术文章可以关注我的微信公众号“FPGA技术实战”,欢迎交流 !