PCI总线学习(一)---> PCI概述

幻灯片 2

幻灯片 3

幻灯片 4

北桥与cpu之间通过前端总线(FSB)连接,北桥与南桥通过root PCI总线互连。所以北桥扮演着host/PCI bridge角色。而南桥为PCI总线通向ISA总线(Industrial Standard Architecture,工业标准结构总线)的一个bridge,连接了PCI root bus和ISA bus,南桥一般包含中断控制器,IDE控制器,USB host控制器和DMA控制器。北桥和南桥组成了芯片组。左边是显卡专用接口部分,由于PCI总线带宽不能满足于显卡的数据传输。于是产生了AGP端口,现在已经被PCIE接口替代。

幻灯片 5

处理器无关。PCI设备是与PCI规范有关的,而于处理器无关,处理器的升级不影响PCI设备。即处理器设计改变,则处理器于北桥之间的通信方式可能改变,但北桥和设备之间通过PCI总线通信方式可以不变。

一条PCI bus理论上可以挂载32个设备,因为设备号是5位的,但是实际中由于总线承载能力有限,最多支持十个设备负载,每个设备最多可包含8个function,即8个逻辑设备,这样每条PCI总线最多可支持80个functions。

支持256条PCI总线,PCI总线号为8位。PCI总线和总线之间由PCI-to-PCI bridge互连。Root PCI总线号为0。

低功耗:表现为避免AD信号,C/BE信号和parity信号悬空,因为悬空超过一定的时间将会引发内部震荡,消耗电流。

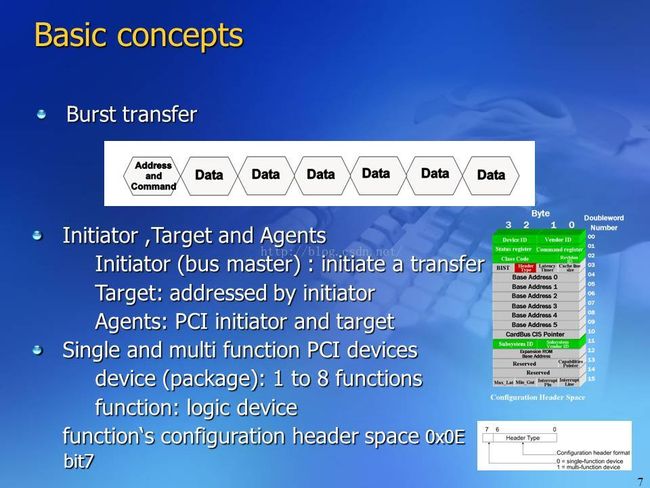

Burst transfer:一次数据传输中包含一个address phase和多个data phase。由bus master决定burst传输的长度。Bus master不会在传输开始时告诉target burst传输的长度,而是当传输最后一个data时通知target。

总线速度:spec2.1开始支持66MHz总线时钟,32bit数据宽度下可以达到264MB/s的传输率。

支持64bit扩展

访问时间最小60ns。

并行总线操作。PCI总线,前端总线,扩展总线可以同时工作。

Bus master,传输的发起者,bus master可以对同一条总线上的target设备进行访问,也可以通过bridge对其他PCI总线上的设备或者扩展总线上的设备或者主存进行访问

Hidden总线仲裁。当一个bus master正在进行传输时,进行总线仲裁工作决定下一个传输总线的所属者,称为隐藏总线仲裁, 省时。

Transaction完整性检查:对地址,命令,数据进行校验。

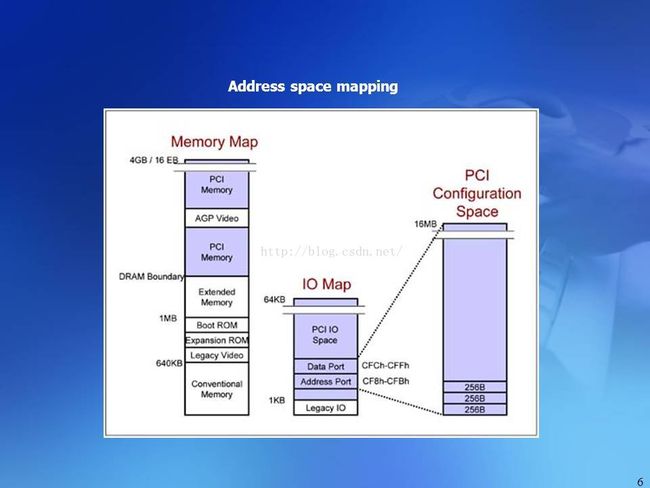

三个地址空间:memory,I/O和配置地址空间。Memory地址空间有4GB,用来访问主存,PCI IO地址空间有4GB,X86 IO空间只有64KB,用来访问外设。每个逻辑设备对应64Dword,256 bytes的配置空间。

幻灯片 6

PCI bus number共8 bits,device number 5bits,function number3bits,doubleword 6 bits,最低2bits为0,一共是24btis,可以访问的地址空间为16M bytes

256 bus*32 device*8function*256B =16M bytes 每个function对应256 bytes配置空间。

幻灯片 7

Burst transfer:一次数据传输中包含一个address phase和多个data phase。由bus master决定burst传输的长度。Bus master不会在传输开始时告诉target burst传输的长度,而是当传输最后一个data时通知target。

幻灯片 8

PCI clock:spec中规定,所有的PCI设备必须支持0M-33MHz范围内的PCI操作,为了低功耗和静态调式能力。集成在板子上的部件可能会设计为工作在固定的时钟频率,add-in card上的设备必须支持从0-33MHZ可变的工作频率。因为card可能工作在不同的平台。

Address phase:1个PCI clock

Start transaction:master assertFRAME#表明要开始一次transaction。

Claim the transaction:target assertsTRDY#信号表示target已经ready,即需要的data已经准备好。接着它会asserts DEVSEL# 信号来claimtransaction。

turn around cycle:当驱动总线的角色要发生转变时,中间会有一个turnaround cycle。

Transaction completion:Master deasserts FRAME#信号,表示它准备完成最后一个dataphase。

return of bus to idle state:IRDY# 和FRAME#信号同时为deasserted状态,表示总线空闲。

数据的传输都是在时钟上升沿发生的。