PCIe学习笔记之pcie结构和配置空间

PCIe概述

PCI Express,是计算机总线PCI的一种,它沿用现有的PCI编程概念及通信标准,但建基于更快的串行通信系统。

PCIE总线使用的是高速差分总线,并采用端到端的连接方式, 现在的高速总线基本上都是串行总线,这样可以使用更高的时钟频率。

当前pcie协议支持到5.0版本,不同PCIe版本对应的传输速率如下:

| PCIe 版本 | 编码 | 传输速率(GT/S) | x4吞吐量(MB/s) |

|---|---|---|---|

| 1.0 | 8b/10b | 2.5 | 1 |

| 2.0 | 8b/10b | 5 | 2 |

| 3.0 | 128b/130b | 8 | ~4 |

| 4.0 | 128b/130b | 16 | ~8 |

| 5.0 | 128b/130b | 32 | ~16 |

pcie总线的拓扑结构

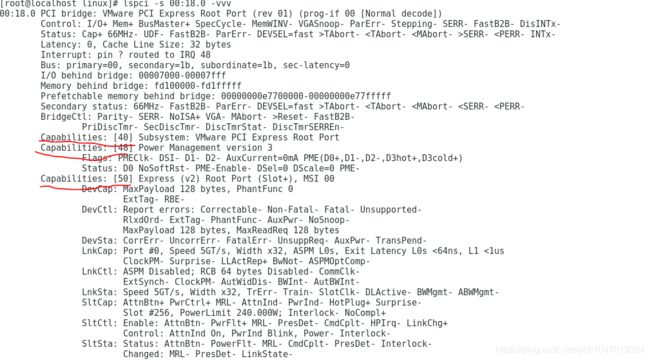

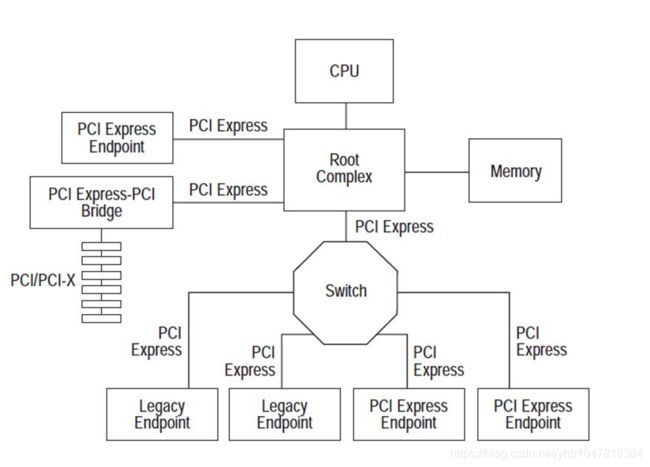

PCIe采用的是树形拓扑结构, 它的体系架构一般由root complex,switch,endpoint等类型的PCIe设备组成

root complex: 根桥设备,是PCIe最重要的一个组成部件; root complex主要负责PCIe报文的解析和生成。RC接受来自CPU的IO指令,生成对应的PCIe报文,或者接受来自设备的PCIe TLP报文,解析数据传输给CPU或者内存。

switch: PCIe的转接器设备,目的是扩展PCIe总线。和PCI并行总线不同,PCIe的总线采用了高速差分总线,并采用端到端的连接方式, 因此在每一条PCIe链路中两端只能各连接一个设备, 如果需要挂载更多的PCIe设备,那就需要用到switch转接器。switch在linux下不可见,软件层面可以看到的是switch的上行口(upstream port, 靠近RC的那一侧)和下行口(downstream port)。

一般而言,一个switch 只有一个upstream port, 可以有多个downstream port.

PCIe endponit: PCIe终端设备,是PCIe树形结构的叶子节点。比如网卡,NVME卡,显卡都是PCIe ep设备。

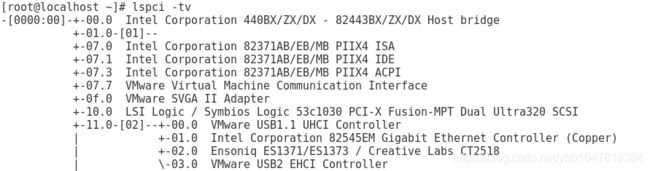

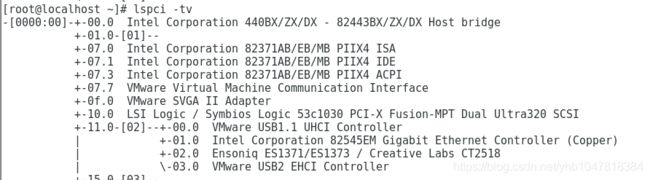

lspci -tv命令可以显示pcie的总线拓扑,如上图所示, 一个PCIe设备的ID由以下几个部分组成:

以0000:00:00.0为例,分别对应PCI域,总线号,设备号,功能号

- PCI域:PCI域ID,目的是为了突破pcie256条总线的限制。

- PCI总线号:pci设备的总线ID,占用8位,所以PCIe总线最多支持256个子总线。

- PCI设备号:指定总线上,pci的设备ID,Device Number占用5位, 所以每个子总线最多支持32个设备

- PCI功能号:指定设备上,pci设备的功能ID, 一个pci 物理设备可以实现多个功能设备,且逻辑功能相互独立,Function Number占用3位,所以每个物理设备最多支持8个功能。

BDF(Bus,device,function)构成了每个PCIe设备节点的身份标识。

PCIe配置空间

PCI有三个相互独立的物理地址空间:memory地址空间、I/O地址空间和配置空间。这三个地址空间都是采用唯一的地址进行寻址,比如我们使用地址0x100时需要指定这个地址在哪个地址空间,配置空间,I/O地址空间和memory地址空间的0x100偏移,对应的是不同的存储位置。

我们可以读取配置空间获得设备的信息,也可以通过配置空间来配置设备,通过pci设备的id和配置空间的偏移地址, 软件可以来访问具体的寄存器。

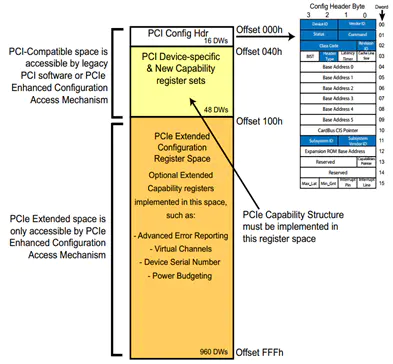

PCIe设备的每一个功能(function)都对应一个独立的配置空间, pcie的配置空间布局如下:

如上图所示,pci的配置空间是256字节,其中64字节是标准配置空间header, 后面的192字节是Capability结构, 展示pci能提供的能力。 为了兼容PCI,PCIe的配置空间前256字节与PCI保持一致,256~4096字节是pcie 扩展配置空间,包含pcie的扩展能力如AER。

1. PCI标准配置空间头(0 ~ 64 bytes)

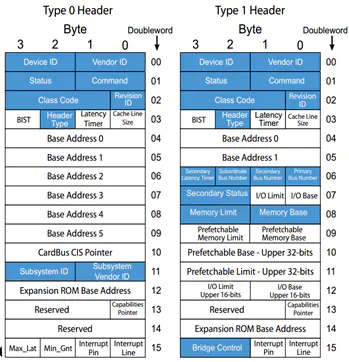

PCI标准配置空间分type0和type1两种。type0主要是针对PCI的endpoint设备,type1主要是针对PCI bridge, switch。

如上图所示,type0和type1有一些共同的寄存器描述。

Device ID: 设备ID, 表示该PCI设备的设备号,只读。

Vendor ID: 厂商ID, 表示生产该设备的厂商的编号,只读。

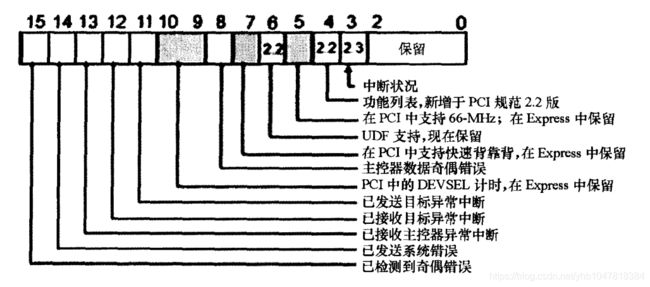

Status: pci设备状态寄存器,用于保存pci设备的状态,如中断状态或运行产生错误时的状态。

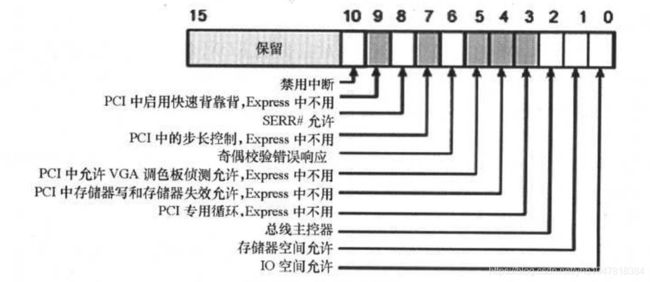

Command: PCI设备命令寄存器, 在pci设备使能pci_enable_device时会配置该寄存器。主要时负责使能或关闭pci设备的I/O 访问,memory访问和INTx中断等。

Class Code: 设备分类信息, 表示pci设备属于哪一种类别,如网卡,存储卡,显卡等。需要重点关注的一个寄存器,之前定位过一个问题,pci设备资源分配失败,就是因为将class code设置为0, 而那张卡是pcie 网卡, class code应该设置为2。

Revision ID: 设备版本ID, 表示PCI设备的版本号。该寄存器可以被认为是Device ID寄存器的扩展。 只读。

BIST: 可选,用于内部自检。

Header type: PCI设备头类型寄存器,表示该设备时pci EP设备还是PCI 桥设备。PCI配置空间时type0还是type1就是由该寄存器定于。

Lantency Timer: 在PCI总线中,多个设备共享同一条总线带宽,该寄存器用来控制PCI设备占用PCI总线的时间。PCIe设备不需要使用该寄存器,该寄存器的值必须为0。因为PCIe总线的仲裁方法与PCI总线不同,使用的连接方法也与PCI总线不同。

Cache line size: cache缓存大小。对于PCIe设备,该寄存器的值无意义。

Expansion Rom Base Address: 扩展ROM映射基地址寄存器。分配给ROM使用,用于PCI设备在处理器还没有运行操作系统之前,完成基本的初始化设置。

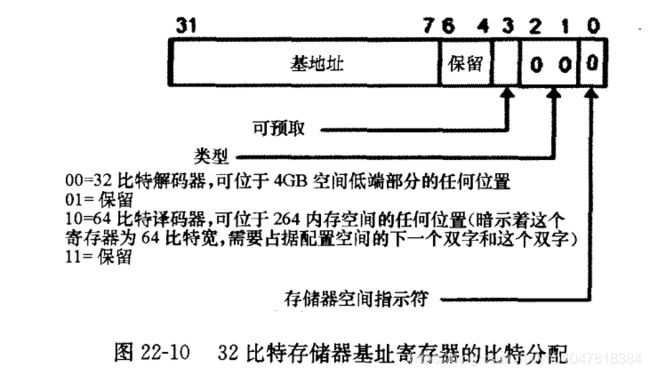

Base Address register: BAR地址寄存器负责PCI设备内部空间的映射。

type0有6个32bit的BAR寄存器,type1与2个32bit的BAR寄存器。每一个BAR地址对应一个地址空间。

在BAR寄存器有些bit是只读的,是PCI设备在出厂前就固定好的bit,写全1进去,如果值保持不变,就说明这些bit是厂家固化好的,这些固化好的bit提供了这块内部空间的一些信息。

举个例子:

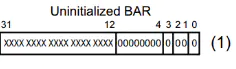

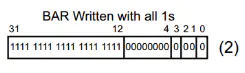

上电时,系统软件首先会读取PCIe设备的BAR0,得到数据:

然后系统软件往该BAR0写入全1,得到:

低12bit没变,表明该设备空间大小是4KB(2的12次方),BAR地址的低4位表明了该存储空间的一些属性([0]: IO映射还是memory映射,[2:1]32bit地址还是64bit地址,[3]能否可预取)。

然后系统软件根据这些信息,在系统内存空间找到这样一块地方来映射这4KB的空间,把分配的基地址写入到BAR寄存器。

BAR地址寄存器负责PCI设备内部空间的映射, 有了这个映射,CPU可以做到对pcie设备空间的访问。

比如CPU想去读PCIe设备的数据,系统启动时通过BAR地址把PCIe设备空间映射到内存空间,CPU要访问该PCIe设备空间,只需访问对应的内存空间。CPU发出一个物理地址,RC检查该地址,如果发现该内存空间地址是某个PCIe设备空间的映射,就会触发其产生TLP,去访问对应的PCIe设备,读取或者写入PCIe设备。

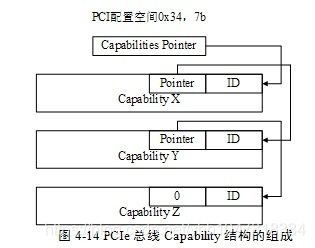

Capbility Pointer: PCI capbility的地址偏移, capbility用于表示pci设备支持的能力。该寄存器存放Capabilities 结构链表的头指针。在一个PCIe 设备中,可能含有多个Capability 结构,这些寄存器组成一个链表:

Interrupt Pin: PCI设备中断引脚,支持INTX A/B/C/D四个中断引脚。

Interrupt line: 表示当前PCI设备使用的中断号。

type0 独有的寄存器:

CardBus CISpointer: 只读,可选,用于表明访问CIS(card info structure)的地址空间, 通常不会涉及。

Subsystem ID/ subsystem Vendor ID: 子系统和子厂商ID,可以结合Device ID和Vendor ID来组成完成的PCI设备标识。

Max_lat: 设备期望的最大延时,只读。

Min_Gbt: 设备期望的最小延时,只读。

type1 独有的寄存器:

Primary Bus Number: 表示PCI设备挂在的PCI总线号。

Subordinate Bus Number: PCI桥可以管理其下的PCI总线子树。其中Subordinate Bus Number寄存器存放当前PCI子树中,编号最大的PCI总线号。

Secondary Bus Number: 存放当前PCI桥Secondary Bus使用的总线号,这个PCI总线号也是该PCI桥管理的PCI子树中编号最小的PCI总线号

Secondary Latency Timer: PCI桥下游的延时寄存器,和Latency Timer寄存器的含义相近

I/O base: 表示IO寻址的基地址, 低4bit只读,所以PCI设备默认IO寻址4K对齐,高4bit可写。

I/O limit: IO寻址的上限,高4bit可写,低4bit为全F,所以io寻址上限是I/O limit地址 + 4K.

Secondary status: 保存PCI下游总线和设备的状态。

Memory Base: 表示memory寻址的基地址。

Memory Limit: 表示memroy寻址的上限,和IO limit类似。

Prefetchable Memory Base: 可预期内存的基地址

Prefetchable Memory Limit: 可预期内存寻址的上限。

Bridge Control Register:管理PCI桥的Secondary Bus, 可以控制 Secondary Bus的 Reset。

2. PCI capbility结构(64 ~ 256bytes)

这段空间主要存放一些与MSI/MSI-X中断机制和电源管理相关的capbility。

在内核include/uapi/linux/pci_regs.h归纳了capabilityID和各个capability名称的对应关系:

/* Capability lists */

#define PCI_CAP_LIST_ID 0 /* Capability ID */

#define PCI_CAP_ID_PM 0x01 /* Power Management */

#define PCI_CAP_ID_AGP 0x02 /* Accelerated Graphics Port */

#define PCI_CAP_ID_VPD 0x03 /* Vital Product Data */

#define PCI_CAP_ID_SLOTID 0x04 /* Slot Identification */

#define PCI_CAP_ID_MSI 0x05 /* Message Signalled Interrupts */

#define PCI_CAP_ID_CHSWP 0x06 /* CompactPCI HotSwap */

#define PCI_CAP_ID_PCIX 0x07 /* PCI-X */

#define PCI_CAP_ID_HT 0x08 /* HyperTransport */

#define PCI_CAP_ID_VNDR 0x09 /* Vendor specific */

#define PCI_CAP_ID_DBG 0x0A /* Debug port */

#define PCI_CAP_ID_CCRC 0x0B /* CompactPCI Central Resource Control */

#define PCI_CAP_ID_SHPC 0x0C /* PCI Standard Hot-Plug Controller */

#define PCI_CAP_ID_SSVID 0x0D /* Bridge subsystem vendor/device ID */

#define PCI_CAP_ID_AGP3 0x0E /* AGP Target PCI-PCI bridge */

#define PCI_CAP_ID_EXP 0x10 /* PCI Express */

#define PCI_CAP_ID_MSIX 0x11 /* MSI-X */

#define PCI_CAP_ID_AF 0x13 /* PCI Advanced Features */

#define PCI_CAP_LIST_NEXT 1 /*Next capability in the list */

#define PCI_CAP_FLAGS 2 /* Capability defined flags (16 bits) */

#define PCI_CAP_SIZEOF 4

3. PCIe 扩展配置空间(256 ~ 4K bytes)

这段空间主要存放PCIe独有的一些capbility结构,如AER, SR-IOV等。

pcie扩展能力定义如下:

/* Extended Capabilities (PCI-X 2.0 and Express) */

#define PCI_EXT_CAP_ID(header) (header & 0x0000ffff)

#define PCI_EXT_CAP_VER(header) ((header >> 16) & 0xf)

#define PCI_EXT_CAP_NEXT(header) ((header >> 20) & 0xffc)

#define PCI_EXT_CAP_ID_ERR 0x01 /* Advanced Error Reporting */

#define PCI_EXT_CAP_ID_VC 0x02 /* Virtual Channel Capability */

#define PCI_EXT_CAP_ID_DSN 0x03 /* Device Serial Number */

#define PCI_EXT_CAP_ID_PWR 0x04 /* Power Budgeting */

#define PCI_EXT_CAP_ID_RCLD 0x05 /* Root Complex Link Declaration */

#define PCI_EXT_CAP_ID_RCILC 0x06 /* Root Complex Internal Link Control */

#define PCI_EXT_CAP_ID_RCEC 0x07 /* Root Complex Event Collector */

#define PCI_EXT_CAP_ID_MFVC 0x08 /* Multi-Function VC Capability */

#define PCI_EXT_CAP_ID_VC9 0x09 /* same as _VC */

#define PCI_EXT_CAP_ID_RCRB 0x0A /* Root Complex RB? */

#define PCI_EXT_CAP_ID_VNDR 0x0B /* Vendor-Specific */

#define PCI_EXT_CAP_ID_CAC 0x0C /* Config Access - obsolete */

#define PCI_EXT_CAP_ID_ACS 0x0D /* Access Control Services */

#define PCI_EXT_CAP_ID_ARI 0x0E /* Alternate Routing ID */

#define PCI_EXT_CAP_ID_ATS 0x0F /* Address Translation Services */

#define PCI_EXT_CAP_ID_SRIOV 0x10 /* Single Root I/O Virtualization */

#define PCI_EXT_CAP_ID_MRIOV 0x11 /* Multi Root I/O Virtualization */

#define PCI_EXT_CAP_ID_MCAST 0x12 /* Multicast */

#define PCI_EXT_CAP_ID_PRI 0x13 /* Page Request Interface */

#define PCI_EXT_CAP_ID_AMD_XXX 0x14 /* Reserved for AMD */

#define PCI_EXT_CAP_ID_REBAR 0x15 /* Resizable BAR */

#define PCI_EXT_CAP_ID_DPA 0x16 /* Dynamic Power Allocation */

#define PCI_EXT_CAP_ID_TPH 0x17 /* TPH Requester */

#define PCI_EXT_CAP_ID_LTR 0x18 /* Latency Tolerance Reporting */

#define PCI_EXT_CAP_ID_SECPCI 0x19 /* Secondary PCIe Capability */

#define PCI_EXT_CAP_ID_PMUX 0x1A /* Protocol Multiplexing */

#define PCI_EXT_CAP_ID_PASID 0x1B /* Process Address Space ID */

#define PCI_EXT_CAP_ID_DPC 0x1D /* Downstream Port Containment */

#define PCI_EXT_CAP_ID_L1SS 0x1E /* L1 PM Substates */

#define PCI_EXT_CAP_ID_PTM 0x1F /* Precision Time Measurement */

#define PCI_EXT_CAP_ID_MAX PCI_EXT_CAP_ID_PTM

#define PCI_EXT_CAP_DSN_SIZEOF 12

#define PCI_EXT_CAP_MCAST_ENDPOINT_SIZEOF 40

PCIE配置空间的访问

CPU可以通过访问BAR地址读取PCIe的设备空间,但是我们需要读取到配置空间才能获取BAR,那么怎么访问PCIe的配置空间呢?

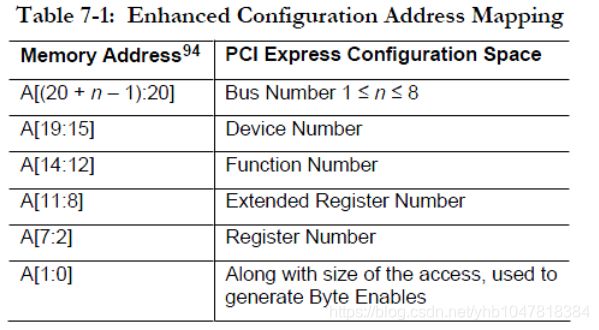

ARM使用ECAM的方式访问PCIe配置空间。ECAM是一个将配置空间映射到MEMORY空间的规则。硬件根据ECAM的方式将某个Memory空间映射给PCI配置空间,CPU访问对应的memory空间即可以操作PCIe配置空间。

映射的地址定义如下:

PCIe总线最多支持256个子总线,每个子总线最多支持32个设备,每个设备最多支持8个功能, 每个配置空间是4KB,所以需要映射256 buses × 32 devices × 8 functions × 4 KiB = 256 MiB 空间的大小。

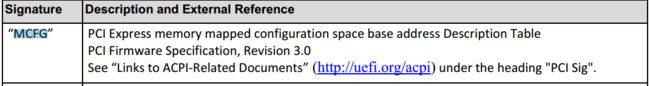

在ACPI规范中,需要通过MCFG表上报ECAM的地址映射

完成映射后,CPU发出的地址如果落在ECAM的范围内, 根据对应的bdf就可以访问到对应ep的配置空间了。

Linux内核中的MCFG实现读/写分别对应函数pci_read_config_byte/word/dword 和 pci_write_config_byte/word/dword

EXPORT_SYMBOL(pci_bus_read_config_byte);

EXPORT_SYMBOL(pci_bus_read_config_word);

EXPORT_SYMBOL(pci_bus_read_config_dword);

EXPORT_SYMBOL(pci_bus_write_config_byte);

EXPORT_SYMBOL(pci_bus_write_config_word);

EXPORT_SYMBOL(pci_bus_write_config_dword);

PCIe常用命令

lspci

查看pci设备拓扑结构: lspci -tv

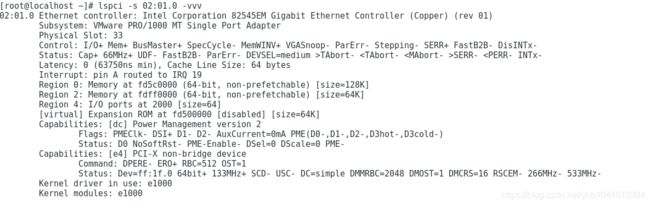

**查看pci设备详细信息: -s [b:d: f] **

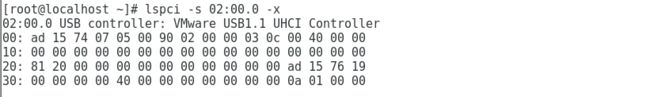

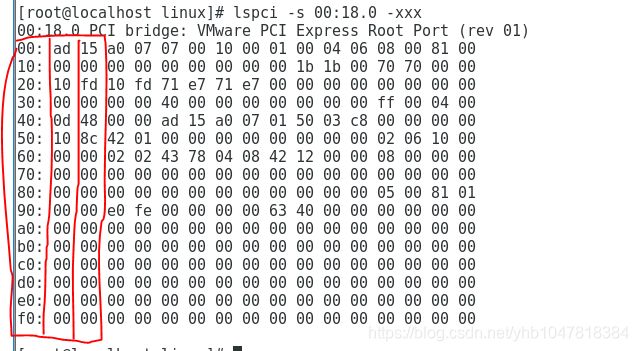

16进制查看pci设备配置空间:

举个例子:

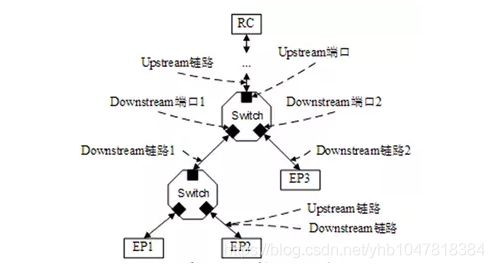

查看设备的详细信息

红色框框中的第一列对应具体的偏移,第二列对应的是设备的capability id, 第三列对应的是next capability id的偏移。

所以40: 0d 48 ===> 表示偏移0x40的位置的capability id是0xd(SSVID); 它指向的下一个capability位于0x48处,偏移0x48的位置的capability id是0x1(即power management); 它指向的下一个capabity位于0x50处,偏移0x50的位置的capability id是0x10(MSI);它指向的下一个capability位于0x8c处, 偏移0x8c的位置的capability id为0x0, 查找结束。

setpci

可以用setpci命令修改配置空间

setpci -s 00:00.0 0x地址.L=0x值 --修改设备地址的数值,一次修改4个字节

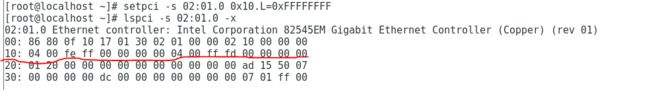

举个例子, 上面有提到往pci设备的BAR寄存器写全1可以计算BAR空间的大小需求

[root@localhost ~]# lspci -s 02:01.0 -x

02:01.0 Ethernet controller: Intel Corporation 82545EM Gigabit Ethernet Controller (Copper) (rev 01)

00: 86 80 0f 10 17 01 30 02 01 00 00 02 10 00 00 00

10: 04 00 5c fd 00 00 00 00 04 00 ff fd 00 00 00 00

20: 01 20 00 00 00 00 00 00 00 00 00 00 ad 15 50 07

30: 00 00 00 00 dc 00 00 00 00 00 00 00 07 01 ff 00

网卡设备的pci配置头空间如上所示, 通过setpci --dumpregs可以查看寄存器偏移

[root@localhost ~]# setpci --dumpregs

cap pos w name

00 W VENDOR_ID

02 W DEVICE_ID

04 W COMMAND

06 W STATUS

08 B REVISION

09 B CLASS_PROG

0a W CLASS_DEVICE

0c B CACHE_LINE_SIZE

0d B LATENCY_TIMER

0e B HEADER_TYPE

0f B BIST

10 L BASE_ADDRESS_0

14 L BASE_ADDRESS_1

18 L BASE_ADDRESS_2

1c L BASE_ADDRESS_3

20 L BASE_ADDRESS_4

24 L BASE_ADDRESS_5

......

BAR0的偏移是0x10, 通过setpci命令写该地址全F

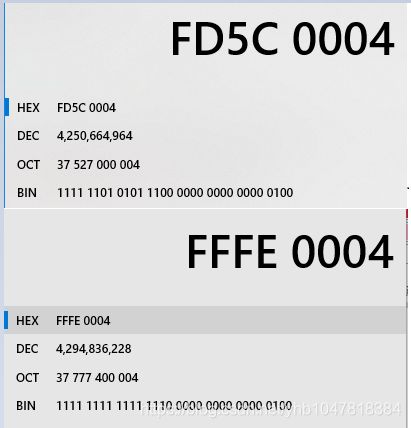

刚开始的BAR0的值为fd5c0004, 写过全F后,BAR0的值为fffe0004

最低位可写入的bit是18(低4bit不算bar地址,是特殊标记)

所以该BAR的空间大小是2^18 = 256K.

参考资料

PCI桥与PCI设备的配置空间

老男孩读PCIe之六:配置和地址空间

PCI.EXPRESS系统体系结构标准教材