89c51中断系统及中断控制

现代的计算机都具有实时处理功能,当外界有突发事件时,cpu能够及时的做出处理,这就是靠中断来实现的。

当CPU正在处理某一命令时,这时外部发生了某一事件(如电平的变化,或者定时器/计数器溢出时)请求CPU去处理该事件,于是CPU停止处理当前的事件,并保存当前停止时的地址,转去处理所发生的事件,处理完毕后,CPU返回原先保存的停止时的地址,继续处理原先的事件,这样的过程被称为中断。

上图即为中断过程示意图,产生中断的请求源被称为中断源,中断源向CPU提出的处理请求被称为中断请求或中断申请。CPU暂时中止当前的事件,转去处理中断请求所对应的事件称为CPU的中断响应过程,对事件的整个处理过程称为中断服务(中断处理)。处理完毕后,返回到原先被中止的地方称为中断返回。

因为有中断请求时,CPU当前执行的的程序是随机的,所以CPU在执行中断服务程序之前,除了硬件会自动把断点地址压入堆栈外,还要注意保护现场数据(相关的工作寄存器,累加器,标志位等信息),以便于在执行完中断服务程序之后恢复原先数据(称为恢复现场)。

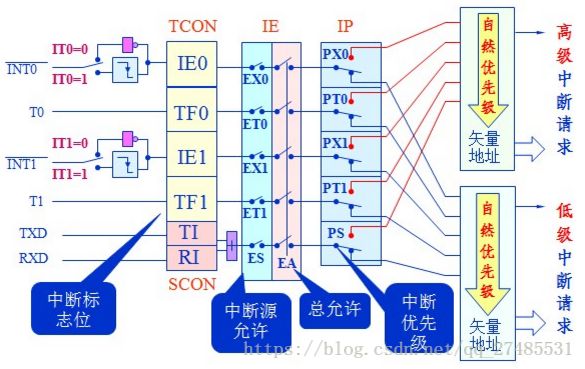

89c51单片机的中断系统如图所示

89c51有5个中断源:

INT0 :外部中断0请求,低电平有效。

INT1 : 外部中断1请求,低电平有效。

T0 : 定时/计数器0溢出中断请求。

T1 :定时/计数器1溢出中断请求。

TXD/RXD : 串口中断请求,当串口发送/接受完一帧数据时,便请求中断。

其中 INT0/1是两个外部中断,T0/1,TXD/RXD是3个内部中断

中断控制

89c51有以下4个特殊功能寄存器

定时器控制寄存器TCON(用6位);

串行口控制寄存器SCON(用2位);

中断允许寄存器IE;

中断优先级寄存器IP.

其中,TCON和SCON只有一部分位用于中断控制。通过对以上各种特殊功能寄存器的各位进行置位或复位操作,即可实现各种中断控制的功能。

1、TCON中的中断标志位

TF1 : 定时/计数器1的中断请求标志位,当定时/计数器溢出时,该位自动置1,并向CPU发出中断请求,当CPU响应中断时,硬件会自动对该位清0。当然,你也可以用“位操作指令”对TF0进行置“1”或清“0”操作。

TF0 :定时/计数器0的中断请求标志位,与TF1原理相同。

IE1 : 外部中断1的中断请求标志位,当检测到外部中断引脚上存在有效的中断请求信号时,由硬件自动使IE1置1,当CPU响应该中断请求时,由硬件自动使IE1清0。

IT1 : 外部中断1的中断触发方式控制位

IT1 = 0 时,外部中断1为电平触发方式。CPU在每一个机器周期采样外部中断1请求引脚的输入电平,若外部中断1请求引脚为低电平,则使IE1位置1,若为高电平,则IE1清0。

IT1 = 1 时,外部中断1为边沿触发方式。CPU如果在两个连续的机器周期采样过程中,一个为高电平。接着下一个为低电平,那么IE1则置1,直到CPU响应该中断时,才由硬件使IE1位清0。

IE0 : 外部中断0的中断请求标志位,与IE1原理相同。

IT0 : 外部中断0的中断触发方式控制位,与IT1原理相同。

2、串行控制寄存器SCON

TI : 串行口发送中断请求标志位。CPU将数据写入SBUF时,就启动发送,每发送完一帧串行数据后,硬件自动把TI位置1,但CPU响应中断时,并不清除TI,必须在中断服务程序中由软件对TI清0。

RI :串行口接收中断请求标志位,在串口允许接收时,每接收完一个串行帧,硬件自动对RI置1.同样CPU响应中断时不会清除RI位,必须用软件对其清0。

3、中断允许控制寄存器IE

89c51对中断源的开放和关闭由中断允许寄存器控制,格式如下

中断允许寄存器IE对中断的开放和关闭实现两级控制,所谓的两级控制就是有一个总的开关中断控制位EA,当EA=0时,屏蔽所有的中断申请,及任何中断申请都不接受,当EA=1时,CPU开放中断,但5个中断源还有由其所对应的控制位的状态进行中断的允许控制。

EA : 中断允许总控制位。 EA = 0 时,屏蔽所有的中断请求,EA = 1时,CPU开放中断,对于中断源的请求是否允许还要取决于各中断源的中断允许控制位的状态。

ES : 串行口中断允许控制位。ES = 0时,禁止串行口中断,ES = 1时,允许串行口中断。

ET1 ;定时/计数器1的溢出中断允许控制位。ET1 = 0时,禁止T1中断,ET1 = 1时,允许T1中断。

EX1 : 外部中断1中断允许控制位。EX1 = 0时,禁止外部中断1中断,EX1 = 1时,允许外部中断1中断。

ET0 : 定时/计数器0的溢出中断允许控制位。ET0 = 0时,禁止T0中断,ET0 = 1时,允许T0中断。

EX0 : 外部中断0中断允许控制位。EX0 = 0时,禁止外部中断0中断,EX0 = 1时,允许外部中断0中断。

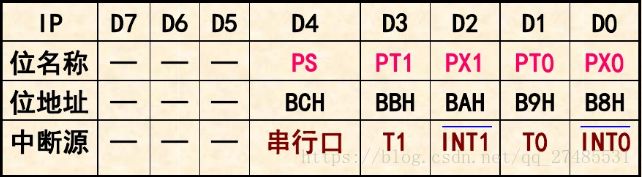

4、中断优先级控制寄存器

89c51有两个中断优先级,每一个中断请求源均可编程为高优先级中断和低优先级中断。

PS : 串行口中断优先级控制位,置1时,为高优先级,置0时,为低优先级。

PT1 : 定时/计数器1中断优先级控制位,控制方法同上。

PX1 : 外部中断1中断优先级控制位,控制方法同上。

PT0 : 定时/计数器0中断优先级控制位,控制方法同上。

PX0 : 外部中断0中断优先级控制位,控制方法同上。

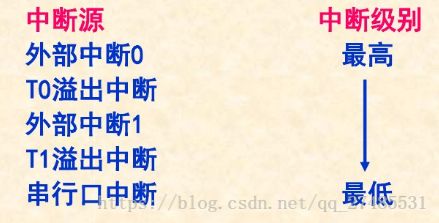

当同时接收到几个同一优先级的中断请求时,响应哪个中断源则取决于内部硬件的查询顺序,如下图所示

当CPU正在处理一个中断请求时,又出现了一个优先级比它高的中断请求时,这时CPU会暂时中止对低优先级中断源的处理,保护当前断点,转去响应优先级更高的中断请求。

89c51中断优先控制的基本原则:

高优先级的中断可以中断正在响应的低优先级的中断,反之则不能

同优先级中断不能互相中断

同一中断优先级中,若有多个中断源同时请求中断,则CPU先响应优先权高的中断,后响应优先权低的中断。