FPGA基础知识极简教程(9)七段数码管显示的Verilog简单设计

博文目录

-

- 写在前面

- 正文

-

- 七段数码管原理

- 七段数码管译码表

- 单个七段数码管显示verilog设计

- 多个数码管动态扫描显示

- 参考资料

- 交个朋友

写在前面

作为FPGA的基础知识教程怎么能少得了这个简单的实际应用七段数码管显示,本篇博文算得上是对以往这个话题的一个总结吧!

注:数码管本身是七段,但是加上小数点之后就是八段了!

正文

七段数码管原理

七段显示器是FPGA设计人员通常用来向用户显示信息的指示器。在VHDL和Verilog中可以轻松完成将二进制文件转换为兼容七段显示器的代码。有许多应用程序可能需要使用一个或多个八段显示器,例如:

- 闹钟

- 秒表

- 按钮计数指示器

- 电压测量(从模拟到数字转换器)

等等!

如下是七段数码管的示意图:我们将七段分别标记为A、B、C、D、E、F、G,还有一个小数点DP。

如果用reg型变量来存七段数码管的位值,定义reg型变量:

reg [6:0] seg;

其中G对应seg[6],F对应seg[5],一直到A对应seg[0],小数点用专门的dp来表示。

七段数码管译码表

那么要想显示0到F,对应的译码表为:

parameter NUM0 = 7'h3f,//40,

NUM1 = 7'h06,//79,

NUM2 = 7'h5b,//24,

NUM3 = 7'h4f,//30,

NUM4 = 7'h66,//19,

NUM5 = 7'h6d,//12,

NUM6 = 7'h7d,//02,

NUM7 = 7'h07,//78,

NUM8 = 7'h7f,//20,

NUM9 = 7'h6f,//10,

NUMA = 7'h77,//08,

NUMB = 7'h7c,//03,

NUMC = 7'h39,//46,

NUMD = 7'h5e,//21,

NUME = 7'h79,//06,

NUMF = 7'h71,//0e;

注意,前面部分为共阴极时的译码表,后面注释掉的为共阳极的译码表!

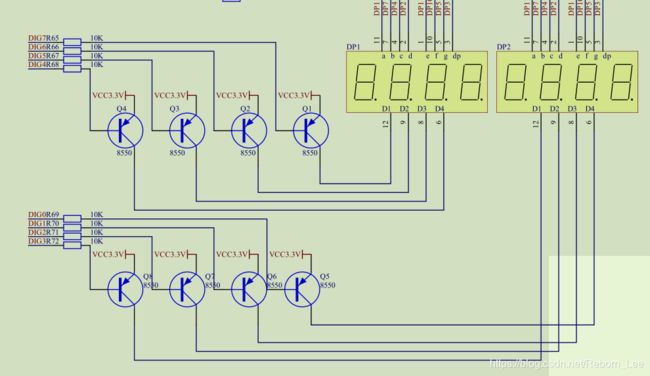

所谓的共阳极,如下原理图所示:

晶体管的集电极连接电源,片选低电平有效,片选选中时,晶体管导通,数码管公共端连接高电平,因此段选低电平,对应段发亮。

单个七段数码管显示verilog设计

以共阴极为例,对单个数码管显示的Verilog设计为:

module Binary_To_7Segment

(

input i_Clk,

input [3:0] i_Binary_Num,

input i_dp, //小数点输入

output o_Segment_A,

output o_Segment_B,

output o_Segment_C,

output o_Segment_D,

output o_Segment_E,

output o_Segment_F,

output o_Segment_G,

output o_dp

);

reg [6:0] r_Hex_Encoding = 7'h00;

// Purpose: Creates a case statement for all possible input binary numbers.

// Drives r_Hex_Encoding appropriately for each input combination.

always @(posedge i_Clk)

begin

case (i_Binary_Num)

4'b0000 : r_Hex_Encoding <= 7'h3f;

4'b0001 : r_Hex_Encoding <= 7'h06;

4'b0010 : r_Hex_Encoding <= 7'h5b;

4'b0011 : r_Hex_Encoding <= 7'h4f;

4'b0100 : r_Hex_Encoding <= 7'h66;

4'b0101 : r_Hex_Encoding <= 7'h6d;

4'b0110 : r_Hex_Encoding <= 7'h7d;

4'b0111 : r_Hex_Encoding <= 7'h07;

4'b1000 : r_Hex_Encoding <= 7'h7f;

4'b1001 : r_Hex_Encoding <= 7'h6f;

4'b1010 : r_Hex_Encoding <= 7'h77;

4'b1011 : r_Hex_Encoding <= 7'h7c;

4'b1100 : r_Hex_Encoding <= 7'h39;

4'b1101 : r_Hex_Encoding <= 7'h5e;

4'b1110 : r_Hex_Encoding <= 7'h79;

4'b1111 : r_Hex_Encoding <= 7'h71;

endcase

end // always @ (posedge i_Clk)

// r_Hex_Encoding[7] is unused

assign o_Segment_A = r_Hex_Encoding[0];

assign o_Segment_B = r_Hex_Encoding[1];

assign o_Segment_C = r_Hex_Encoding[2];

assign o_Segment_D = r_Hex_Encoding[3];

assign o_Segment_E = r_Hex_Encoding[4];

assign o_Segment_F = r_Hex_Encoding[5];

assign o_Segment_G = r_Hex_Encoding[6];

assign o_dp = i_dp;

endmodule // Binary_To_7Segment

多个数码管动态扫描显示

用一句话来描述多个数码管动态扫描显示,那就是,只要你闪的够快,你就看不出我灭过!

动态扫描显示就是如此,数码管的动态显示是对每个数码管采用分时复用的方式轮流点亮每个数码管,在同一时间只会点亮一个数码管。

分时复用的扫描显示利用了人眼的视觉暂留特性,如果公共端的控制信号刷新速度足够快,人眼就不会区分出LED的闪烁,认为4个数码管是同时点亮。

如下图是多个数码管连接的原理图:

片选控制信号的刷新速度必须足够快才能避免闪烁感,但也不能太快,以免影响数码管的开关切换,最佳的工作频率为1000Hz左右。如果FPGA的时钟为50MHz,那么至少跑5*10^4个周期,也即50000个周期刷新一次才行,我们知道2^16=65536,2^15=32768。

我们选择计数器位宽为16试试!

注:效果可以实际上板子测试决定,由于现在开发板不在手上,暂时并未验证怎么样!

代码中采用的是18位2进制数,高2位控制片选,低16位计数满一次,进位一次,高两位的变化时00——01——10——11——00——…,分别选中数码管的其中之一,使用case语句即可完成这个功能。

下面代码中的hex0、hex1、hex2、hex3是输入信号,用来控制数码管显示的数字,dp_in用来控制小数点的亮灭。

`timescale 1ns / 1ps

module scan_led_hex_disp(

input clk,

input reset,

input [3:0] hex0, //第一个数码管显示的数字

input [3:0] hex1,

input [3:0] hex2,

input [3:0] hex3,

input [3:0] dp_in, //小数点控制

output reg [3:0] an, //片选

output reg [7:0] sseg //段选

);

localparam N = 18; //使用低16位对50Mhz的时钟进行分频(50MHZ/2^16)

reg [N-1:0] regN; //高两位作为控制信号,低16位为计数器,对时钟进行分频

reg [3:0] hex_in; //段选控制信号

reg dp;

always@(posedge clk, posedge reset)

begin

if(reset)

regN <= 0;

else

regN <= regN + 1;

end

always@ *

begin

case(regN[N-1:N-2])

2'b00:begin

an = 4'b1110; //选中第1个数码管

hex_in = hex0; //数码管显示的数字由hex_in控制,显示hex0输入的数字;

dp = dp_in[0]; //控制该数码管的小数点的亮灭

end

2'b01:begin

an = 4'b1101; //选中第二个数码管

hex_in = hex1;

dp = dp_in[1];

end

2'b10:begin

an = 4'b1011;

hex_in = hex2;

dp = dp_in[2];

end

default:begin

an = 4'b0111;

hex_in = hex3;

dp = dp_in[3];

end

endcase

end

always@ *

begin

case(hex_in)

4'h0: sseg[6:0] = 7'b0000001; //共阳极数码管

4'h1: sseg[6:0] = 7'b1001111;

4'h2: sseg[6:0] = 7'b0010010;

4'h3: sseg[6:0] = 7'b0000110;

4'h4: sseg[6:0] = 7'b1001100;

4'h5: sseg[6:0] = 7'b0100100;

4'h6: sseg[6:0] = 7'b0100000;

4'h7: sseg[6:0] = 7'b0001111;

4'h8: sseg[6:0] = 7'b0000010;

4'h9: sseg[6:0] = 7'b0000100;

4'ha: sseg[6:0] = 7'b0001000;

4'hb: sseg[6:0] = 7'b1100000;

4'hc: sseg[6:0] = 7'b0110001;

4'hd: sseg[6:0] = 7'b1000010;

4'he: sseg[6:0] = 7'b0110000;

default: sseg[6:0] = 7'b0111000;

endcase

sseg[7] = dp;

end

endmodule

根据上一小节,单个数码管显示的Verilog设计,最后一段译码模块可以使用时序逻辑,也就是代码可以改为:

`timescale 1ns / 1ps

module scan_led_hex_disp(

input clk,

input reset,

input [3:0] hex0, //第一个数码管显示的数字

input [3:0] hex1,

input [3:0] hex2,

input [3:0] hex3,

input [3:0] dp_in, //小数点控制

output reg [3:0] an, //片选

output reg [7:0] sseg //段选

);

localparam N = 18; //使用低16位对50Mhz的时钟进行分频(50MHZ/2^16)

reg [N-1:0] regN; //高两位作为控制信号,低16位为计数器,对时钟进行分频

reg [3:0] hex_in; //段选控制信号

reg dp;

always@(posedge clk, posedge reset)

begin

if(reset)

regN <= 0;

else

regN <= regN + 1;

end

always@ *

begin

case(regN[N-1:N-2])

2'b00:begin

an = 4'b1110; //选中第1个数码管

hex_in = hex0; //数码管显示的数字由hex_in控制,显示hex0输入的数字;

dp = dp_in[0]; //控制该数码管的小数点的亮灭

end

2'b01:begin

an = 4'b1101; //选中第二个数码管

hex_in = hex1;

dp = dp_in[1];

end

2'b10:begin

an = 4'b1011;

hex_in = hex2;

dp = dp_in[2];

end

default:begin

an = 4'b0111;

hex_in = hex3;

dp = dp_in[3];

end

endcase

end

always@(posedge clk)

begin

case(hex_in)

4'h0: sseg[6:0] = 7'b0000001; //共阳极数码管

4'h1: sseg[6:0] = 7'b1001111;

4'h2: sseg[6:0] = 7'b0010010;

4'h3: sseg[6:0] = 7'b0000110;

4'h4: sseg[6:0] = 7'b1001100;

4'h5: sseg[6:0] = 7'b0100100;

4'h6: sseg[6:0] = 7'b0100000;

4'h7: sseg[6:0] = 7'b0001111;

4'h8: sseg[6:0] = 7'b0000010;

4'h9: sseg[6:0] = 7'b0000100;

4'ha: sseg[6:0] = 7'b0001000;

4'hb: sseg[6:0] = 7'b1100000;

4'hc: sseg[6:0] = 7'b0110001;

4'hd: sseg[6:0] = 7'b1000010;

4'he: sseg[6:0] = 7'b0110000;

default: sseg[6:0] = 7'b0111000;

endcase

sseg[7] = dp;

end

endmodule

注:由于代码都是根据过去的博客以及参考资料移植,导致命名方式没有统一,请注意;还有多个数码管显示时,数码管是共阳极的数码管,而单个数码管显示那一节,也就是上一节,使用的数码管是共阴极为例,因此,数码管译码部分数值不同,请注意!

参考资料

- 参考资料1

- 参考资料2

- 参考资料3

- 参考资料4

- 参考资料5

- 参考资料6

交个朋友

-

个人微信公众号:FPGA LAB

-

知乎:李锐博恩

-

FPGA/IC技术交流2020