- (179)时序收敛--->(29)时序收敛二九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛二九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (180)时序收敛--->(30)时序收敛三十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- (158)时序收敛--->(08)时序收敛八

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛八(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (159)时序收敛--->(09)时序收敛九

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛九(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (160)时序收敛--->(10)时序收敛十

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛十(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (153)时序收敛--->(03)时序收敛三

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)F

- (121)DAC接口--->(006)基于FPGA实现DAC8811接口

FPGA系统设计指南针

FPGA接口开发(项目实战)fpga开发FPGAIC

1目录(a)FPGA简介(b)IC简介(c)Verilog简介(d)基于FPGA实现DAC8811接口(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电

- FPGA复位专题---(3)上电复位?

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发

(3)上电复位?1目录(a)FPGA简介(b)Verilog简介(c)复位简介(d)上电复位?(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限

- (182)时序收敛--->(32)时序收敛三二

FPGA系统设计指南针

FPGA系统设计(内训)fpga开发时序收敛

1目录(a)FPGA简介(b)Verilog简介(c)时钟简介(d)时序收敛三二(e)结束1FPGA简介(a)FPGA(FieldProgrammableGateArray)是在PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。(b)

- 使用FPGA接收MIPI CSI RX信号并进行去抖动、RGB转YUV处理:FX3014 USB3.0 UVC传输与帧率控制源代码,FPGA实现MIPI CSI RX接收,去Debayer, RGB转

kVfINoSzdrt

fpga开发程序人生

fpgamipicsirx接收去debayer,rgb转yuv,fx3014usb3.0uvc传输与帧率控制源代码,具体架构看图,除dphy物理层外,mipi均为源码sensorimx219mipi源码mipi4lanecsirxraw10fpgamachXO3lf-690usb3.0fx301432bityuvdatawithframesync测试模式3280*246415fps1920*108

- FPGA_mipi

哈呀_fpga

fpga开发逻辑高速接口系统架构高速传输

1mipi接口mipi(移动行业处理器接口,是为高速数据传输量身定做的,旨在解决日益增长的高清图像(视频)传输的高带宽要求与传统接口低速率之间的矛盾。采用差分信号传输,在设计时需要按照差分设计的一般规则进行严格的设计。mipi协议提出之际,主要有2个应用,csi(摄像头串行接口),旨在为高清摄像头和应用处理器之间提供一个高速串行接口,和dsi(显示串行接口),旨在为应用处理器和显示设备之间提供一个

- Xilinx 7系列FPGA架构之器件配置(二)

FPGA技术实战

FPGA器件架构XinxFPGA硬件设计fpga开发

引言:本文我们介绍下7系列FPGA的配置接口,在进行硬件电路图设计时,这也是我们非常关心的内容,本文主要介绍配置模式的选择、配置管脚定义以及如何选择CFGBVS管脚电压及Bank14/15电压。1.概述Xilinx®7系列设备有五个配置接口。每个配置接口对应一个或多个配置模式和总线宽度,如表1所示。有关接口详细的时序信息,可以参阅相应的7系列FPGA数据手册。配置时序主要与FPGA配置时钟管脚CC

- Xilinx 7系列FPGA架构之器件配置(一)

FPGA技术实战

FPGA器件架构XinxFPGA硬件设计fpga开发

引言:本系列博文描述7系列FPGA配置的技术参考。作为开篇,简要概述了7系列FPGA的配置方法和功能。随后的博文将对每种配置方法和功能进行更详细的描述。本文描述的配置方法和功能适用于所有7系列家族器件,只有少数例外。1.概述Xilinx®7系列FPGA通过将特定于应用程序的配置数据(位流)加载到内存中进行配置。7系列FPGA可以主动从外部非易失性存储设备加载,也可以通过外部智能源(如微处理器、DS

- FPGA器件在线配置方法概述

fpga和matlab

FPGA其他fpga开发FPGA在线配置

目录1.配置电路结构和原理2.ICR控制电路软件3.几种常见的FPGA在线配置方法3.1动态部分重配置(PartialReconfiguration,PR)3.2在系统编程(In-SystemProgramming,ISP)3.3多比特流配置(Multi-BitstreamConfiguration)3.4远程更新与配置3.5使用OpenCL或HLS工具FPGA(Field-Programmabl

- quartus频率计 时钟设置_FPGA021 基于QuartusⅡ数字频率计的设计与仿真

weixin_39876739

quartus频率计时钟设置

摘要随着科技电子领域的发展,可编程逻辑器件,例如CPLD和FPGA的在设计中得到了广泛的应用和普及,FPGA/CPLD的发展使数字设计更加的灵活。这些芯片可以通过软件编程的方式对内部结构进行重构,使它达到相应的功能。这种设计思想改变了传统的数字系统设计理念,促进了EDA技术的迅速发展。数字频率计是一种基本的测量仪器。它被广泛应用与航天、电子、测控等领域。采用等精度频率测量方法具有测量精度保持恒定,

- quartus pin 分配(三)

落雨无风

IC设计fpgafpga开发

quartuspin分配如有需要,可查看quartusUI界面sdc配置(二)上次文章中,说了自己写sdc需要配置的分类点,这次将介绍管脚分配。已打开Quartus软件,导入设计,写好约束下一步,在Quartus软件的菜单栏打开Assignments中的二级菜单PinPlanner打开改界面即可看到选中的fpga型号,管脚图,封装类型等信息。在打开的界面中,大致可分为上下两个部分。上半部分,可分为

- Quartus sdc UI界面设置(二)

落雨无风

IC设计fpgafpga开发

Quartussdc设置根据一配置quartus综合简单流程(一)上次文章中,说了自己写sdc需要配置的分类点,这次将说明在UI界面配置sdc。1.在Quartus软件中,导入verilog设计之后,打开Tools/TimeQuestTimingAnalyzer界面大致分为上下两部分,上半部分左侧显示Report、Tasks,右侧显示欢迎界面;下半部分显示Console和History,此处缺图,

- FPGA随记——赛灵思OOC功能

一口一口吃成大V

FPGA随记fpga开发

在这里,我们简要介绍一下Vivado的OOC(Out-of-Context)综合的概念。对于顶层设计,Vivado使用自顶向下的全局(Global)综合方式,将顶层之下的所有逻辑模块都进行综合,但是设置为OOC方式的模块除外,它们独立于顶层设计而单独综合。通常,在整个设计周期中,顶层设计会被多次修改并综合。但有些子模块在创建完毕之后不会因为顶层设计的修改而被修改,如IP,它们被设置为OOC综合方式

- 如何设计实现完成一个FPGA项目

芯作者

D1:verilog设计D1:VHDL设计fpga开发

设计并完成一个FPGA项目是一个复杂但非常有价值的工程任务。以下是一个详细的步骤指南,帮助你从零开始完成一个FPGA项目。1.项目定义与需求分析确定项目目标:明确项目要实现的功能和性能指标。需求分析:列出所有功能需求、性能需求、接口需求等。可行性分析:评估技术可行性、成本和时间预算。2.硬件选择FPGA芯片选择:根据项目需求选择合适的FPGA芯片(如Xilinx、Intel/Altera、Latt

- 零配置初始化流程就一直过不去_ZYNQ UltraScale+ MPSoc FPGA自学笔记-启动加载配置...

weixin_40009026

零配置初始化流程就一直过不去

前言听说最近秋天的第一杯奶茶挺火的,我得赶紧奋发图强写点东西,好赚点赏钱给妹子买奶茶,各位大佬出手大方点,我怕秋天过去了妹子还没喝上奶茶!言归正传,ZYNQUltraScale+MPSoc的配置过程还是挺复杂的,决定写一篇文章来讲一讲,当然我也是初学,如有错讹请轻轻打左脸。一、配置过程Zynq®UltraScale+™MPSoC同时有PS端和PL端,PS又有两种不同的多核处理器可以运行底层代码或者

- FPGA编程指南: CSU DMA传输

行者..................

fpga开发FPGA

1.将安全流开关配置设置为从DMA源接收,即设置csu.csu_sss_cfg[pcap_sss]为0x5。2.配置并设置CSU_DMA以建立通道和传输,具体编程方法可参考CSUDMA编程部分。-通道类型为DMA_SRC。-设置源地址为位流的地址。-设置大小为以字表示的位流大小。3.等待CSUDMA操作完成,确保源频道的传输已完成。4.清除CSU_DMA中断并确认传输完成,这需要设置csudma.

- Swift初学笔记之Swift基础语法

_迦与迦若

Swift编程语言swiftiosxcode

一、变量声明与oc相比更简洁,编译时的检错机制更完善1、let声明常量,var声明变量varmyVariable=42myVariable=50letmyConstant=422、如果初始化时直接赋值可以不声明类型,swift会自己识别(即类型推断)。反之需要用冒号:声明变量类型letmyString="HelloWorld"print(myString);//;加不加都可以,不会报错letmSt

- FPGA案例小程序

BABA8891

fpga开发小程序

FPGA(Field-ProgrammableGateArray,现场可编程门阵列)的应用广泛,因此存在许多不同领域的案例小程序。以下是一些FPGA案例小程序的示例,涵盖了不同的应用场景:1.串口闭环收发小程序应用场景:工业自动化、通信设备、仪器仪表等。功能描述:该小程序通过FPGA芯片的编程实现串口数据的接收和发送功能,支持9600和115200两种速率。在接收数据时,FPGA通过串行接口接收外

- 电源管理芯片4644关键指标及测试方法

国科安芯

产品fpga开发嵌入式硬件硬件工程

以国科安芯(ANSILIC)推出四通道输出降压微型模块稳压器ASP4644为例,该器件支持多路级联输出最高16A。工程师可以快速设计出满足FPGA、ASIC和微处理器等多种电压和负载电流要求驱动,ASP4644模块稳压器包括DC/DC控制器、电源开关、电感器和补偿组件,采用BGA封装。仅需8个外部陶瓷电容器和4个反馈电阻器就能调节4个可独立地调整并介于0.6V至5.5V的输出。单独的输入引脚使4个

- 牛客Verilog语法刷题Day 1

SAChemAdvance

刷题fpga开发

校验器的输入是由原始数据位和校验位组成对于奇偶校验,若合法编码中奇数位发生了错误,也就是编码中的1变成0或0变成1,则编码中1的个数的奇偶性就发生了变化,从而可以发现错误,但不能检测出是哪些位出错。对于一个设置为50MHz的移位寄存器,把16左移到128,需要()nsA.30B.40C.50D.60本题答案选D,从16到128需要3位,50MHz的时钟为20ns,移动3位则为60ns时间(s)=1

- FPGA(Field-Programmable Gate Array,现场可编程门阵列)开发入门

MAMA6681

fpga开发

FPGA(Field-ProgrammableGateArray,现场可编程门阵列)开发入门是一个系统且深入的过程,涉及到硬件设计、编程语言、开发工具等多个方面。以下是一个简要的FPGA开发入门指南:一、基础知识准备数字电路与逻辑设计:了解数字电路的基本概念,如二进制、逻辑门电路、组合逻辑电路、时序逻辑电路等。熟悉布尔代数和逻辑门的功能及其实现方法。计算机体系架构:掌握CPU、内存、外设、总线等计

- FPGA 编程基础, 赋值操作符, 运算符使用, 条件表达式, 信号操作方法

行者..................

fpga开发

1.**赋值符号**:-**"="**:阻塞赋值,即在`always`模块中该语句会被立即执行。-**""**:大于,如果A>B则结果为TRUE,否则为FALSE。-**">="**:大于等于,如果A>=B则结果为TRUE,否则为FALSE。-**"=="**:等于,如果A==B则结果为TRUE,否则为FALSE。-**"!="**:不等于,如果A!=B则结果为TRUE,否则为FALSE。4.**

- 连续发送多个数据(uart串口RS232协议/verilog详细代码+仿真)

勇敢牛牛(FPGA学习版)

fpga开发嵌入式硬件matlab智能硬件

写在前言以下内容详细源文件,已经上传个人主页资源,需要自取~目录写在前言需求分析UART简介整体架构流程小结需求分析使用串口(rs232协议)间隔1s连续发送16byte的数据。由于每次发送的数据只有8bit,16byte=128bit,所以要发送16帧。UART简介这里实验所使用的参数有:rs232通信协议+9600bps+quartus18.0+modelsim2020异步通信:UART是一种

- zobovision随谈H.265/HEVC编码FPGA实现(一)

zobovision

视频图像编解码FPGAIPfpga开发视频编解码

zobovision随谈H.265/HEVC编码FPGA实现(一)H.265/HEVC出来已有10年,但市场应用难言巅峰,正如古董级的H.264现在仍然大行其道,H.265的全面应用仍有待市场发酵,至少在硬件产品端应用,值得期待。一来H.265相对H.264而言,压缩技术确实要先进不少,不管是理论上还是实际效果方面;二是H.265相对后来者H.266/VVC等而言,实用性更强,性价比更高,产品端的

- (14)时钟专题--->(014)行波时钟

宁静致远dream

FPGA学无止境fpga开发FPGAIC

1.1.1本节目录1)本节目录2)本节引言3)FPGA简介4)行波时钟5)结束语1.1.2本节引言“不积跬步,无以至千里;不积小流,无以成江海。就是说:不积累一步半步的行程,就没有办法达到千里之远;不积累细小的流水,就没有办法汇成江河大海。1.1.3FPGA简介FPGA(FieldProgrammableGateArray)是在PAL、GAL等可编程器件的基础上进一步发展的产物。它是作为专用集成电

- Java实现的基于模板的网页结构化信息精准抽取组件:HtmlExtractor

yangshangchuan

信息抽取HtmlExtractor精准抽取信息采集

HtmlExtractor是一个Java实现的基于模板的网页结构化信息精准抽取组件,本身并不包含爬虫功能,但可被爬虫或其他程序调用以便更精准地对网页结构化信息进行抽取。

HtmlExtractor是为大规模分布式环境设计的,采用主从架构,主节点负责维护抽取规则,从节点向主节点请求抽取规则,当抽取规则发生变化,主节点主动通知从节点,从而能实现抽取规则变化之后的实时动态生效。

如

- java编程思想 -- 多态

百合不是茶

java多态详解

一: 向上转型和向下转型

面向对象中的转型只会发生在有继承关系的子类和父类中(接口的实现也包括在这里)。父类:人 子类:男人向上转型: Person p = new Man() ; //向上转型不需要强制类型转化向下转型: Man man =

- [自动数据处理]稳扎稳打,逐步形成自有ADP系统体系

comsci

dp

对于国内的IT行业来讲,虽然我们已经有了"两弹一星",在局部领域形成了自己独有的技术特征,并初步摆脱了国外的控制...但是前面的路还很长....

首先是我们的自动数据处理系统还无法处理很多高级工程...中等规模的拓扑分析系统也没有完成,更加复杂的

- storm 自定义 日志文件

商人shang

stormclusterlogback

Storm中的日志级级别默认为INFO,并且,日志文件是根据worker号来进行区分的,这样,同一个log文件中的信息不一定是一个业务的,这样就会有以下两个需求出现:

1. 想要进行一些调试信息的输出

2. 调试信息或者业务日志信息想要输出到一些固定的文件中

不要怕,不要烦恼,其实Storm已经提供了这样的支持,可以通过自定义logback 下的 cluster.xml 来输

- Extjs3 SpringMVC使用 @RequestBody 标签问题记录

21jhf

springMVC使用 @RequestBody(required = false) UserVO userInfo

传递json对象数据,往往会出现http 415,400,500等错误,总结一下需要使用ajax提交json数据才行,ajax提交使用proxy,参数为jsonData,不能为params;另外,需要设置Content-type属性为json,代码如下:

(由于使用了父类aaa

- 一些排错方法

文强chu

方法

1、java.lang.IllegalStateException: Class invariant violation

at org.apache.log4j.LogManager.getLoggerRepository(LogManager.java:199)at org.apache.log4j.LogManager.getLogger(LogManager.java:228)

at o

- Swing中文件恢复我觉得很难

小桔子

swing

我那个草了!老大怎么回事,怎么做项目评估的?只会说相信你可以做的,试一下,有的是时间!

用java开发一个图文处理工具,类似word,任意位置插入、拖动、删除图片以及文本等。文本框、流程图等,数据保存数据库,其余可保存pdf格式。ok,姐姐千辛万苦,

- php 文件操作

aichenglong

PHP读取文件写入文件

1 写入文件

@$fp=fopen("$DOCUMENT_ROOT/order.txt", "ab");

if(!$fp){

echo "open file error" ;

exit;

}

$outputstring="date:"." \t tire:".$tire."

- MySQL的btree索引和hash索引的区别

AILIKES

数据结构mysql算法

Hash 索引结构的特殊性,其 检索效率非常高,索引的检索可以一次定位,不像B-Tree 索引需要从根节点到枝节点,最后才能访问到页节点这样多次的IO访问,所以 Hash 索引的查询效率要远高于 B-Tree 索引。

可能很多人又有疑问了,既然 Hash 索引的效率要比 B-Tree 高很多,为什么大家不都用 Hash 索引而还要使用 B-Tree 索引呢

- JAVA的抽象--- 接口 --实现

百合不是茶

抽象 接口 实现接口

//抽象 类 ,方法

//定义一个公共抽象的类 ,并在类中定义一个抽象的方法体

抽象的定义使用abstract

abstract class A 定义一个抽象类 例如:

//定义一个基类

public abstract class A{

//抽象类不能用来实例化,只能用来继承

//

- JS变量作用域实例

bijian1013

作用域

<script>

var scope='hello';

function a(){

console.log(scope); //undefined

var scope='world';

console.log(scope); //world

console.log(b);

- TDD实践(二)

bijian1013

javaTDD

实践题目:分解质因数

Step1:

单元测试:

package com.bijian.study.factor.test;

import java.util.Arrays;

import junit.framework.Assert;

import org.junit.Before;

import org.junit.Test;

import com.bijian.

- [MongoDB学习笔记一]MongoDB主从复制

bit1129

mongodb

MongoDB称为分布式数据库,主要原因是1.基于副本集的数据备份, 2.基于切片的数据扩容。副本集解决数据的读写性能问题,切片解决了MongoDB的数据扩容问题。

事实上,MongoDB提供了主从复制和副本复制两种备份方式,在MongoDB的主从复制和副本复制集群环境中,只有一台作为主服务器,另外一台或者多台服务器作为从服务器。 本文介绍MongoDB的主从复制模式,需要指明

- 【HBase五】Java API操作HBase

bit1129

hbase

import java.io.IOException;

import org.apache.hadoop.conf.Configuration;

import org.apache.hadoop.hbase.HBaseConfiguration;

import org.apache.hadoop.hbase.HColumnDescriptor;

import org.apache.ha

- python调用zabbix api接口实时展示数据

ronin47

zabbix api接口来进行展示。经过思考之后,计划获取如下内容: 1、 获得认证密钥 2、 获取zabbix所有的主机组 3、 获取单个组下的所有主机 4、 获取某个主机下的所有监控项

- jsp取得绝对路径

byalias

绝对路径

在JavaWeb开发中,常使用绝对路径的方式来引入JavaScript和CSS文件,这样可以避免因为目录变动导致引入文件找不到的情况,常用的做法如下:

一、使用${pageContext.request.contextPath}

代码” ${pageContext.request.contextPath}”的作用是取出部署的应用程序名,这样不管如何部署,所用路径都是正确的。

- Java定时任务调度:用ExecutorService取代Timer

bylijinnan

java

《Java并发编程实战》一书提到的用ExecutorService取代Java Timer有几个理由,我认为其中最重要的理由是:

如果TimerTask抛出未检查的异常,Timer将会产生无法预料的行为。Timer线程并不捕获异常,所以 TimerTask抛出的未检查的异常会终止timer线程。这种情况下,Timer也不会再重新恢复线程的执行了;它错误的认为整个Timer都被取消了。此时,已经被

- SQL 优化原则

chicony

sql

一、问题的提出

在应用系统开发初期,由于开发数据库数据比较少,对于查询SQL语句,复杂视图的的编写等体会不出SQL语句各种写法的性能优劣,但是如果将应用系统提交实际应用后,随着数据库中数据的增加,系统的响应速度就成为目前系统需要解决的最主要的问题之一。系统优化中一个很重要的方面就是SQL语句的优化。对于海量数据,劣质SQL语句和优质SQL语句之间的速度差别可以达到上百倍,可见对于一个系统

- java 线程弹球小游戏

CrazyMizzz

java游戏

最近java学到线程,于是做了一个线程弹球的小游戏,不过还没完善

这里是提纲

1.线程弹球游戏实现

1.实现界面需要使用哪些API类

JFrame

JPanel

JButton

FlowLayout

Graphics2D

Thread

Color

ActionListener

ActionEvent

MouseListener

Mouse

- hadoop jps出现process information unavailable提示解决办法

daizj

hadoopjps

hadoop jps出现process information unavailable提示解决办法

jps时出现如下信息:

3019 -- process information unavailable3053 -- process information unavailable2985 -- process information unavailable2917 --

- PHP图片水印缩放类实现

dcj3sjt126com

PHP

<?php

class Image{

private $path;

function __construct($path='./'){

$this->path=rtrim($path,'/').'/';

}

//水印函数,参数:背景图,水印图,位置,前缀,TMD透明度

public function water($b,$l,$pos

- IOS控件学习:UILabel常用属性与用法

dcj3sjt126com

iosUILabel

参考网站:

http://shijue.me/show_text/521c396a8ddf876566000007

http://www.tuicool.com/articles/zquENb

http://blog.csdn.net/a451493485/article/details/9454695

http://wiki.eoe.cn/page/iOS_pptl_artile_281

- 完全手动建立maven骨架

eksliang

javaeclipseWeb

建一个 JAVA 项目 :

mvn archetype:create

-DgroupId=com.demo

-DartifactId=App

[-Dversion=0.0.1-SNAPSHOT]

[-Dpackaging=jar]

建一个 web 项目 :

mvn archetype:create

-DgroupId=com.demo

-DartifactId=web-a

- 配置清单

gengzg

配置

1、修改grub启动的内核版本

vi /boot/grub/grub.conf

将default 0改为1

拷贝mt7601Usta.ko到/lib文件夹

拷贝RT2870STA.dat到 /etc/Wireless/RT2870STA/文件夹

拷贝wifiscan到bin文件夹,chmod 775 /bin/wifiscan

拷贝wifiget.sh到bin文件夹,chm

- Windows端口被占用处理方法

huqiji

windows

以下文章主要以80端口号为例,如果想知道其他的端口号也可以使用该方法..........................1、在windows下如何查看80端口占用情况?是被哪个进程占用?如何终止等. 这里主要是用到windows下的DOS工具,点击"开始"--"运行",输入&

- 开源ckplayer 网页播放器, 跨平台(html5, mobile),flv, f4v, mp4, rtmp协议. webm, ogg, m3u8 !

天梯梦

mobile

CKplayer,其全称为超酷flv播放器,它是一款用于网页上播放视频的软件,支持的格式有:http协议上的flv,f4v,mp4格式,同时支持rtmp视频流格 式播放,此播放器的特点在于用户可以自己定义播放器的风格,诸如播放/暂停按钮,静音按钮,全屏按钮都是以外部图片接口形式调用,用户根据自己的需要制作 出播放器风格所需要使用的各个按钮图片然后替换掉原始风格里相应的图片就可以制作出自己的风格了,

- 简单工厂设计模式

hm4123660

java工厂设计模式简单工厂模式

简单工厂模式(Simple Factory Pattern)属于类的创新型模式,又叫静态工厂方法模式。是通过专门定义一个类来负责创建其他类的实例,被创建的实例通常都具有共同的父类。简单工厂模式是由一个工厂对象决定创建出哪一种产品类的实例。简单工厂模式是工厂模式家族中最简单实用的模式,可以理解为是不同工厂模式的一个特殊实现。

- maven笔记

zhb8015

maven

跳过测试阶段:

mvn package -DskipTests

临时性跳过测试代码的编译:

mvn package -Dmaven.test.skip=true

maven.test.skip同时控制maven-compiler-plugin和maven-surefire-plugin两个插件的行为,即跳过编译,又跳过测试。

指定测试类

mvn test

- 非mapreduce生成Hfile,然后导入hbase当中

Stark_Summer

maphbasereduceHfilepath实例

最近一个群友的boss让研究hbase,让hbase的入库速度达到5w+/s,这可愁死了,4台个人电脑组成的集群,多线程入库调了好久,速度也才1w左右,都没有达到理想的那种速度,然后就想到了这种方式,但是网上多是用mapreduce来实现入库,而现在的需求是实时入库,不生成文件了,所以就只能自己用代码实现了,但是网上查了很多资料都没有查到,最后在一个网友的指引下,看了源码,最后找到了生成Hfile

- jsp web tomcat 编码问题

王新春

tomcatjsppageEncode

今天配置jsp项目在tomcat上,windows上正常,而linux上显示乱码,最后定位原因为tomcat 的server.xml 文件的配置,添加 URIEncoding 属性:

<Connector port="8080" protocol="HTTP/1.1"

connectionTi

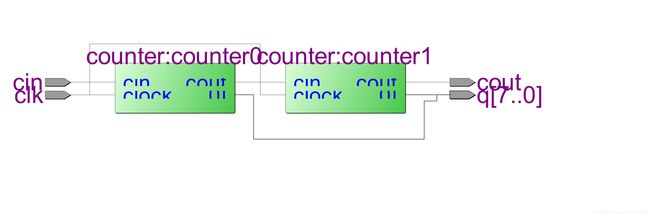

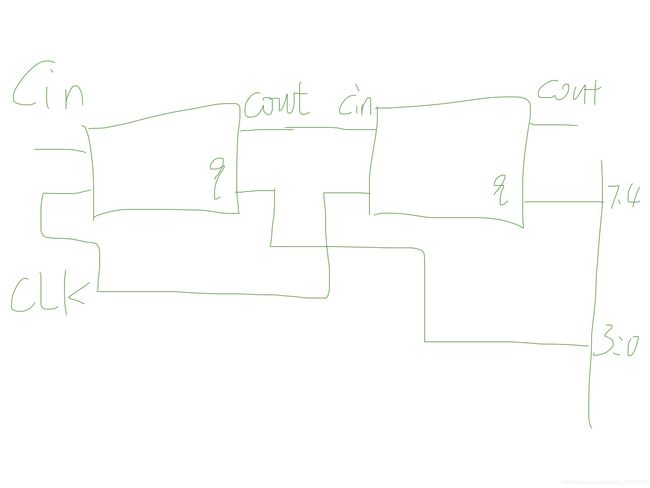

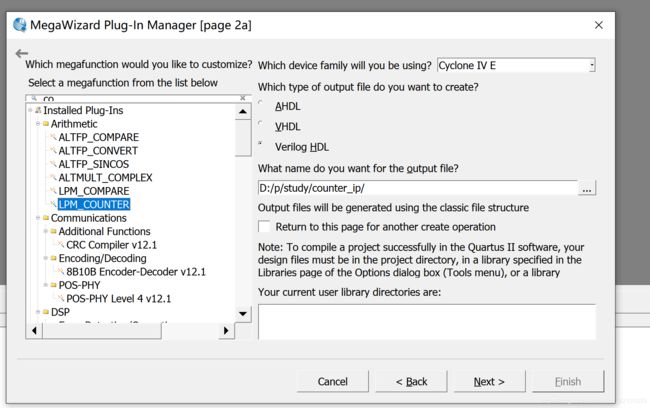

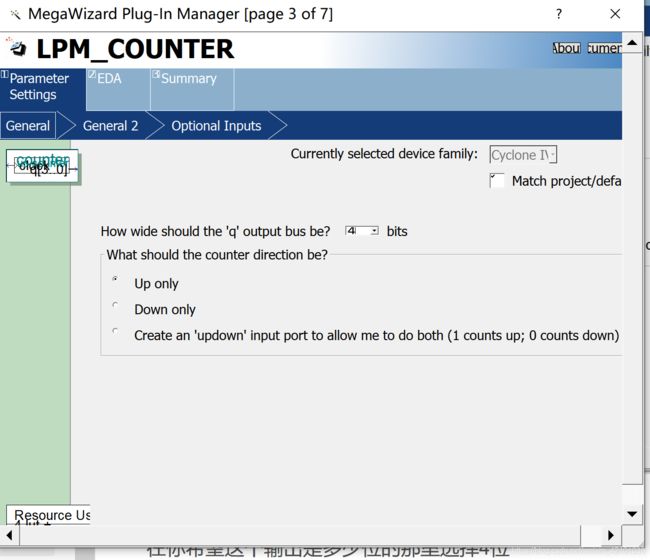

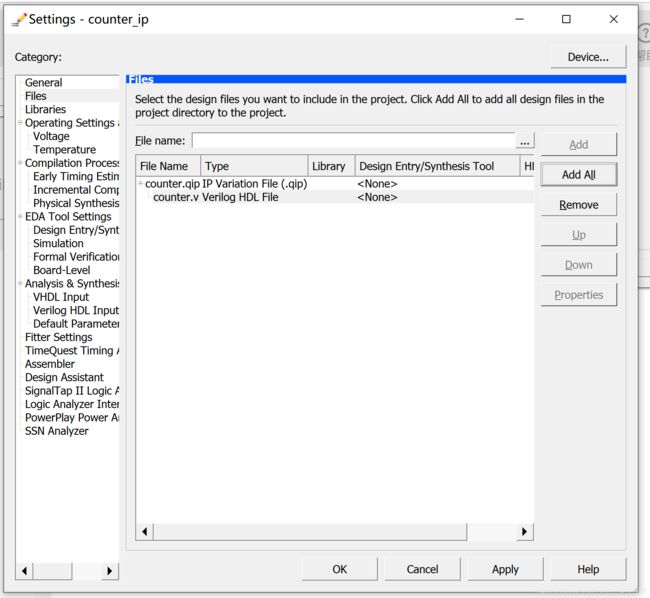

选择Up only,增计数模式。点击next

选择Up only,增计数模式。点击next

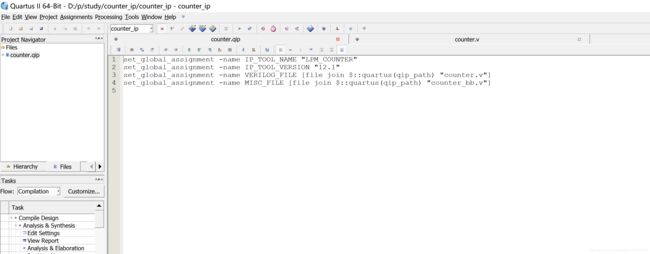

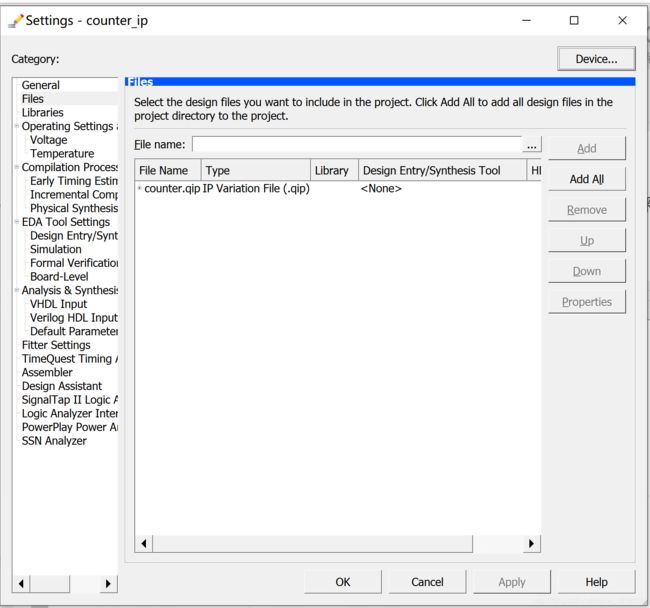

然后就可以看到qip文件已经添加进来了。

然后就可以看到qip文件已经添加进来了。

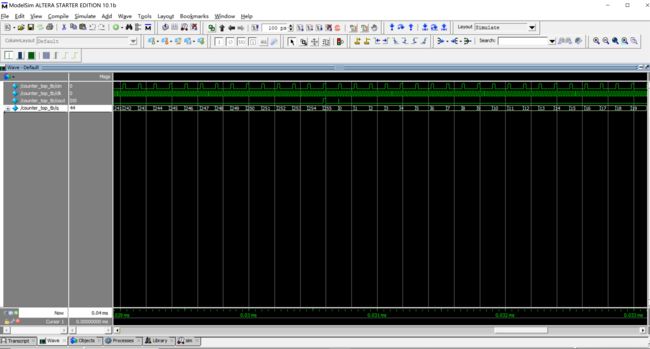

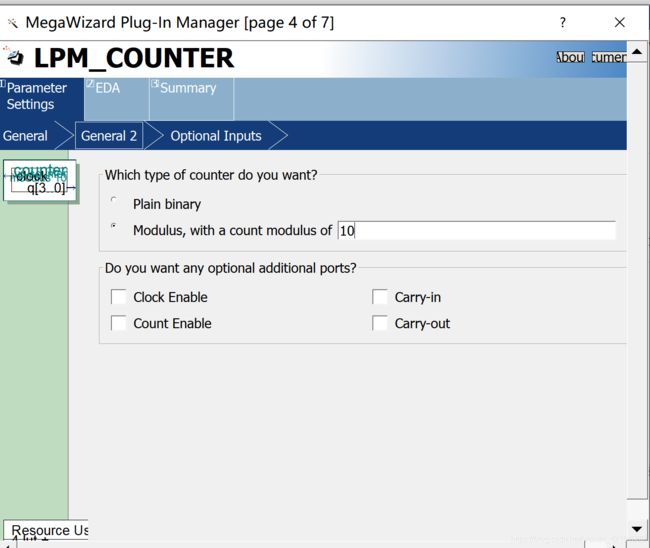

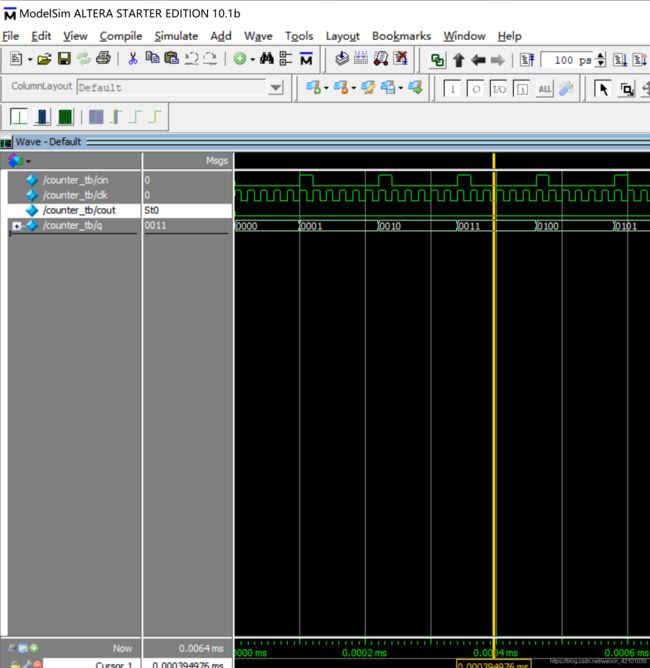

下面试一下八位计数

下面试一下八位计数