nuc970 杂记

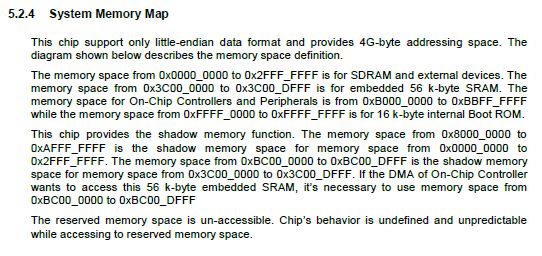

1. 系统内存映射表

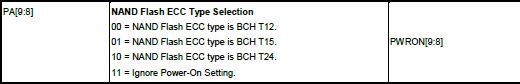

2. 上电前初始化的硬件管脚

注意每个管脚上电时需配置对应的电平该功能才能生效!

3. CPU主频300MHz与264MHz切换

主要修改两个地方,第一个地址0xB0000264修改对应的频率,另个是0xB0001834是对应SDRAM的的延时时间。

打印时钟的源码:

static void print_clock_info(void)

{

int apll_clk, upll_clk, Fvco_clk, sys_clk, cpu_clk, dram_clk, hclk1_clk, pclk;

int reg_value, sys_sel, CPU_N, N, M, P, PCLK_N;

reg_value = readl(REG_CLK_APLLCON);

N = (reg_value&0x7f)+1;

M = ((reg_value>>7)&0x3f) + 1;

P = ((reg_value>>13) & 0x07) + 1;

apll_clk = 12*(N/(M*P));

reg_value = readl(REG_CLK_UPLLCON);

N = (reg_value&0x7f)+1;

M = ((reg_value>>7)&0x3f) + 1;

P = ((reg_value>>13) & 0x07) + 1;

upll_clk = 12*(N/(M*P));

Fvco_clk = 12*(N/M);

reg_value = readl(REG_CLK_DIV0);

sys_sel = (reg_value>>3)&0x03;

if (sys_sel == 2) { //Apll-clk

sys_clk = apll_clk;

} else if (sys_sel == 3) { //Upll-clk

sys_clk = upll_clk;

} else {

sys_clk = 12;

}

sys_clk = sys_clk/((reg_value&0x07)+1);

CPU_N = ((reg_value>>16)&0x0f) + 1;

cpu_clk = sys_clk / CPU_N;

dram_clk = cpu_clk/2;

hclk1_clk = cpu_clk/2;

PCLK_N = (reg_value>>24) & 0x0f;

pclk = hclk1_clk/(PCLK_N+1);

printk(KERN_INFO "xin-clk:12MHz, apll-clk:%dMHz, upll-clk:%dMHz, sys-clk:%dMHz, Fvco_clk:%dMHz, cpu-clk:%dMHz, dram_clk:%dMHz, hclk1_clk:%dMHz, pclk:%dMHz.\n",\

apll_clk, upll_clk, sys_clk, Fvco_clk, cpu_clk, dram_clk, hclk1_clk, pclk);

}输出的调试信息为:

=======================================

Run framware code

CPU: 300MHz, DDR: 150MHz, SYS: 300MHz, PCLK: 75MHz

Parse NuWriter command line

=======================================

xin-clk:12MHz, apll-clk:264MHz, upll-clk:300MHz, sys-clk:300MHz, Fvco_clk:300MHz, cpu-clk:300MHz, dram_clk:150MHz, hclk1_clk:150MHz, pclk:75MHz.

=======================================

Run framware code

CPU: 264MHz, DDR: 132MHz, SYS: 264MHz, PCLK: 66MHz

Parse NuWriter command line

=======================================

xin-clk:12MHz, apll-clk:264MHz, upll-clk:264MHz, sys-clk:264MHz, Fvco_clk:264MHz, cpu-clk:264MHz, dram_clk:132MHz, hclk1_clk:132MHz, pclk:66MHz.

上面更改CPU的主频,只能在packet包烧写时选定主频,这对于后续现场运行的产品是不行的,所以针对上面两个寄存器0xB0000264、0xB0001834可以在系统刚起来时初始化时钟架构的前面对这两个寄存器重新初始化,修改如下源码:

int __init nuc970_init_clocks(void)

{

int i;

#if 1

//300MHz

writel(0xC0000018, REG_CLK_UPLLCON); //CPU时钟由UPLL倍频输出

writel(0x00888820, NUC970_VA_SDIC+0x034); //设置sdram的延时时间

#else

//264MHz

writel(0xC0000015, REG_CLK_UPLLCON);

writel(0x00FFFF20, NUC970_VA_SDIC+0x034);

#endif

// source

clk[xin] = nuc970_clk_fixed("xin", 12000000);

clk[xin32k] = nuc970_clk_fixed("xin32k", 32768);

clk[apll] = nuc970_clk_apll("apll", "xin", REG_CLK_APLLCON);

clk[upll] = nuc970_clk_upll("upll", "xin", REG_CLK_UPLLCON);

......

}经打印的调试信息,可以正常设置cpu主频:

xin-clk:12MHz, apll-clk:264MHz, upll-clk:264MHz, sys-clk:264MHz, Fvco_clk:264MHz, cpu-clk:264MHz, dram_clk:132MHz, hclk1_clk:132MHz, pclk:66MHz.

xin-clk:12MHz, apll-clk:264MHz, upll-clk:300MHz, sys-clk:300MHz, Fvco_clk:300MHz, cpu-clk:300MHz, dram_clk:150MHz, hclk1_clk:150MHz, pclk:75MHz.

为了简化,可将上述代码添加到内核配置单里面,修改如下kconfig文件,

路径:linux-3.10.x-20171019\arch\arm\kconfig

添加如下脚本:

choice

prompt "select cpu frequency"

default ARCH_CPU_300MHZ

config ARCH_CPU_300MHZ

bool "cpu frequency 300MHz"

config ARCH_CPU_264MHZ

bool "cpu frequency 264MHz"

endchoice当执行make menuconfig配置单时出现如下界面:

内核源码修改如下:

int __init nuc970_init_clocks(void)

{

int i;

#ifdef CONFIG_ARCH_CPU_264MHZ

//264MHz

writel(0xC0000015, REG_CLK_UPLLCON); //CPU时钟由UPLL倍频输出

writel(0x00FFFF20, NUC970_VA_SDIC+0x034); //设置sdram的延时时间

printk(KERN_INFO "nuc970_init_clocks: CONFIG_ARCH_CPU_264MHZ\n");

#else

//300MHz

writel(0xC0000018, REG_CLK_UPLLCON); //CPU时钟由UPLL倍频输出

writel(0x00888820, NUC970_VA_SDIC+0x034); //设置sdram的延时时间

printk(KERN_INFO "nuc970_init_clocks: CONFIG_ARCH_CPU_300MHZ\n");

#endif

// source

clk[xin] = nuc970_clk_fixed("xin", 12000000);

clk[xin32k] = nuc970_clk_fixed("xin32k", 32768);

clk[apll] = nuc970_clk_apll("apll", "xin", REG_CLK_APLLCON);

clk[upll] = nuc970_clk_upll("upll", "xin", REG_CLK_UPLLCON);

......

}