Cordic v6.0 IP CORE使用说明

一、前言:

最近打算用Verlog写一个Cordic算法程序,先看看官方的IP CORE的接口设计和所实现的功能作为参考。

如果你使用的是CORDIC V4.0 IP CORE,请参考下面的链接

http://blog.163.com/fantasy_sunny/blog/static/1959182122013113152237210/

二、Cordic v6.0 IP CORE使用说明

1)平台:Vivado2015.4

2)参考资料:CORDIC V6.0 LogiCORE IP Product Guide

3) IP CORE介绍

CORDIC原理希望大家找一本权威的书籍仔细研读,本文不再介绍原理。

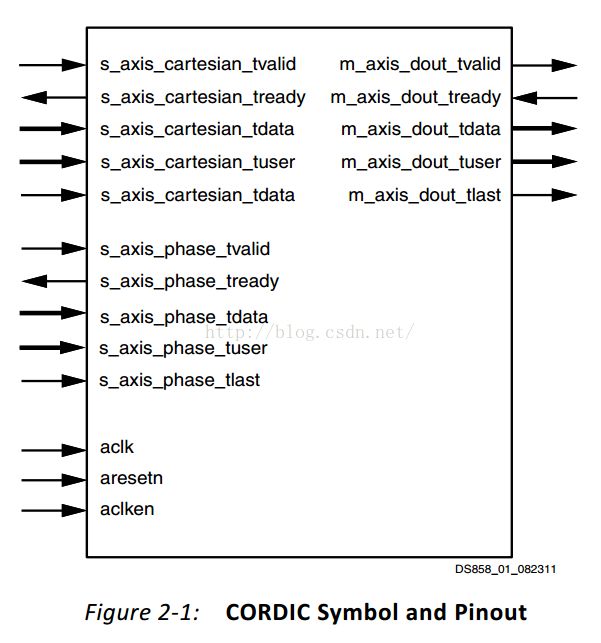

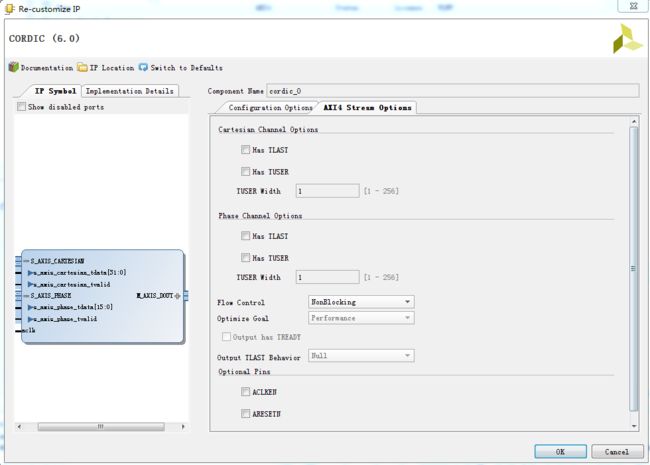

CORDIC V6.0所使用的AXI4-STREAM总线,简称AXIS。AXIS时序非常简单,大家可以在网上搜到很多博 客,这里不妨给出一个链接点击打开链接 ,不再介绍AXIS总线时序。

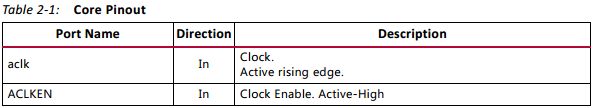

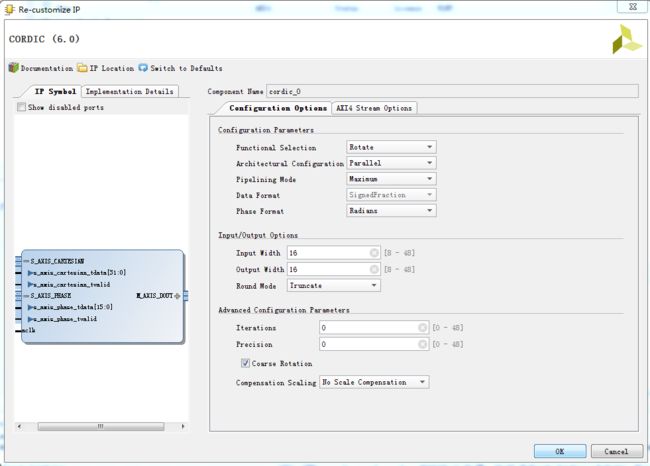

上图 是USER GUIDE上的部分截图,也是我设计自己的IP CORE主要的参考部分,我觉得Xilinx公司把IP CORE的接口都统一为AXI总线是有自己的理由的,一是与ARM公司的合作,ARM+FPGA的发展方向,第二也 是为了用户使用方便,将IP CORE的接口标准化。

我们发现以前的接口是分为X,Y,PHASE的,而现在只是DATA,PHASE,其实是X,Y嵌入到DATA之中了

data和phase的宽度必须为BYTE的整数倍,而且要能容纳X_IN,Y_IN,PHASE_IN

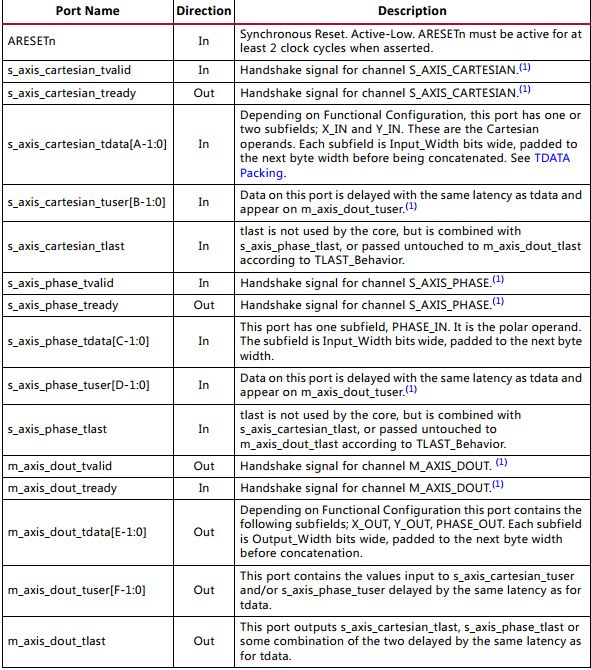

1、Functional Selection:

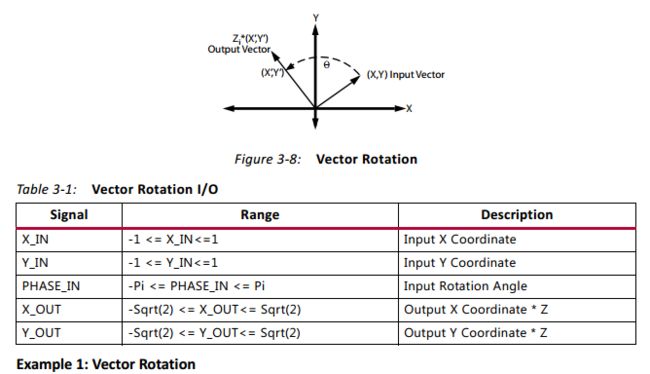

由于CORDIC算法的核心是伪旋转,所以各个功能的输出都会有一定的伸缩,注意比例系数 Z

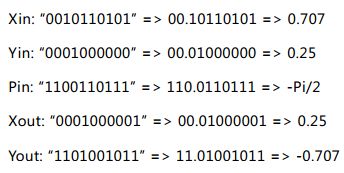

a、Rotate

以下是一个例子

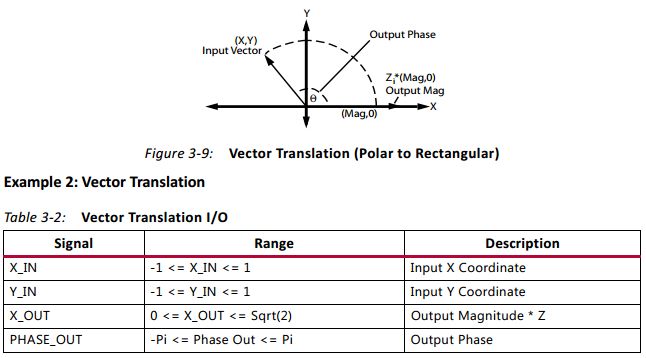

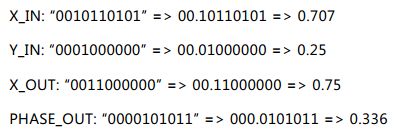

b、Translate

图中括号应该是写错了,我认为应是Rectangular to Polar才对,xy坐标向极坐标的转换,以下是 一个例子。

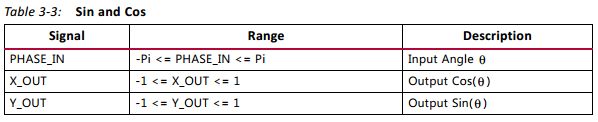

c、sin/cos

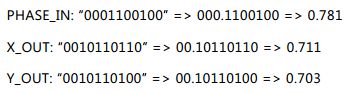

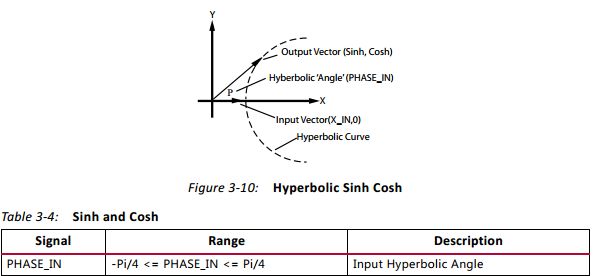

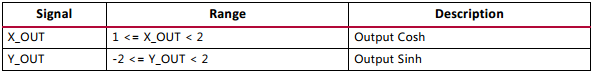

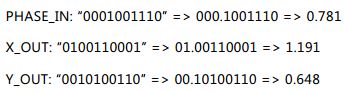

d、sinh/cosh

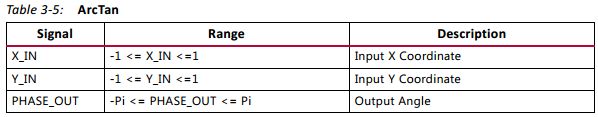

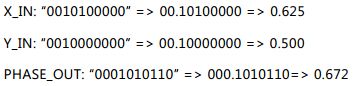

e、arc tan

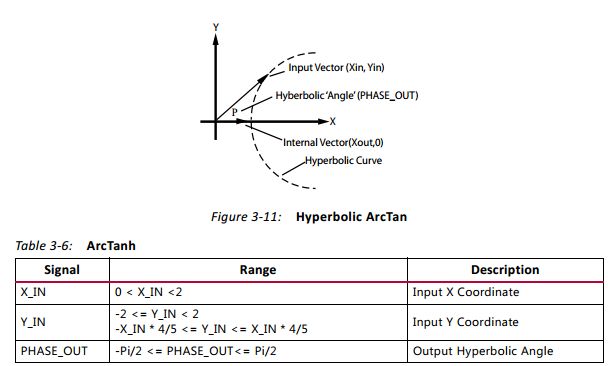

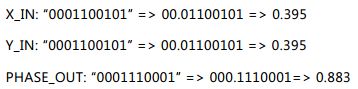

f、 arc tanh

g、square root

2、architectural configuration:

分为 word serial 和 parallel

简单来说,word serial 是为了节省资源,采用了循环的方法,只用一个shift-addsub和一个循环计数器来实 现,parallel则是用多个shift-addsub串连在一起来实现,如果为了提高始终频率和吞吐量,每个shift-addsub之间 可添加reg ,实现pipeline。

最大时钟频率:

parallel with pipeline > word serial > parallel without pipeline

(在xilinx fpga数字信号处理权威指南 何宾,张艳辉 一书CORDIC章节有速率比较,从实现原理上考虑这 种结果理所当然)

3、pipeline mode:结合2中所讲,主要用来提升吞吐量

4、data format:

根据应用场合不同,CORDIC算法的input & output 可以为Cartesian pair(笛卡尔坐标,也就是xy坐标),Polar pair (极坐标)or Scalar form(常量),下面我们一一介绍:

(1)Cartesian Operands and Results

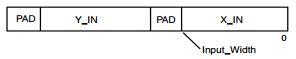

s_axis_cartisian_tdata的subfields是X_IN, Y_IN

s_axis_cartisian_tdata的subfields是X_OUT, Y_OUT

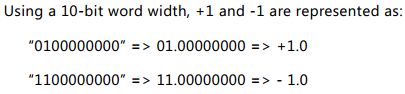

a、在rotate,translate,sin,cos,sinh,cosh,atan 功能中操作数都是如下表示:

并要求: -1 <= input data <= +1

也就是说,使用的是fixed-point,一位符号位,一位整数位,剩下的都是小数位,这种表示方法统称为

Q Numbers Format,具体到上例叫做1QN 或者Fix(N+1)_N, 其中N=(数据位数 - 2),也就是8;

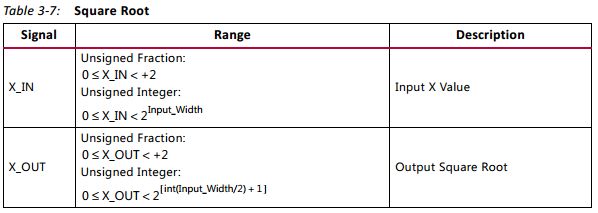

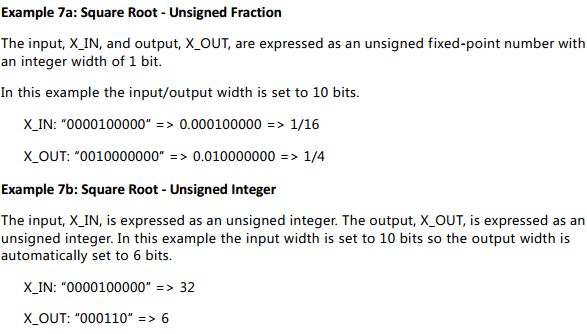

b、 在square root功能中,X_IN, X_OUT都是 unsigned fraction 或者unsigned integer,毕竟开根号的结 果永远不会是负数

此时,X_IN ,X_OUT的整数位为一位,剩下的均为小数位

5、phase format:

表示方法与data format类似,一位符号位,两位整数位,剩下的都是小数位

6、Input/output Options

略

7、Advanced Configuration Parameters

a、Iterations

控制CORDIC算法的迭代次数,用于控制internal add-sub的数量

默认为0,这样迭代次数由输出精度自动决定

b、precision

Configure the internal precision of the add-sub iterations

默认为0,这样内部精度由输出精度要求和迭代次数自动决定

c、coarse rotation

如果没有选中,那么rotation,translation,sin,cos,arc tan的输入输出范围将被限定在(-pi/4~pi/4)

选中则可以扩展到整个圆

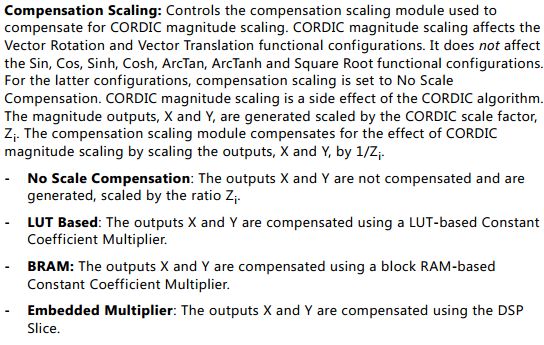

d、compensation scaling