FFT算法8点12位硬件实现 (verilog)

*FFT算法8点12位硬件实现 (verilog) 1

一.功能描述: 1

二.设计结构: 2

三.设计模块介绍 3

1.蝶形运算(第一级) 3

2.矢量角度旋转(W) 4

3.CORDIC 结果处理 除法单元模块 8

4.蝶形运算(第二,三级) 9

5.Vectoring CORDIC 模块 10

6.输出并转串模块 11

四.工程纵览 12

五.功能测试 13

六.工程结束遐想 14*

一.功能描述:

对12位(带符号位)数据进行8点FFT计算

8个12位数据并行输入(懒得写前端的串转并模块,)

8个12位数据并行处理,计算

8个数据串行输出

二.设计结构:

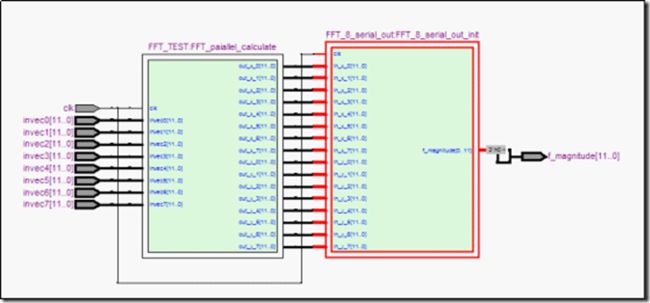

图2.1 FFT并行计算模块

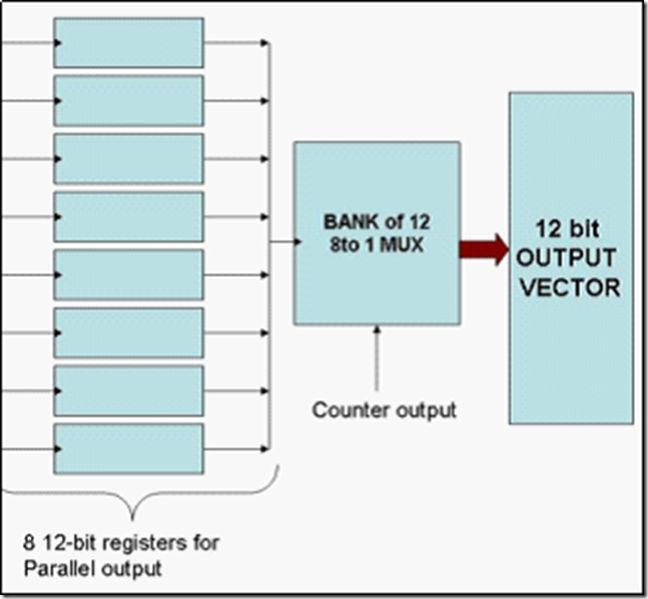

图2.2 输出并转串模块

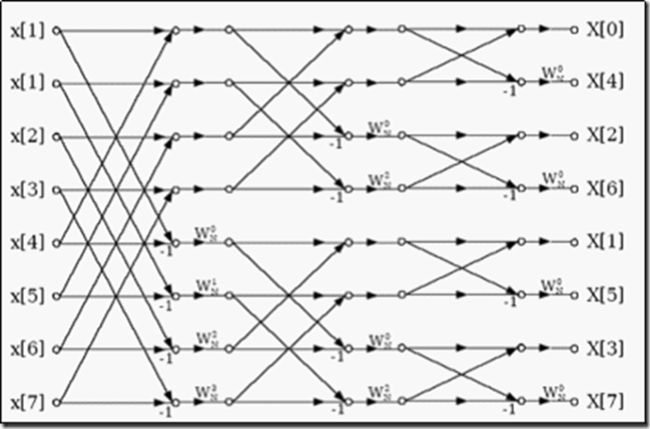

图2.3 FFT算法结构

三.设计模块介绍

按数据流动方向依次介绍

1.1硬件实现方式:

加法:直接运用12位加法器

减法:转换为补码形式后用加法计算

1.2 Verilog代码:

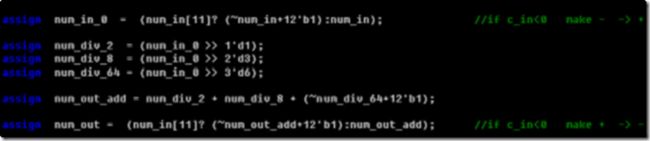

图3.1 第一级蝶形运算 verilog

2.矢量角度旋转(W)

2.1硬件实现方式:

0度:不加操作

-45度:使用Rotation CORDIC算法处理

-90度:使用总线交换,补码转换 方式处理

-135度:预旋转-90度后用Rotation CORDIC算法处理

(Rotation CORDIC 角度输入范围约为-99度到99度,后文有详细介绍)

2.2 Rotation CORDIC算法实现

Rotation CORDIC算法简单介绍

图3.2.1 Rotation CORDI 用于矢量角度旋转

为简化计算将cos()提出

出现两个布尔代数不太喜欢的运算cos与tan,

处理方法:

Tanθ:可见θ为最终要旋转的角。将Tanθ以一系列正或负2-n (此工程中n=7,6,5,4,3,2,1,0)的形式逼近。即每次旋转一个小角度(arctan(2-n))多次旋转后达到θ角

arctan(2-n)的值预先求出 直接由n调用

Cosθ:8个cos的乘积趋向于1/1.647=0.607 在输出端加上除法单元(移位实现1/2 + 1/8 -1/64=0.609)

算法伪代码:

For n=0 to [inf]

If (Z(n) >= 0) then

Z(n + 1) := Z(n) – atan(1/2^n);

Else

Z(n + 1) := Z(n) + atan(1/2^n);

End if;

End for;

If (Z(n) >= 0) then

X(n + 1) := X(n) – (Yn/2^n);

Y(n + 1) := Y(n) + (Xn/2^n);

Z(n + 1) := Z(n) – atan(1/2^n);

Else

X(n + 1) := X(n) + (Yn/2^n);

Y(n + 1) := Y(n) – (Xn/2^n);

Z(n + 1) := Z(n) + atan(1/2^n);

End if;

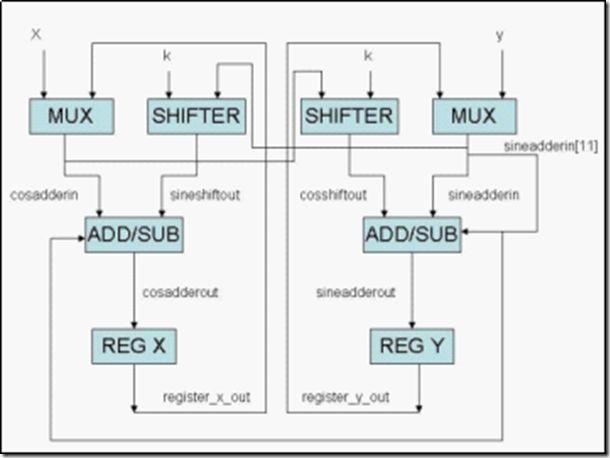

Rotation CORDI 硬件实现

参数:

角度输入范围: 约为-99~99度

实部X:任意12位数(含符号)

虚部Y:任意12位数(含符号)

图3.2.2 Rotation CORDI 硬件实现结构图

SHIFTER 模块:

将负数转为补码形式处理

分三级移位

图3.2.3 SHIFTER 模块 verilog

图3.2.4 SHIFTER 模块 RTL

TABLE 模块:

arctan(2-k)的值预先求出

用12位数表示-180~180的角度

方式如下:

1000_0000_0000 表示-180度

0100_0000_0000 表示90度

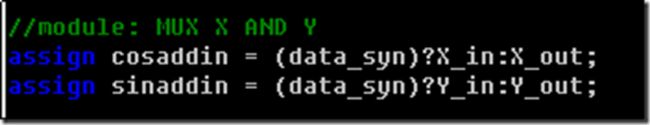

X,Y MUX 与SUB/ADD模块:

原始数据要进行8次迭代,data_syn用于数据同步,确定何时输入原始数据

图3.2.6 MUX 模块 verilog

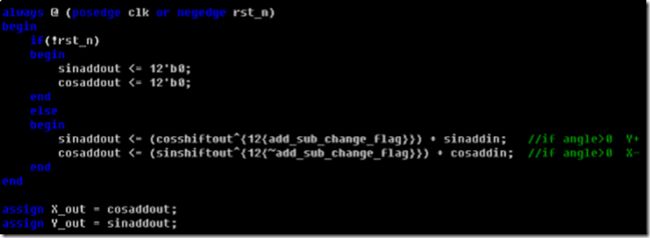

通过异或来确定是否取反(进行减法)

图3.2.7 SUB/ADD 模块 verilog

图3.2.8 MUX , SUB/ADD 模块 verilog

3.CORDIC 结果处理 除法单元模块

8个cos的乘积趋向于1/1.647=0.607 在输出端加上除法单元(移位实现1/2 + 1/8 -1/64=0.609)

图3.3.1 除法单元模块 verilog

4.蝶形运算(第二,三级)

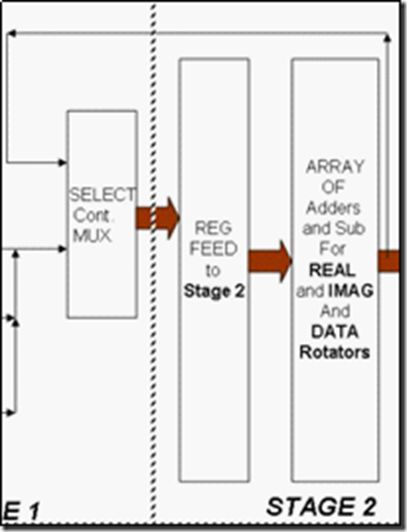

图3.4.1 第二,三级蝶形运算算法结构

4.1硬件实现方式:

将减少资源使用量将第二与第三级运算在同一个硬件模块下循环进行

两级都是蝶形运算只要改变,选择适当的输入,就可在2个CLK下完成这两级运算。

图3.4.2 第二,三级蝶形运算硬件实现结构图

4.2 Verilog代码:

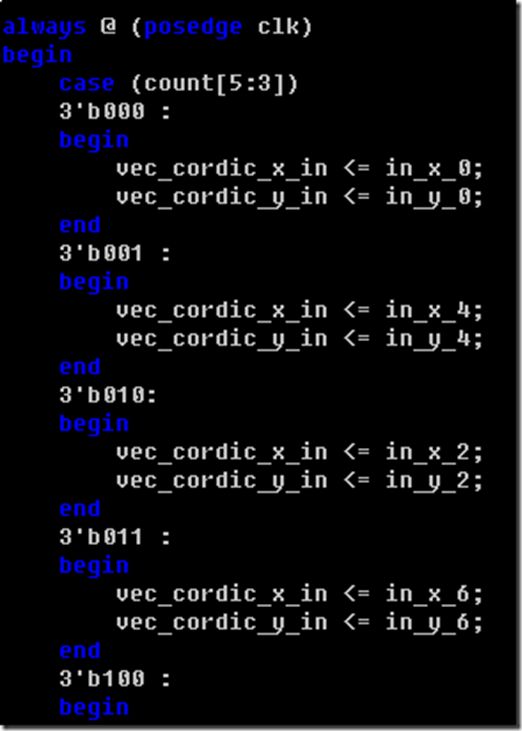

图3.4.3 第二,三级蝶形运算 MUX 模块 verilog

PS:对-90度的矢量旋转直接用总线交换,补码,的形式完成。

5.Vectoring CORDIC 模块

用于对矢量取模

参数:

X:任意大于0的12位数(含符号)

Y:任意12位数(含符号)

5.1算法简述:

通过判断Y的值,使Y趋向于0.使矢量旋转到X轴正方向。此时X坐标就是模值(要经过除法模块除1.647.前面以讲)

图3.5.1 Vectoring CORDI 硬件实现结构图

5.2 Verilog代码:

与 Rotation CORDI 类似 这儿不再重复

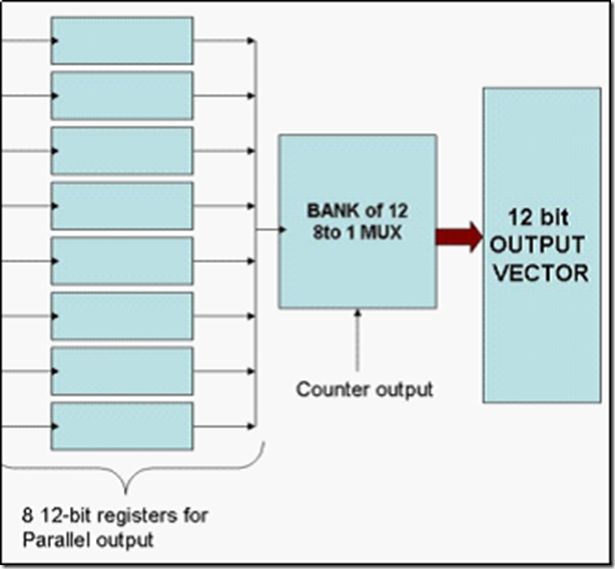

6.输出并转串模块

图3.6.1 并转串结构图

图3.6.2 并转串 verilog 部分

四.工程纵览

图4.1 工程总RTL

图4.2 工程并行计算模块RTL

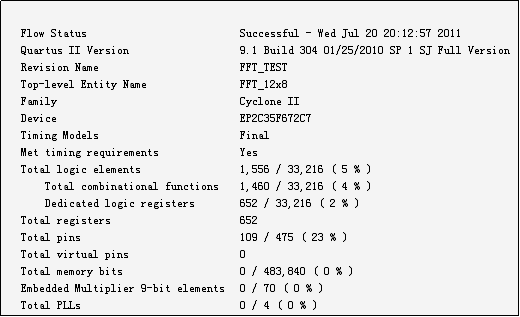

图4.3工程资源利用结果

五.功能测试

为了使硬件定点实现FFT时,输出寄存器能支持比输入信号幅值大的多的数据,在最后有加除8除法器。毕竟我们更关注的是DFT的相对幅值。

![]()

![]()

图5.1 仿真测试结果

六.工程结束遐想

迭代,用二进制数逼近任何数,有点二分法的感觉,又有点向微积分

乘法,除法,与移位的关系,分级运算的妙用

依旧是时间与空间的折中考虑,相互转化

流水下线拆分逻辑,提高速度

时序与逻辑的严密考虑,使时序下的逻辑按我们的下发进行吗,无论是 串行还是并行

循环节省了资源,使处理速度减慢

加减法与补码的关系

细分模块 封装好输入输出 可是调试更方面,,思路更清晰

准确计算每个模块的耗时,便于模块间逻辑的链接