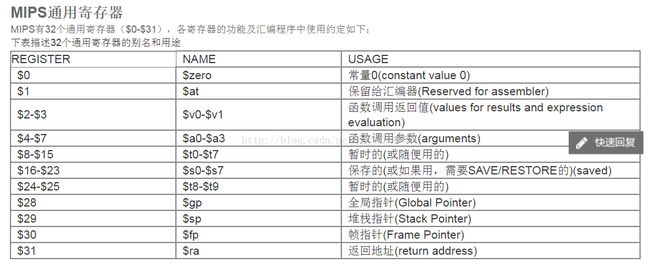

MIPS64寄存器与指令集

MIPS64指令集

需要注意的与32位的区别(32为的w:word ----- 64为的d: double):

运算类:add变成dadd,同理sub/mul/div变成dsub/dmul/ddiv

访存: lw变成ld, sw变成sd

寄存器名: S0/S1… 全部变为r0/r1/… / r31

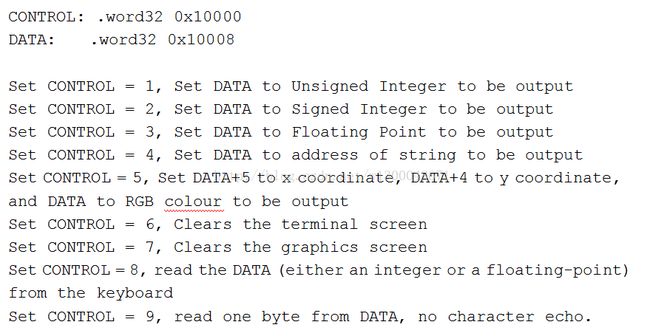

I/O映射表

在符号区域定义的符号的值是当前符号所对应的内存地址,使用的是字节地址

如:

.data

A : .word 32

A的值并不是32,而是其所在的内存位置 0

在.text定义的变量记录的是当前的字地址

.text

Loop: dadd $s0,$s1,$s2

来源:网上资料

64位版本开头以“d”表示,无符号数以“u”结尾,立即数通常以“i”结尾,字节操作以“b”结尾,双字操作以“d”结尾,字操作以“w”结尾

| 序号 |

伪指令 |

功能 |

| 1 |

.data |

start of data segment |

| 2 |

.text |

start of code segment |

| 3 |

.code |

start of code segment (same as .text) |

| 4 |

.org |

start address |

| 5 |

.space |

leave n empty bytes |

| 6 |

.asciiz |

enters zero terminated ascii string |

| 7 |

.ascii |

enter ascii string |

| 8 |

.align |

align to n-byte boundary |

| 9 |

.word |

enters word(s) of data (64-bits) |

| 10 |

.byte |

enter bytes |

| 11 |

.word16 |

enters 16 bit number(s) |

| 12 |

.word32 |

enters 32 bit number(s) |

| 13 |

.double |

enters floating-point number(s) |

| 序号 |

指令 |

功能 |

|

|

访存 |

|

|

|

lb reg,imm(reg) |

load byte |

|

|

lbu reg,imm(reg) |

load byte unsigned |

|

|

lh reg,imm(reg) |

load 16-bit half-word |

|

|

lhu reg,imm(reg) |

load 16-bit half word unsigned |

|

|

lw reg,imm(reg) |

load 32-bit word |

|

|

lwu reg,imm(reg) |

load 32-bit word unsigned |

|

|

ld reg,imm(reg) |

load 64-bit double-word |

|

|

l.s freg,imm(reg) |

load 32-bit floating-point(single FP ) |

|

|

l.d freg,imm(reg) |

load 64-bit floating-point(double FP ) |

|

|

sb reg,imm(reg) |

store byte |

|

|

sh reg,imm(reg) |

store 16-bit half-word |

|

|

sw reg,imm(reg) |

store 32-bit word |

|

|

sd reg,imm(reg) |

store 64-bit double-word |

|

|

s.s freg,imm(reg) |

store 32-bit floating-point |

|

|

s.d freg,imm(reg) |

store 64-bit floating-point |

|

|

|

|

|

|

传送 |

|

|

|

movz r1,r2,r3 |

If(r3==0) r1=r2 |

|

|

movn reg,reg,reg |

move if register not equal to zero |

|

|

|

|

|

|

mov.s freg,freg |

move floating-point(single FP ) |

|

|

mov.d freg,freg |

move floating-point(double FP ) |

|

|

|

|

|

|

mtc1 reg,freg |

move data from integer register to FP register |

|

|

mfc1 reg,freg |

move data from FP register to integer register |

|

|

|

|

|

|

lui reg,imm |

load upper half of register immediate |

|

|

|

|

|

|

算术 |

|

|

|

dadd reg,reg,reg |

add integers |

|

|

daddu reg,reg,reg |

add integers unsigned |

|

|

daddi reg,reg,imm |

add immediate |

|

|

daddui reg,reg,imm |

add immediate unsigned( WinMIPS64格式 ) |

|

|

daddiu reg,reg,imm |

add immediate unsigned( MIPSsim格式 ) |

|

|

add.s freg,freg,freg |

add floating-point(single FP ) |

|

|

add.d freg,freg,freg |

add floating-point(double FP ) |

|

|

dsub reg,reg,reg |

subtract integers |

|

|

dsubu reg,reg,reg |

subtract integers unsigned |

|

|

sub.s freg,freg,freg |

subtract floating-point(single FP ) |

|

|

sub.d freg,freg,freg |

subtract floating-point(double FP ) |

|

|

dmul reg,reg,reg |

signed integer multiplication |

|

|

dmulu reg,reg,reg |

unsigned integer multiplication |

|

|

mul.d freg,freg,freg |

multiply floating-point |

|

|

ddiv reg,reg,reg |

signed integer division |

|

|

ddivu reg,reg,reg |

unsigned integer division |

|

|

div.d freg,freg,freg |

divide floating-point |

|

|

|

|

|

|

逻辑 |

|

|

|

and reg,reg,reg |

logical and |

|

|

andi reg,reg,imm |

logical and immediate |

|

|

or reg,reg,reg |

logical or |

|

|

ori reg,reg,imm |

logical or immediate |

|

|

xor reg,reg,reg |

logical xor |

|

|

xori reg,reg,imm |

exclusive or immediate |

|

|

|

|

|

|

dsll reg,reg,imm |

shift left logical |

|

|

dsllv reg,reg,reg |

shift left logical by variable amount |

|

|

dsrl reg,reg,imm |

shift right logical |

|

|

dsra reg,reg,imm |

shift right arithmetic |

|

|

dsrlv reg,reg,reg |

shift right logical by variable amount |

|

|

dsrav reg,reg,reg |

shift right arithmetic by variable amount |

|

|

|

|

|

|

转换 |

|

|

|

cvt.d.l freg,freg |

convert 64-bit integer to a double FP format |

|

|

cvt.l.d freg,freg |

convert double FP to a 64-bit integer format |

|

|

|

|

|

|

标志 |

|

|

|

slt reg,reg,reg |

set if less than |

|

|

dslt reg,reg,reg |

set if less than( 教材写错,上条为正确格式 ) |

|

|

sltu reg,reg,reg |

set if less than unsigned |

|

|

slti reg,reg,imm |

set if less than immediate |

|

|

sltiu reg,reg,imm |

set if less than immediate unsigned |

|

|

|

|

|

|

c.lt.d freg,freg |

set FP flag if less than |

|

|

c.eq.d freg,freg |

set FP flag if equal to |

|

|

c.le.d freg,freg |

set FP flag if less than or equal to |

|

|

|

|

|

|

跳转 |

|

|

|

j imm |

jump to address (不会保存返回地址) |

|

|

jr reg |

jump to address in register (不会保存返回地址) |

|

|

jal imm |

跳转到imm地址并且将返回地址记录在寄存器ra中(会保存) |

|

|

jalr reg |

jump and link to address in register (会保存) |

|

|

|

|

|

|

beqz reg,imm |

branch if register is equal to zero |

|

|

bnez reg,imm |

branch if register is not equal to zero |

|

|

beq reg,reg,imm |

branch if pair of registers are equal |

|

|

bne reg,reg,imm |

branch if pair of registers are not equal |

|

|

bc1t imm |

branch to address if FP flag is TRUE |

|

|

bc1f imm |

branch to address if FP flag is FALSE |

|

|

|

|

|

|

控制 |

|

|

|

nop |

no operation |

|

|

halt |

stops the program |