【STM32】DAC详解

00. 目录

文章目录

-

- 00. 目录

- 01. DAC简介

- 02. DAC主要特性

- 03. DAC功能说明

- 04. DAC 双通道转换

- 05. DAC寄存器

-

- 5.1 DAC 控制寄存器 (DAC_CR)

- 5.2 DAC 软件触发寄存器 (DAC_SWTRIGR)

- 5.3 DAC 1 通道 12 位右对齐数据保持寄存器 (DAC_DHR12R1)

- 5.4 DAC 1 通道 12 位左对齐数据保持寄存器 (DAC_DHR12L1)

- 5.5 DAC 1 通道 8 位右对齐数据保持寄存器 (DAC_DHR8R1)

- 5.6 DAC 2 通道 12 位右对齐数据保持寄存器 (DAC_DHR12R2)

- 5.7 DAC 2 通道 12 位左对齐数据保持寄存器 (DAC_DHR12L2)

- 5.8 DAC 2 通道 8 位右对齐数据保持寄存器 (DAC_DHR8R2)

- 5.9 双 DAC 12 位右对齐数据保持寄存器 (DAC_DHR12RD)

- 5.10 双 DAC 12 位左对齐数据保持寄存器 (DAC_DHR12LD)

- 5.11 双 DAC 8 位右对齐数据保持寄存器 (DAC_DHR8RD)

- 5.12 DAC 1 通道数据输出寄存器 (DAC_DOR1)

- 5.13 DAC 2 通道数据输出寄存器 (DAC_DOR2)

- 5.14 DAC 状态寄存器 (DAC_SR)

- 06. 附录

- 07. 声明

01. DAC简介

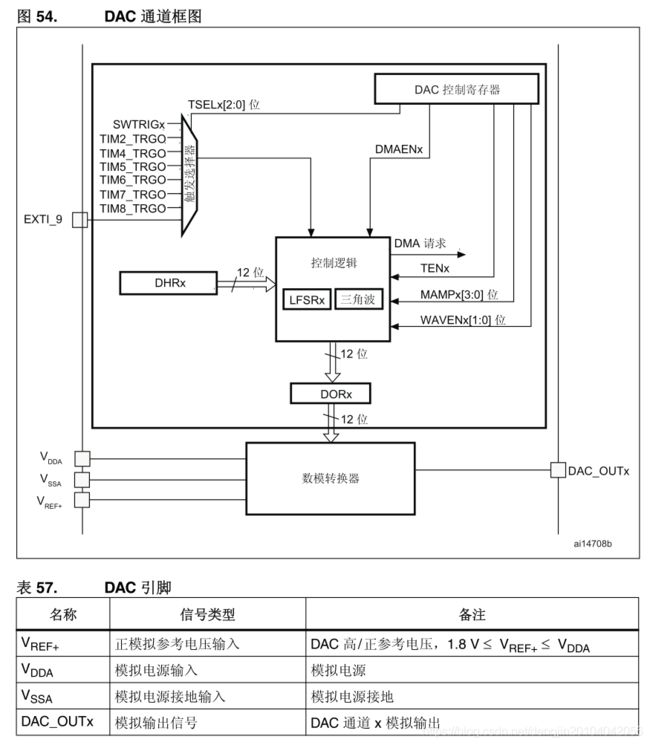

DAC 模块是 12 位电压输出数模转换器。DAC 可以按 8 位或 12 位模式进行配置,并且可与DMA 控制器配合使用。在 12 位模式下,数据可以采用左对齐或右对齐。DAC 有两个输出通道,每个通道各有一个转换器。在 DAC 双通道模式下,每个通道可以单独进行转换;当两个通道组合在一起同步执行更新操作时,也可以同时进行转换。可通过一个输入参考电压引脚 V REF+ (与 ADC 共享)来提高分辨率。

02. DAC主要特性

● 两个 DAC 转换器:各对应一个输出通道

● 12 位模式下数据采用左对齐或右对齐

● 同步更新功能

● 生成噪声波

● 生成三角波

● DAC 双通道单独或同时转换

● 每个通道都具有 DMA 功能

● DMA 下溢错误检测

● 通过外部触发信号进行转换

● 输入参考电压 V REF+

温馨提示

使能 DAC 通道 x 后,相应 GPIO 引脚( PA4 或 PA5 )将自动连接到模拟转换器输出(DAC_OUTx) 。为了避免寄生电流消耗,应首先将 PA4 或 PA5 引脚配置为模拟模式 (AIN) 。

03. DAC功能说明

DAC 通道使能

将 DAC_CR 寄存器中的相应 ENx 位置 1,即可接通对应 DAC 通道。经过一段启动时间t WAKEUP 后,DAC 通道被真正使能。

DAC 输出缓冲器使能

DAC 集成了两个输出缓冲器,可用来降低输出阻抗并在不增加外部运算放大器的情况下直接驱动外部负载。通过 DAC_CR 寄存器中的相应 BOFFx 位,可使能或禁止各 DAC 通道输出缓冲器。

DAC 数据格式

根据所选配置模式,数据必须按如下方式写入指定寄存器:

● 对于 DAC 单通道 x,有三种可能的方式:

— 8 位右对齐:软件必须将数据加载到 DAC_DHR8Rx [7:0] 位(存储到DHRx[11:4] 位)。

— 12 位左对齐:软件必须将数据加载到 DAC_DHR12Lx [15:4] 位(存储到DHRx[11:0] 位)。

— 12 位右对齐:软件必须将数据加载到 DAC_DHR12Rx [11:0] 位(存储到DHRx[11:0] 位)。

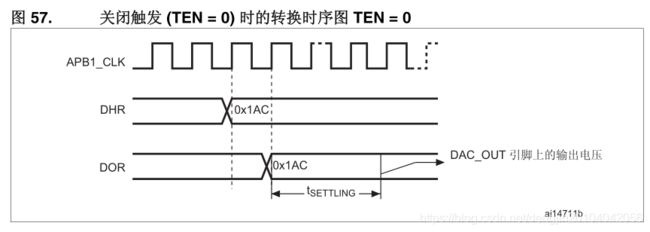

DAC 转换

DAC_DORx 无法直接写入,任何数据都必须通过加载 DAC_DHRx 寄存器(写入DAC_DHR8Rx、DAC_DHR12Lx、DAC_DHR12Rx、DAC_DHR8RD、DAC_DHR12LD 或DAC_DHR12LD)才能传输到 DAC 通道 x。

如果未选择硬件触发(DAC_CR 寄存器中的 TENx 位复位),那么经过一个 APB1 时钟周期后,DAC_DHRx 寄存器中存储的数据将自动转移到 DAC_DORx 寄存器。但是,如果选择硬件触发(置位 DAC_CR 寄存器中的 TENx 位)且触发条件到来,将在三个 APB1 时钟

周期后进行转移。

当 DAC_DORx 加载了 DAC_DHRx 内容时,模拟输出电压将在一段时间 t SETTLING 后可用,具体时间取决于电源电压和模拟输出负载。

DAC 输出电压

经过线性转换后,数字输入会转换为 0 到 V REF+ 之间的输出电压。各DAC通道引脚的模拟输出电压通过以下公式确定:

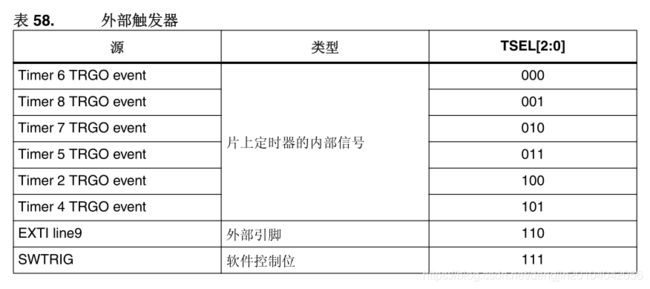

DAC 触发选择

如果 TENx 控制位置 1,可通过外部事件(定时计数器、外部中断线)触发转换。TSELx[2:0]控制位将决定通过 8 个可能事件中的哪一个来触发转换,如 表 58 所示。

DMA 请求

每个 DAC 通道都具有 DMA 功能。两个 DMA 通道用于处理 DAC 通道的 DMA 请求。当 DMAENx 位置 1 时,如果发生外部触发(而不是软件触发),则将产生 DAC DMA 请求。DAC_DHRx 寄存器的值随后转移到 DAC_DORx 寄存器。

在双通道模式下,如果两个 DMAENx 位均置 1,则将产生两个 DMA 请求。如果只需要一个DMA 请求,应仅将相应 DMAENx 位置 1。这样,应用程序可以在双通道模式下通过一个DMA 请求和一个特定 DMA 通道来管理两个 DAC 通道。

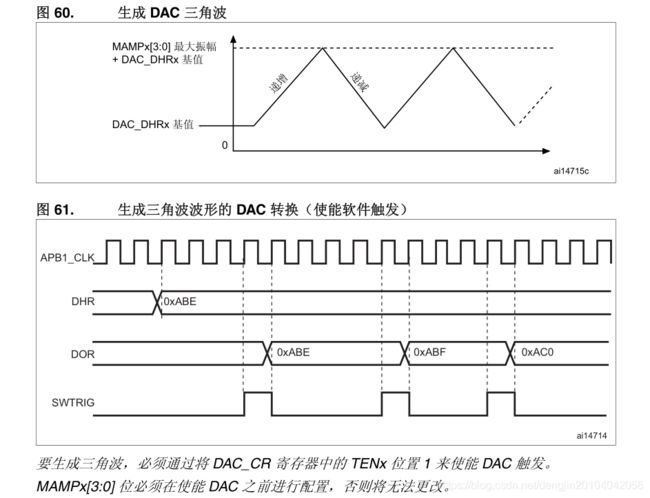

生成三角波

可以在直流电流或慢变信号上叠加一个小幅三角波。将 WAVEx[1:0] 置为“10”即可选择DAC 生成三角波。振幅通过 DAC_CR 寄存器中的 MAMPx[3:0] 位进行配置。每次发生触发事件后,经过三个 APB1 时钟周期,内部三角波计数器将会递增。在不发生溢出的情况下,该计数器的值将与 DAC_DHRx 寄存器内容相加,所得总和将存储到 DAC_DORx 寄存器中。只要小于 MAMPx[3:0] 位定义的最大振幅,三角波计数器就会一直递增。一旦达到配置的振幅,计数器将递减至零,然后再递增,以此类推。可以通过复位 WAVEx[1:0] 位来将三角波产生功能关闭。

04. DAC 双通道转换

为了在同时需要两个 DAC 通道的应用中有效利用总线带宽,DAC 模块实现了三个双寄存器:DHR8RD、DHR12RD 和 DHR12LD。这样,只需一个寄存器访问即可同时驱动两个 DAC通道。

通过两个 DAC 通道和这三个双寄存器可以实现 11 种转换模式。但如果需要,所有这些转换模式也都可以通过单独的 DHRx 寄存器来实现。下面几段内容将介绍所有这些模式。

独立触发(不产生波形)

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为不同的值,以配置不同的触发源

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

DAC 1 通道触发信号到达时,DHR1 寄存器的内容转移到 DAC_DOR1(三个 APB1 时钟周期之后)。

DAC 2 通道触发信号到达时,DHR2 寄存器的内容转移到 DAC_DOR2(三个 APB1 时钟周期之后)。

独立触发(生成单个 LFSR )

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为不同的值,以配置不同的触发源

● 将两个 DAC 通道的 WAVEx[1:0] 设置为“01”,并在 MAMPx[3:0] 位中配置相同的 LFSR掩码值

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DHR12RD、DHR12LD 或 DHR8RD)DAC 通道 1 触发信号到达时,LFSR1 计数器内容(使用相同的掩码)与 DHR1 寄存器内容相加,所得总和转移到 DAC_DOR1 中(三个 APB1 时钟周期之后)。LFSR1 计数器随即更新。DAC 通道 2 触发信号到达时,LFSR2 计数器内容(使用相同的掩码)与 DHR2 寄存器内容相加,所得总和转移到 DAC_DOR2 中(三个 APB1 时钟周期之后)。LFSR2 计数器随即更新。

独立触发(生成不同 LFSR )

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为不同的值,以配置不同的触发源

● 将两个 DAC 通道的 WAVEx[1:0] 设置为“01”,并在 MAMP1[3:0] 和 MAMP2[3:0] 位中设置不同的 LFSR 掩码值

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

DAC 通道 1 触发信号到达时,LFSR1 计数器内容(使用 MAMP1[3:0] 配置的掩码)与 DHR1寄存器内容相加,所得总和转移到 DAC_DOR1 中(三个 APB1 时钟周期之后)。LFSR1 计数器随即更新。

DAC 通道 2 触发信号到达时,LFSR2 计数器内容(使用 MAMP2[3:0] 配置的掩码)与 DHR2寄存器内容相加,所得总和转移到 DAC_DOR2 中(三个 APB1 时钟周期之后)。LFSR2 计数器随即更新。

独立触发(生成单个三角波)

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为不同的值,以配置不同的触发源

● 将两个 DAC 通道的 WAVEx[1:0] 设置为“1x”,并在 MAMPx[3:0] 位中配置相同的最大振幅值

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

DAC 通道 1 触发信号到达时,DAC 1 通道三角波计数器内容(使用相同的三角波振幅)与DHR1 寄存器内容相加,所得总和转移到 DAC_DOR1 中(三个 APB1 时钟周期之后)。

DAC 1 通道三角波计数器随即更新。

DAC 2 通道触发信号到达时,DAC 2 通道三角波计数器内容(使用相同的三角波振幅)与DHR2 寄存器内容相加,所得总和转移到 DAC_DOR2 中(三个 APB1 时钟周期之后)。

DAC 2 通道三角波计数器随即更新。

独立触发(生成不同三角波)

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为不同的值,以配置不同的触发源

● 将两个 DAC 通道的 WAVEx[1:0] 设置为“1x”,并在 MAMP1[3:0] 和 MAMP2[3:0] 位中设置不同的最大振幅值

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

DAC 1 通道触发信号到达时,DAC 1 通道三角波计数器内容(使用 MAMP1[3:0] 配置的三角波振幅)与 DHR1 寄存器内容相加,所得总和转移到 DAC_DOR1 中(三个 APB1 时钟周期之后)。DAC 1 通道三角波计数器随即更新。

DAC 2 通道触发信号到达时,DAC 2 通道三角波计数器内容(使用 MAMP2[3:0] 配置的三角波振幅)与 DHR2 寄存器内容相加,所得总和转移到 DAC_DOR2 中(三个 APB1 时钟周期之后)。DAC 2 通道三角波计数器随即更新。

同步软件启动

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

在此配置中,DHR1 和 DHR2 寄存器内容会在一个 APB1 时钟周期后分别转移到 DAC_DOR1和 DAC_DOR2 中。

同步触发(不产生波形)

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为相同的值,以便为两个 DAC 通道配置相同的触发源

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

当触发信号到达时,DHR1 和 DHR2 寄存器内容将分别转移到 DAC_DOR1 和 DAC_DOR2中(三个 APB1 时钟周期之后)。

同步触发(生成单个 LFSR )

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为相同的值,以便为两个 DAC 通道配置相同的触发源

● 将两个 DAC 通道的 WAVEx[1:0] 设置为“01”,并在 MAMPx[3:0] 位中配置相同的 LFSR掩码值

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DHR12RD、DHR12LD 或 DHR8RD)触发信号到达时,LFSR1 计数器内容(使用相同的掩码)与 DHR1 寄存器内容相加,所得总和转移到 DAC_DOR1 中(三个 APB1 时钟周期之后)。LFSR1 计数器随即更新。同时,LFSR2 计数器内容(使用相同的掩码)与 DHR2 寄存器内容相加,所得总和转移到DAC_DOR2 中(三个 APB1 时钟周期之后)。LFSR2 计数器随即更新。

同步触发(生成不同 LFSR )

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为相同的值,以便为两个 DAC 通道配置相同的触发源

● 将两个 DAC 通道的 WAVEx[1:0] 设置为“01”,并在 MAMP1[3:0] 和 MAMP2[3:0] 位中设置不同的 LFSR 掩码值

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

触发信号到达时,LFSR1 计数器内容(使用 MAMP1[3:0] 配置的掩码)与 DHR1 寄存器内容相加,所得总和转移到 DAC_DOR1 中(三个 APB1 时钟周期之后)。LFSR1 计数器随即更新。

同时,LFSR2 计数器内容(使用 MAMP2[3:0] 配置的掩码)与 DHR2 寄存器内容相加,所得总和转移到 DAC_DOR2 中(三个 APB1 时钟周期之后)。LFSR2 计数器随即更新。

同步触发(生成单个三角波)

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为相同的值,以便为两个 DAC 通道配置相同的触发源

● 将两个 DAC 通道的 WAVEx[1:0] 设置为“1x”,并在 MAMPx[3:0] 位中配置相同的最大振幅值

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

触发信号到达时,DAC 1 通道三角波计数器内容(使用相同的三角波振幅)与 DHR1 寄存器内容相加,所得总和转移到 DAC_DOR1 中(三个 APB1 时钟周期之后)。DAC 1 通道三角波计数器随即更新。

同时,DAC 2 通道三角波计数器内容(使用相同的三角波振幅)与 DHR2 寄存器内容相加,所得总和转移到 DAC_DOR2 中(三个 APB1 时钟周期之后)。DAC 2 通道三角波计数器随即更新。

同步触发(生成不同三角波)

要将 DAC 配置为此转换模式,需要遵循以下顺序:

● 将两个 DAC 通道触发使能位 TEN1 和 TEN2 置 1

● 将 TSEL1[2:0] 和 TSEL2[2:0] 设置为相同的值,以便为两个 DAC 通道配置相同的触发源

● 将两个 DAC 通道的 WAVEx[1:0] 设置为“1x”,并在 MAMP1[3:0] 和 MAMP2[3:0] 位中设置不同的最大振幅值

● 将 DAC 双通道数据加载到所需 DHR 寄存器(DAC_DHR12RD、DAC_DHR12LD 或DAC_DHR8RD)

触发信号到达时,DAC 通道 1 三角波计数器内容(使用 MAMP1[3:0] 配置的三角波振幅)与DHR1 寄存器内容相加,所得总和转移到 DAC_DOR1 中(三个 APB1 时钟周期之后)。DAC通道 1 三角波计数器随即更新。

同时,DAC 通道 2 三角波计数器内容(使用 MAMP2[3:0] 配置的三角波振幅)与 DHR2 寄存器内容相加,所得总和转移到 DAC_DOR2 中(三个 APB1 时钟周期之后)。DAC 通道 2三角波计数器随即更新。

05. DAC寄存器

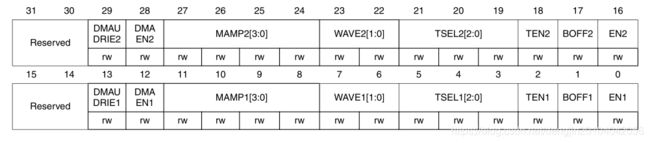

5.1 DAC 控制寄存器 (DAC_CR)

DAC control register

偏移地址:0x00

复位值:0x0000 0000

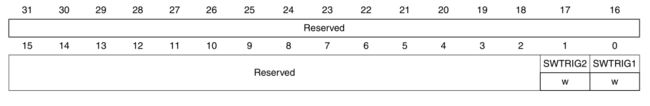

5.2 DAC 软件触发寄存器 (DAC_SWTRIGR)

DAC software trigger register

偏移地址:0x04

复位值:0x0000 0000

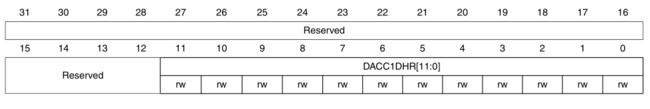

5.3 DAC 1 通道 12 位右对齐数据保持寄存器 (DAC_DHR12R1)

DAC channel1 12-bit right-aligned data holding register

偏移地址:0x08

复位值:0x0000 0000

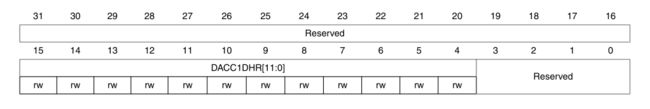

5.4 DAC 1 通道 12 位左对齐数据保持寄存器 (DAC_DHR12L1)

DAC channel1 12-bit left aligned data holding register

偏移地址:0x0C

复位值:0x0000 0000

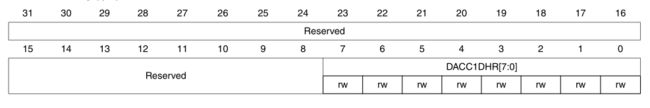

5.5 DAC 1 通道 8 位右对齐数据保持寄存器 (DAC_DHR8R1)

DAC channel1 8-bit right aligned data holding register

偏移地址:0x10

复位值:0x0000 0000

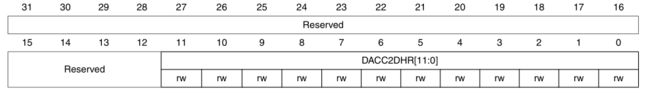

5.6 DAC 2 通道 12 位右对齐数据保持寄存器 (DAC_DHR12R2)

DAC channel2 12-bit right aligned data holding register

偏移地址:0x14

复位值:0x0000 0000

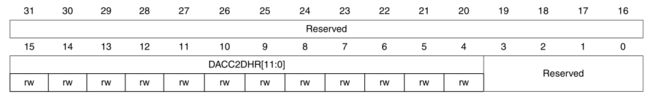

5.7 DAC 2 通道 12 位左对齐数据保持寄存器 (DAC_DHR12L2)

DAC channel2 12-bit left aligned data holding register

偏移地址:0x18

复位值:0x0000 0000

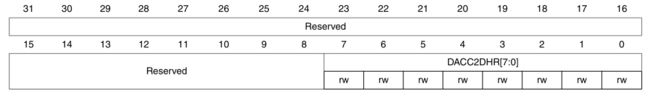

5.8 DAC 2 通道 8 位右对齐数据保持寄存器 (DAC_DHR8R2)

DAC channel2 8-bit right-aligned data holding register

偏移地址:0x1C

复位值:0x0000 0000

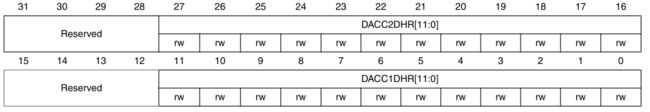

5.9 双 DAC 12 位右对齐数据保持寄存器 (DAC_DHR12RD)

Dual DAC 12-bit right-aligned data holding register

偏移地址:0x20

复位值:0x0000 0000

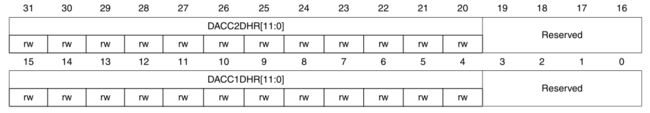

5.10 双 DAC 12 位左对齐数据保持寄存器 (DAC_DHR12LD)

DUAL DAC 12-bit left aligned data holding register

偏移地址:0x24

复位值:0x0000 0000

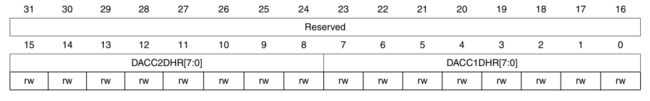

5.11 双 DAC 8 位右对齐数据保持寄存器 (DAC_DHR8RD)

DUAL DAC 8-bit right aligned data holding register

偏移地址:0x28

复位值:0x0000 0000

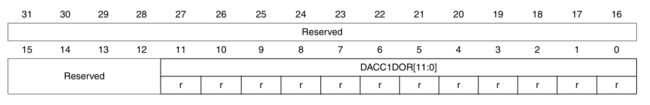

5.12 DAC 1 通道数据输出寄存器 (DAC_DOR1)

DAC channel1 data output register

偏移地址:0x2C

复位值:0x0000 0000

5.13 DAC 2 通道数据输出寄存器 (DAC_DOR2)

DAC channel2 data output register

偏移地址:0x30

复位值:0x0000 0000

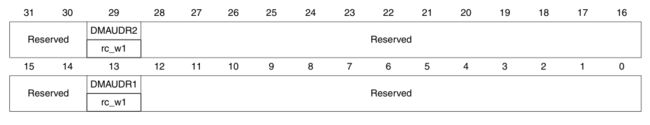

5.14 DAC 状态寄存器 (DAC_SR)

DAC status register

偏移地址:0x34

复位值:0x0000 0000

06. 附录

6.1 【STM32】STM32系列教程汇总

网址:【STM32】STM32系列教程汇总

07. 声明

STM32F4xx英文参考手册