如何自己用SOPC Builder建立一個能在DE2上跑μC/OS-II的Nios II系統? (IC Design) (DE2) (Quartus II) (Nios II) (SOPC Builder) (μC/OS-II)

Abstract

很多人跑DE2本身的範例,都可以上μC/OS-II這個作業系統,但只要自己用SOPC Builder建立的Nios II系統,就無法上μC/OS-II,本文示範如何用SOPC Builder手動打造一個在DE2上能跑uC/OS-II的Nios II系統。

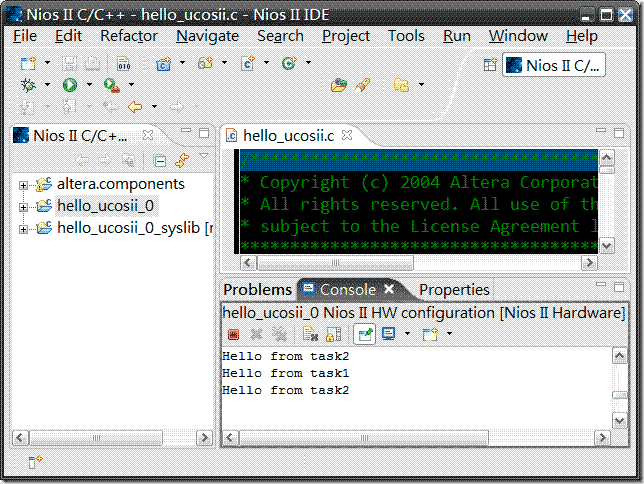

使用環境:Quartus II 7.2 SP1 + Nios II 7.2 SP1 + DE2(Cyclone II EP2C35F627C6) + μC/OS-II

Introduction

本文為我較早期的文章,雖然仍有參考價值,不過並非最佳的設計,建議您一併參考(原創) 如何自己用SOPC Builder建立一個能在DE2上跑μC/OS-II的Nios II系統 (SRAM精簡版)? (SOC) (Quartus II) (Nios II) (SOPC Builder) (μC/OS-II) (DE2)

根據Altera原廠的資料,要讓Nios II上μC/OS-II,只要依照Using MicroC/OS-II RTOS with the Nios II Processor Tutorial這份資料照著做即可,不過這份資料有幾個問題:

1.這份資料是Altera為自己的開發版所寫的,儘管你照著步驟做,仍無法在DE2上執行。

2.他使用了已經編譯好的sof檔,若你主要是用於Nios II軟體的開發,可以採用這種方式。若你可能加入自己設計的硬體元件,則勢必重新編譯sof檔,很多人就是因為這樣而無法上μC/OS-II。

在(原創) 如何成功執行『Using μC/OS-II RTOS with the Nios II Processor Tutorial』? (中級) (IC Design) (Quartus II) (Nios II) (μC/OS-II) 中雖然克服了萬難讓Nios II上μC/OS-II了,不用總有個遺憾,為什麼只能用DE2原廠範例的DE2_SD_Card_Audio.sof呢?為什麼不能自己用SOPC Builder建立一個Nios II系統跑uC/OS-II呢?後來在Terasic原廠網站

http://www.terasic.com/downloads/cd-rom/de2/DE2_System_v1.4b.zip

中發現在這個目錄下

\DE2_demonstrations\SOPC_Builder\Reference_Design\DE2_NIOS\

有Terasic原廠所建議的Nios II硬體設計,經過一番研究後,整理出這份文件。

Solution

要讓Nios II軟體跑在on-chip memory並不是不可能,但DE2最多只能有49K的on-chip memory,所以若要讓軟體能跑,必須動一些最佳化的方式讓軟體盡量的小,在(原創) 如何在DE2執行Checksum Master範例 (中級) (IC Design) (DE2) (Quartus II) (Nios II) (SOPC Builder)用過幾個方式從軟體解決,有興趣的人可以參考,本篇主要是從硬體解決,直接將μC/OS-II跑在SRAM上。

Quartus II

使用Quartus II建立一個全新的project

Step 1:

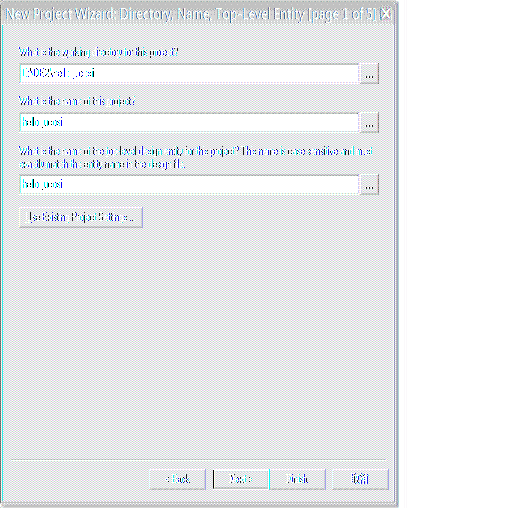

建立一個新project

Step 2:

按Next下一步。

Step 3:

輸入project路徑名稱、project名稱與top-level module名稱,按Next下一步

Step 4:

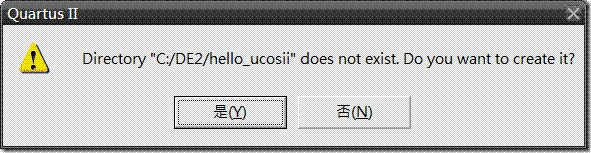

c:/DE2/hello_ucosii目錄尚未建立,是否建立此目錄,按Yes繼續

Step 5:

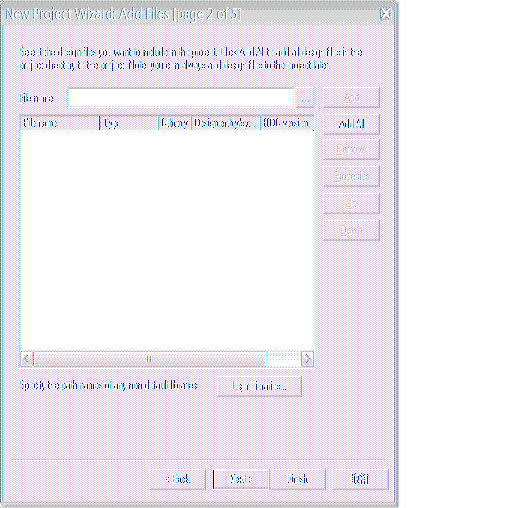

加入既有檔案,由於我們目前沒有任何檔案,所以按Next下一步

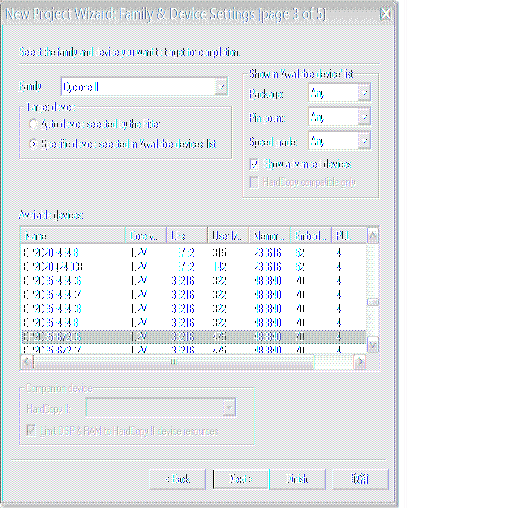

Step 6:

選擇FPGA型號,DE2用的是EP2C35F627C6,按Next下一步

Step 7:

EDA工具設定,不需額外設定,按Next下一步

Step 8:

最後的Summary,按Finish

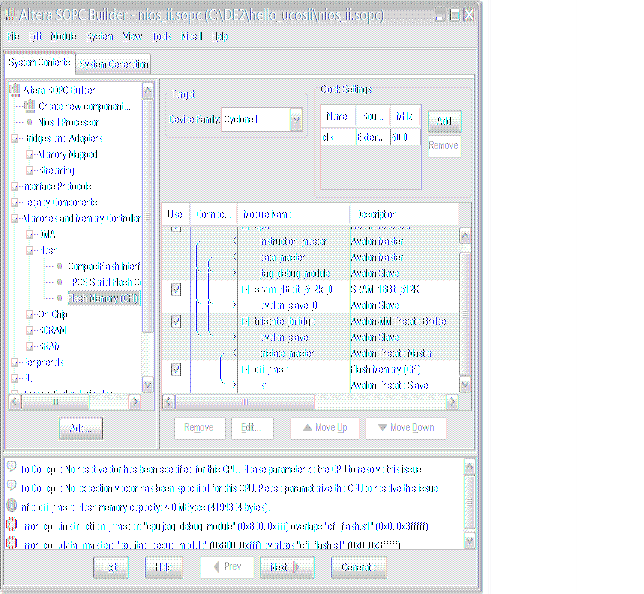

SOPC Builder

使用SOPC Builder建立一個全新的Nios II系統

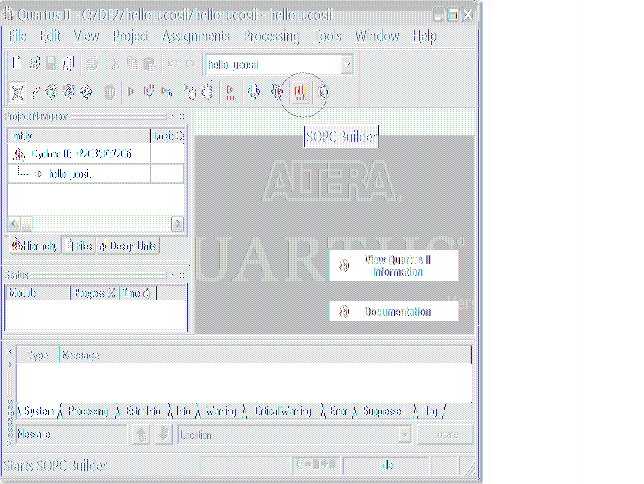

Step 1:

啟動SOPC Builder

Step 2:

輸入System名稱:nios_ii,選擇Verilog

Step 3:

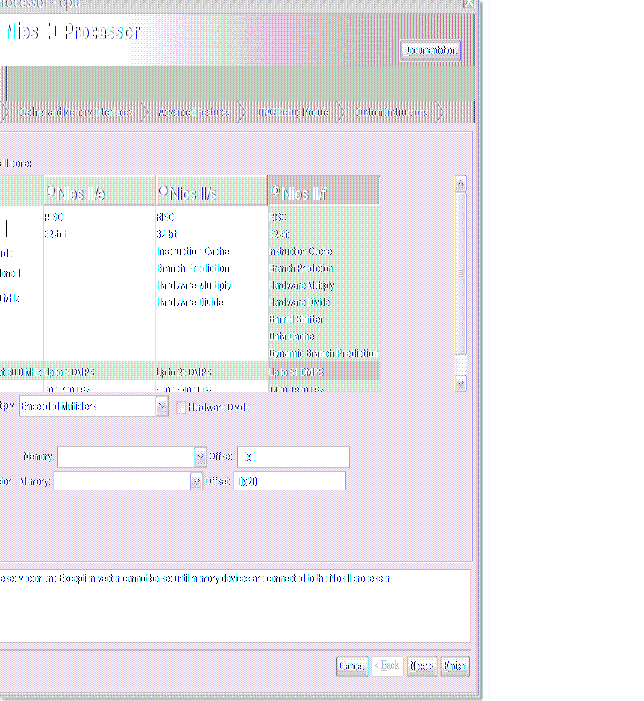

加入Nios II Processor

選擇左側Altera SOPC Builder->Nios II Processor,滑鼠按兩下加入

使用預設的Nios II/f即可,按Finish

Step 4:

加入SRAM

由於我們要將μC/OS-II放在SRAM跑,所以要加入SRAM controller,不過這裡有個值得注意的地方,你不能使用SOPC Builder所附的SRAM controller,必須改用Terasic本身所附的SRAM controller,將SRAM_16Bit_512K.7z下載,或者

http://www.terasic.com/downloads/cd-rom/de2/DE2_System_v1.4b.zip內的\DE2_demonstrations\SOPC_Builder\Component\SRAM_16Bit_512K

目錄複製到

C:\DE2\hello_ucosii\

複製完成後,請重新開啟SOPC Builder,就可以在左側的Altera SOPC Builder->Terasic Technologies Inc\發現SRAM_16Bit_512K這個contoller,滑鼠按兩下加入

Step 5:

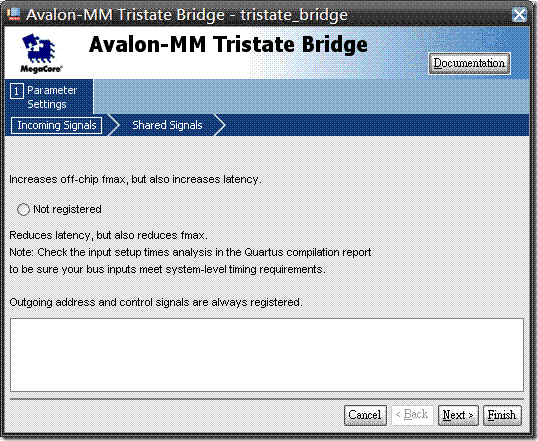

加入Tristate Bridge

由於SRAM需要連接到Tristate Bridge的slave,所以需要加入Tristate Bridge controller,在左側Altera SOPC Builder->Bridges and Adapters->Memoery Mapped下找到Avalon-MM Tristate Bridge,滑鼠按兩下加入

按Finish即可,完成後如下圖出現了一個錯誤訊息:

錯誤訊息表示Tristate Bridge的master必須接到一個slave裝置,所以加上一個Flash Memory controller連上Tristate Bridge。

Step 6:

加入Flash Memory controller

在左側Altera SOPC Builder->Memories and Memory Controllers->Flash下找到Flash Memory(CFI),按兩下加入,將Address Width(bits)改成22

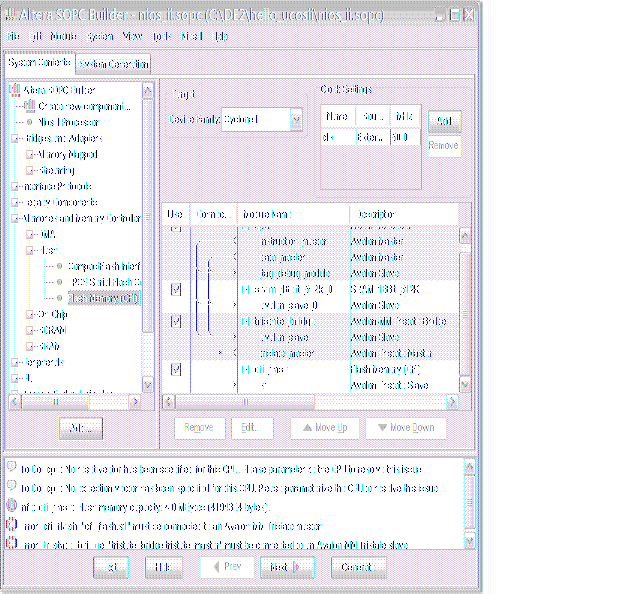

加入後,會如下圖,發現tristate_bridge的tristate_master仍然沒和cfi_flash相接:

所以我們必須手動的接上去

Step 7:

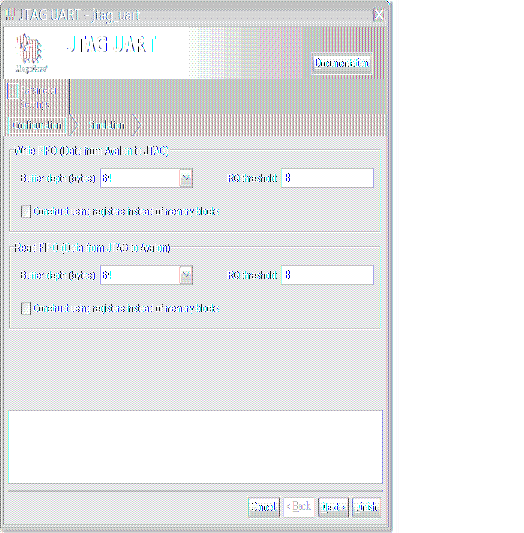

加入JTAG UART

由於我們需在console顯示文字,所以需要加上JTAG UART

在左側Altera SOPC Builder->Interface Protocols->Serial下找到JTAG UART,滑鼠點兩下加入,接受預設值即可,按Finish

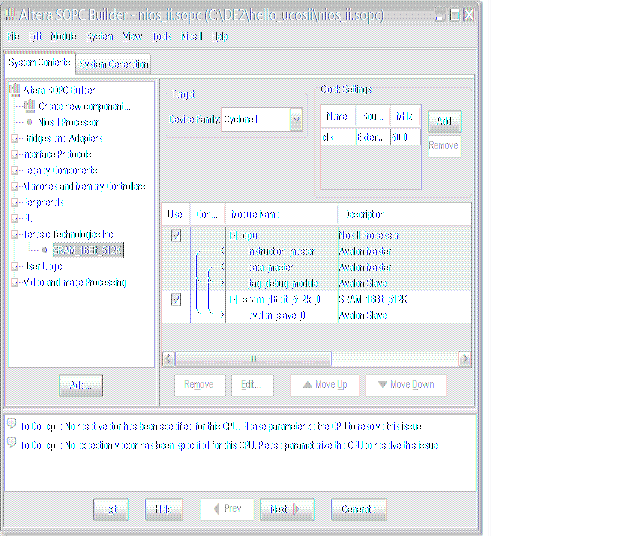

最後如下圖所示

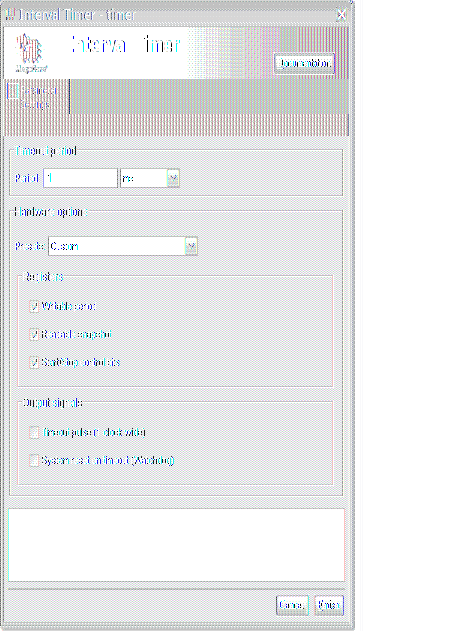

Step 8:

加入Interval Timer

由於μC/OS-II需要用到Internal Timer,所以需要加上。

在左側Altera SOPC Builder->Peripherals->Microcontroller Peripherals下找到Interval Timer,滑鼠點兩下加入,接受預設值即可,按Finish

最後如下圖所示

Step 9:

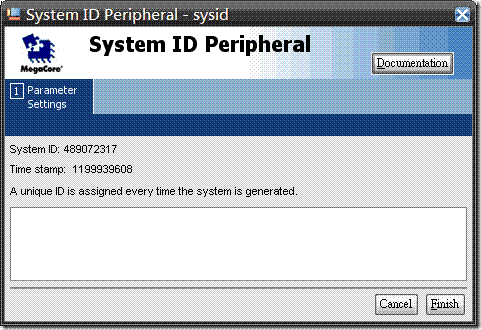

加入System ID Peripheral

System ID Peripheral可以用來辨識硬體,雖然沒有加入也能執行,不過Altera原廠手冊仍建議加入此controller。

在左側Altera SOPC Builder->Peripherals->Debug and Performance下找到System ID Peripheral,滑鼠點兩下加入,接受預設值即可,按Finish

最後如下圖所示

Step 10:

解決錯誤訊息

上圖最下面有幾個錯誤訊息

Error : cpu.instruction_master:

"

cpu.jtag_debug_module

"

(0x800..0xfff) overlaps

"

cfi_flash.s1

"

(0x0..0x3fffff)

Error : cpu.instruction_master:

"

cpu.jtag_debug_module

"

(0x800..0xfff) overlaps

"

cfi_flash.s1

"

(0x0..0x3fffff) Error : cpu.data_master:

"

cpu.jtag_debug_module

"

(0x800..0xfff) overlaps

"

cfi_flash.s1

"

(0x0..0x3fffff)

Error : cpu.data_master:

"

cpu.jtag_debug_module

"

(0x800..0xfff) overlaps

"

cfi_flash.s1

"

(0x0..0x3fffff) Error : cpu.d_irq:Interrupt number conflict(jtag_uart

,

timer.irg) on

0

Error : cpu.d_irq:Interrupt number conflict(jtag_uart

,

timer.irg) on

0

在

Error : cpu.instruction_master:

"

cpu.jtag_debug_module

"

(0x800..0xfff) overlaps

"

cfi_flash.s1

"

(0x0..0x3fffff)

Error : cpu.instruction_master:

"

cpu.jtag_debug_module

"

(0x800..0xfff) overlaps

"

cfi_flash.s1

"

(0x0..0x3fffff)

點兩下,將Reset Vector選擇cfi_flash,Exception Vector選擇sram_16bit_512k_0,按Finish完成

Step 11:

重新分配Base Address

Menu的System->Auto-Assign Base Address

Step 12:

重新分配IRQ

Menu的System->Auto-Assign IRQs

Step 13:

新增Clock Settings

將原本clk改成100.0 Mhz

另外加上clk_50為50.0 Mhz

至此,一個能跑μC/OS-II最小的Nios II系統已經完成,而且是我們DIY用SOPC Builder完成的,最後完成圖如下。

最後按下Generate開始產生硬體,詢問是否儲存,按Save

需要一些時間,完全看你CPU速度而定。

Quartus II Top Module

至此我們還缺Quartus II的Top Module,建立一個新的Verilog檔,名為hello_ucosii.v

hello_ucosii.v

module hello_ucosii (

module hello_ucosii (2

//////////////////// Clock Input ////////////////////

//////////////////// Clock Input ////////////////////

3

CLOCK_27,

//

On Board 27 MHz

CLOCK_27,

//

On Board 27 MHz

4

CLOCK_50,

//

On Board 50 MHz

CLOCK_50,

//

On Board 50 MHz

5

EXT_CLOCK,

//

External Clock

EXT_CLOCK,

//

External Clock

6

//////////////////// Push Button ////////////////////

//////////////////// Push Button ////////////////////

7

KEY,

//

Pushbutton[3:0]

KEY,

//

Pushbutton[3:0]

8

//////////////////// Flash Interface ////////////////

//////////////////// Flash Interface ////////////////

9

FL_DQ,

//

FLASH Data bus 8 Bits

FL_DQ,

//

FLASH Data bus 8 Bits

10

FL_ADDR,

//

FLASH Address bus 20 Bits

FL_ADDR,

//

FLASH Address bus 20 Bits

11

FL_WE_N,

//

FLASH Write Enable

FL_WE_N,

//

FLASH Write Enable

12

FL_RST_N,

//

FLASH Reset

FL_RST_N,

//

FLASH Reset

13

FL_OE_N,

//

FLASH Output Enable

FL_OE_N,

//

FLASH Output Enable

14

FL_CE_N,

//

FLASH Chip Enable

FL_CE_N,

//

FLASH Chip Enable

15

//////////////////// SRAM Interface ////////////////

//////////////////// SRAM Interface ////////////////

16

SRAM_DQ,

//

SRAM Data bus 16 Bits

SRAM_DQ,

//

SRAM Data bus 16 Bits

17

SRAM_ADDR,

//

SRAM Address bus 18 Bits

SRAM_ADDR,

//

SRAM Address bus 18 Bits

18

SRAM_UB_N,

//

SRAM High-byte Data Mask

SRAM_UB_N,

//

SRAM High-byte Data Mask

19

SRAM_LB_N,

//

SRAM Low-byte Data Mask

SRAM_LB_N,

//

SRAM Low-byte Data Mask

20

SRAM_WE_N,

//

SRAM Write Enable

SRAM_WE_N,

//

SRAM Write Enable

21

SRAM_CE_N,

//

SRAM Chip Enable

SRAM_CE_N,

//

SRAM Chip Enable

22

SRAM_OE_N

//

SRAM Output Enable

SRAM_OE_N

//

SRAM Output Enable

23

);

);24

25

//////////////////////// Clock Input ////////////////////////

//////////////////////// Clock Input ////////////////////////

26

input CLOCK_27;

//

On Board 27 MHz

input CLOCK_27;

//

On Board 27 MHz

27

input CLOCK_50;

//

On Board 50 MHz

input CLOCK_50;

//

On Board 50 MHz

28

input EXT_CLOCK;

//

External Clock

input EXT_CLOCK;

//

External Clock

29

//////////////////////// Push Button ////////////////////////

//////////////////////// Push Button ////////////////////////

30

input [

3

:

0

] KEY;

//

Pushbutton[3:0]

input [

3

:

0

] KEY;

//

Pushbutton[3:0]

31

32

//////////////////////// Flash Interface ////////////////////////

//////////////////////// Flash Interface ////////////////////////

33

inout [

7

:

0

] FL_DQ;

//

FLASH Data bus 8 Bits

inout [

7

:

0

] FL_DQ;

//

FLASH Data bus 8 Bits

34

output [

21

:

0

] FL_ADDR;

//

FLASH Address bus 22 Bits

output [

21

:

0

] FL_ADDR;

//

FLASH Address bus 22 Bits

35

output FL_WE_N;

//

FLASH Write Enable

output FL_WE_N;

//

FLASH Write Enable

36

output FL_RST_N;

//

FLASH Reset

output FL_RST_N;

//

FLASH Reset

37

output FL_OE_N;

//

FLASH Output Enable

output FL_OE_N;

//

FLASH Output Enable

38

output FL_CE_N;

//

FLASH Chip Enable

output FL_CE_N;

//

FLASH Chip Enable

39

//////////////////////// SRAM Interface ////////////////////////

//////////////////////// SRAM Interface ////////////////////////

40

inout [

15

:

0

] SRAM_DQ;

//

SRAM Data bus 16 Bits

inout [

15

:

0

] SRAM_DQ;

//

SRAM Data bus 16 Bits

41

output [

17

:

0

] SRAM_ADDR;

//

SRAM Address bus 18 Bits

output [

17

:

0

] SRAM_ADDR;

//

SRAM Address bus 18 Bits

42

output SRAM_UB_N;

//

SRAM Low-byte Data Mask

output SRAM_UB_N;

//

SRAM Low-byte Data Mask

43

output SRAM_LB_N;

//

SRAM High-byte Data Mask

output SRAM_LB_N;

//

SRAM High-byte Data Mask

44

output SRAM_WE_N;

//

SRAM Write Enable

output SRAM_WE_N;

//

SRAM Write Enable

45

output SRAM_CE_N;

//

SRAM Chip Enable

output SRAM_CE_N;

//

SRAM Chip Enable

46

output SRAM_OE_N;

//

SRAM Output Enable

output SRAM_OE_N;

//

SRAM Output Enable

47

48

wire CPU_CLK;

wire CPU_CLK;49

wire CPU_RESET;

wire CPU_RESET;50

wire CLK_18_4;

wire CLK_18_4;51

wire CLK_25;

wire CLK_25;52

53

//

Flash

//

Flash

54

assign FL_RST_N

=

1

'

b1;

assign FL_RST_N

=

1

'

b1;

55

56

Reset_Delay delay1 (.iRST(KEY[

0

]),.iCLK(CLOCK_50),.oRESET(CPU_RESET));

Reset_Delay delay1 (.iRST(KEY[

0

]),.iCLK(CLOCK_50),.oRESET(CPU_RESET));57

58

SDRAM_PLL PLL1 (.inclk0(CLOCK_50),.c0(DRAM_CLK),.c1(CPU_CLK),.c2(CLK_25));

SDRAM_PLL PLL1 (.inclk0(CLOCK_50),.c0(DRAM_CLK),.c1(CPU_CLK),.c2(CLK_25));59

60

nios_ii u0 (

nios_ii u0 (61

//

1) global signals:

//

1) global signals:

62

.clk(CPU_CLK),

.clk(CPU_CLK),63

.reset_n(CPU_RESET),

.reset_n(CPU_RESET),64

65

//

the_sram_0

//

the_sram_0

66

.SRAM_ADDR_from_the_sram_16bit_512k_0(SRAM_ADDR),

.SRAM_ADDR_from_the_sram_16bit_512k_0(SRAM_ADDR),67

.SRAM_CE_N_from_the_sram_16bit_512k_0(SRAM_CE_N),

.SRAM_CE_N_from_the_sram_16bit_512k_0(SRAM_CE_N),68

.SRAM_DQ_to_and_from_the_sram_16bit_512k_0(SRAM_DQ),

.SRAM_DQ_to_and_from_the_sram_16bit_512k_0(SRAM_DQ),69

.SRAM_LB_N_from_the_sram_16bit_512k_0(SRAM_LB_N),

.SRAM_LB_N_from_the_sram_16bit_512k_0(SRAM_LB_N),70

.SRAM_OE_N_from_the_sram_16bit_512k_0(SRAM_OE_N),

.SRAM_OE_N_from_the_sram_16bit_512k_0(SRAM_OE_N),71

.SRAM_UB_N_from_the_sram_16bit_512k_0(SRAM_UB_N),

.SRAM_UB_N_from_the_sram_16bit_512k_0(SRAM_UB_N),72

.SRAM_WE_N_from_the_sram_16bit_512k_0(SRAM_WE_N),

.SRAM_WE_N_from_the_sram_16bit_512k_0(SRAM_WE_N),73

74

//

the_tri_state_bridge_0_avalon_slave

//

the_tri_state_bridge_0_avalon_slave

75

.select_n_to_the_cfi_flash(FL_CE_N),

.select_n_to_the_cfi_flash(FL_CE_N),76

.address_to_the_cfi_flash(FL_ADDR),

.address_to_the_cfi_flash(FL_ADDR),77

.data_to_and_from_the_cfi_flash(FL_DQ),

.data_to_and_from_the_cfi_flash(FL_DQ),78

.read_n_to_the_cfi_flash(FL_OE_N),

.read_n_to_the_cfi_flash(FL_OE_N),79

.write_n_to_the_cfi_flash(FL_WE_N)

.write_n_to_the_cfi_flash(FL_WE_N)80

);

);81

82

endmodule

endmodule

56行的Reset_Dealy module和SDRAM_PLL module,我們須自己建立。

Reset_Delay.v

module Reset_Delay(iRST,iCLK,oRESET);

module Reset_Delay(iRST,iCLK,oRESET);2

input iCLK;

input iCLK;3

input iRST;

input iRST;4

output reg oRESET;

output reg oRESET;5

reg [

23

:

0

] Cont;

reg [

23

:

0

] Cont;6

7

always@(posedge iCLK or negedge iRST)

always@(posedge iCLK or negedge iRST)8

begin

begin9

if

(

!

iRST)

if

(

!

iRST)10

begin

begin11

oRESET

<=

1

'

b0;

oRESET

<=

1

'

b0;

12

Cont

<=

24

'

h0000000;

Cont

<=

24

'

h0000000;

13

end

end14

else

else

15

begin

begin16

if

(Cont

!=

24

'

hFFFFFF)

if

(Cont

!=

24

'

hFFFFFF)

17

begin

begin18

Cont

<=

Cont

+

1

;

Cont

<=

Cont

+

1

;19

oRESET

<=

1

'

b0;

oRESET

<=

1

'

b0;

20

end

end21

else

else

22

oRESET

<=

1

'

b1;

oRESET

<=

1

'

b1;

23

end

end24

end

end25

26

endmodule

endmodule

SDRAM_PLL.v

//

megafunction wizard: %ALTPLL%

//

megafunction wizard: %ALTPLL%2

//

GENERATION: STANDARD

//

GENERATION: STANDARD3

//

VERSION: WM1.0

//

VERSION: WM1.04

//

MODULE: altpll

//

MODULE: altpll 5

6

//

============================================================

//

============================================================7

//

File Name: SDRAM_PLL.v

//

File Name: SDRAM_PLL.v8

//

Megafunction Name(s):

//

Megafunction Name(s):9

//

altpll

//

altpll10

//

============================================================

//

============================================================11

//

************************************************************

//

************************************************************12

//

THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!

//

THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!13

//

//

14

//

6.0 Build 202 06/20/2006 SP 1 SJ Full Version

//

6.0 Build 202 06/20/2006 SP 1 SJ Full Version15

//

************************************************************

//

************************************************************16

17

18

//

Copyright (C) 1991-2006 Altera Corporation

//

Copyright (C) 1991-2006 Altera Corporation19

//

Your use of Altera Corporation's design tools, logic functions

//

Your use of Altera Corporation's design tools, logic functions 20

//

and other software and tools, and its AMPP partner logic

//

and other software and tools, and its AMPP partner logic 21

//

functions, and any output files any of the foregoing

//

functions, and any output files any of the foregoing 22

//

(including device programming or simulation files), and any

//

(including device programming or simulation files), and any 23

//

associated documentation or information are expressly subject

//

associated documentation or information are expressly subject 24

//

to the terms and conditions of the Altera Program License

//

to the terms and conditions of the Altera Program License 25

//

Subscription Agreement, Altera MegaCore Function License

//

Subscription Agreement, Altera MegaCore Function License 26

//

Agreement, or other applicable license agreement, including,

//

Agreement, or other applicable license agreement, including, 27

//

without limitation, that your use is for the sole purpose of

//

without limitation, that your use is for the sole purpose of 28

//

programming logic devices manufactured by Altera and sold by

//

programming logic devices manufactured by Altera and sold by 29

//

Altera or its authorized distributors. Please refer to the

//

Altera or its authorized distributors. Please refer to the 30

//

applicable agreement for further details.

//

applicable agreement for further details.31

32

33

//

synopsys translate_off

//

synopsys translate_off

34

`timescale

1

ps

/

1

ps

`timescale

1

ps

/

1

ps35

//

synopsys translate_on

//

synopsys translate_on

36

module SDRAM_PLL (

module SDRAM_PLL (37

inclk0,

inclk0,38

c0,

c0,39

c1,

c1,40

c2);

c2);41

42

input inclk0;

input inclk0;43

output c0;

output c0;44

output c1;

output c1;45

output c2;

output c2;46

47

wire [

5

:

0

] sub_wire0;

wire [

5

:

0

] sub_wire0;48

wire [

0

:

0

] sub_wire6

=

1

'

h0;

wire [

0

:

0

] sub_wire6

=

1

'

h0;

49

wire [

2

:

2

] sub_wire3

=

sub_wire0[

2

:

2

];

wire [

2

:

2

] sub_wire3

=

sub_wire0[

2

:

2

];50

wire [

1

:

1

] sub_wire2

=

sub_wire0[

1

:

1

];

wire [

1

:

1

] sub_wire2

=

sub_wire0[

1

:

1

];51

wire [

0

:

0

] sub_wire1

=

sub_wire0[

0

:

0

];

wire [

0

:

0

] sub_wire1

=

sub_wire0[

0

:

0

];52

wire c0

=

sub_wire1;

wire c0

=

sub_wire1;53

wire c1

=

sub_wire2;

wire c1

=

sub_wire2;54

wire c2

=

sub_wire3;

wire c2

=

sub_wire3;55

wire sub_wire4

=

inclk0;

wire sub_wire4

=

inclk0;56

wire [

1

:

0

] sub_wire5

=

{sub_wire6, sub_wire4}

;

wire [

1

:

0

] sub_wire5

=

{sub_wire6, sub_wire4}

;57

58

altpll altpll_component (

altpll altpll_component (59

.inclk (sub_wire5),

.inclk (sub_wire5),60

.clk (sub_wire0),

.clk (sub_wire0),61

.activeclock (),

.activeclock (),62

.areset (

1

'

b0),

.areset (

1

'

b0),

63

.clkbad (),

.clkbad (),64

.clkena (

{6{1'b1}}),

.clkena (

{6{1'b1}}),65

.clkloss (),

.clkloss (),66

.clkswitch (1'b0),

.clkswitch (1'b0),67

.enable0 (),

.enable0 (),68

.enable1 (),

.enable1 (),69

.extclk (),

.extclk (),70

.extclkena ({4{1'b1}}),

.extclkena ({4{1'b1}}),71

.fbin (1'b1),

.fbin (1'b1),72

.locked (),

.locked (),73

.pfdena (1'b1),

.pfdena (1'b1),74

.pllena (1'b1),

.pllena (1'b1),75

.scanaclr (1'b0),

.scanaclr (1'b0),76

.scanclk (1'b0),

.scanclk (1'b0),77

.scandata (1'b0),

.scandata (1'b0),78

.scandataout (),

.scandataout (),79

.scandone (),

.scandone (),80

.scanread (1'b0),

.scanread (1'b0),81

.scanwrite (1'b0),

.scanwrite (1'b0),82

.sclkout0 (),

.sclkout0 (),83

.sclkout1 ());

.sclkout1 ());84

defparam

defparam85

altpll_component.clk0_divide_by = 1,

altpll_component.clk0_divide_by = 1,86

altpll_component.clk0_duty_cycle = 50,

altpll_component.clk0_duty_cycle = 50,87

altpll_component.clk0_multiply_by = 1,

altpll_component.clk0_multiply_by = 1,88

altpll_component.clk0_phase_shift = "-3000",

altpll_component.clk0_phase_shift = "-3000",89

altpll_component.clk1_divide_by = 1,

altpll_component.clk1_divide_by = 1,90

altpll_component.clk1_duty_cycle = 50,

altpll_component.clk1_duty_cycle = 50,91

altpll_component.clk1_multiply_by = 2,

altpll_component.clk1_multiply_by = 2,92

altpll_component.clk1_phase_shift = "0",

altpll_component.clk1_phase_shift = "0",93

altpll_component.clk2_divide_by = 2,

altpll_component.clk2_divide_by = 2,94

altpll_component.clk2_duty_cycle = 50,

altpll_component.clk2_duty_cycle = 50,95

altpll_component.clk2_multiply_by = 1,

altpll_component.clk2_multiply_by = 1,96

altpll_component.clk2_phase_shift = "0",

altpll_component.clk2_phase_shift = "0",97

altpll_component.compensate_clock = "CLK0",

altpll_component.compensate_clock = "CLK0",98

altpll_component.inclk0_input_frequency = 20000,

altpll_component.inclk0_input_frequency = 20000,99

altpll_component.intended_device_family = "Cyclone II",

altpll_component.intended_device_family = "Cyclone II",100

altpll_component.lpm_type = "altpll",

altpll_component.lpm_type = "altpll",101

altpll_component.operation_mode = "NORMAL",

altpll_component.operation_mode = "NORMAL",102

altpll_component.pll_type = "FAST",

altpll_component.pll_type = "FAST",103

altpll_component.port_activeclock = "PORT_UNUSED",

altpll_component.port_activeclock = "PORT_UNUSED",104

altpll_component.port_areset = "PORT_UNUSED",

altpll_component.port_areset = "PORT_UNUSED",105

altpll_component.port_clkbad0 = "PORT_UNUSED",

altpll_component.port_clkbad0 = "PORT_UNUSED",106

altpll_component.port_clkbad1 = "PORT_UNUSED",

altpll_component.port_clkbad1 = "PORT_UNUSED",107

altpll_component.port_clkloss = "PORT_UNUSED",

altpll_component.port_clkloss = "PORT_UNUSED",108

altpll_component.port_clkswitch = "PORT_UNUSED",

altpll_component.port_clkswitch = "PORT_UNUSED",109

altpll_component.port_fbin = "PORT_UNUSED",

altpll_component.port_fbin = "PORT_UNUSED",110

altpll_component.port_inclk0 = "PORT_USED",

altpll_component.port_inclk0 = "PORT_USED",111

altpll_component.port_inclk1 = "PORT_UNUSED",

altpll_component.port_inclk1 = "PORT_UNUSED",112

altpll_component.port_locked = "PORT_UNUSED",

altpll_component.port_locked = "PORT_UNUSED",113

altpll_component.port_pfdena = "PORT_UNUSED",

altpll_component.port_pfdena = "PORT_UNUSED",114

altpll_component.port_pllena = "PORT_UNUSED",

altpll_component.port_pllena = "PORT_UNUSED",115

altpll_component.port_scanaclr = "PORT_UNUSED",

altpll_component.port_scanaclr = "PORT_UNUSED",116

altpll_component.port_scanclk = "PORT_UNUSED",

altpll_component.port_scanclk = "PORT_UNUSED",117

altpll_component.port_scandata = "PORT_UNUSED",

altpll_component.port_scandata = "PORT_UNUSED",118

altpll_component.port_scandataout = "PORT_UNUSED",

altpll_component.port_scandataout = "PORT_UNUSED",119

altpll_component.port_scandone = "PORT_UNUSED",

altpll_component.port_scandone = "PORT_UNUSED",120

altpll_component.port_scanread = "PORT_UNUSED",

altpll_component.port_scanread = "PORT_UNUSED",121

altpll_component.port_scanwrite = "PORT_UNUSED",

altpll_component.port_scanwrite = "PORT_UNUSED",122

altpll_component.port_clk0 = "PORT_USED",

altpll_component.port_clk0 = "PORT_USED",123

altpll_component.port_clk1 = "PORT_USED",

altpll_component.port_clk1 = "PORT_USED",124

altpll_component.port_clk2 = "PORT_USED",

altpll_component.port_clk2 = "PORT_USED",125

altpll_component.port_clk3 = "PORT_UNUSED",

altpll_component.port_clk3 = "PORT_UNUSED",126

altpll_component.port_clk4 = "PORT_UNUSED",

altpll_component.port_clk4 = "PORT_UNUSED",127

altpll_component.port_clk5 = "PORT_UNUSED",

altpll_component.port_clk5 = "PORT_UNUSED",128

altpll_component.port_clkena0 = "PORT_UNUSED",

altpll_component.port_clkena0 = "PORT_UNUSED",129

altpll_component.port_clkena1 = "PORT_UNUSED",

altpll_component.port_clkena1 = "PORT_UNUSED",130

altpll_component.port_clkena2 = "PORT_UNUSED",

altpll_component.port_clkena2 = "PORT_UNUSED",131

altpll_component.port_clkena3 = "PORT_UNUSED",

altpll_component.port_clkena3 = "PORT_UNUSED",132

altpll_component.port_clkena4 = "PORT_UNUSED",

altpll_component.port_clkena4 = "PORT_UNUSED",133

altpll_component.port_clkena5 = "PORT_UNUSED",

altpll_component.port_clkena5 = "PORT_UNUSED",134

altpll_component.port_enable0 = "PORT_UNUSED",

altpll_component.port_enable0 = "PORT_UNUSED",135

altpll_component.port_enable1 = "PORT_UNUSED",

altpll_component.port_enable1 = "PORT_UNUSED",136

altpll_component.port_extclk0 = "PORT_UNUSED",

altpll_component.port_extclk0 = "PORT_UNUSED",137

altpll_component.port_extclk1 = "PORT_UNUSED",

altpll_component.port_extclk1 = "PORT_UNUSED",138

altpll_component.port_extclk2 = "PORT_UNUSED",

altpll_component.port_extclk2 = "PORT_UNUSED",139

altpll_component.port_extclk3 = "PORT_UNUSED",

altpll_component.port_extclk3 = "PORT_UNUSED",140

altpll_component.port_extclkena0 = "PORT_UNUSED",

altpll_component.port_extclkena0 = "PORT_UNUSED",141

altpll_component.port_extclkena1 = "PORT_UNUSED",

altpll_component.port_extclkena1 = "PORT_UNUSED",142

altpll_component.port_extclkena2 = "PORT_UNUSED",

altpll_component.port_extclkena2 = "PORT_UNUSED",143

altpll_component.port_extclkena3 = "PORT_UNUSED",

altpll_component.port_extclkena3 = "PORT_UNUSED",144

altpll_component.port_sclkout0 = "PORT_UNUSED",

altpll_component.port_sclkout0 = "PORT_UNUSED",145

altpll_component.port_sclkout1 = "PORT_UNUSED";

altpll_component.port_sclkout1 = "PORT_UNUSED";146

147

148

endmodule

endmodule149

150

// ============================================================

// ============================================================151

// CNX file retrieval info

// CNX file retrieval info152

// ============================================================

// ============================================================153

// Retrieval info: PRIVATE: ACTIVECLK_CHECK STRING "0"

// Retrieval info: PRIVATE: ACTIVECLK_CHECK STRING "0"154

// Retrieval info: PRIVATE: BANDWIDTH STRING "1.000"

// Retrieval info: PRIVATE: BANDWIDTH STRING "1.000"155

// Retrieval info: PRIVATE: BANDWIDTH_FEATURE_ENABLED STRING "0"

// Retrieval info: PRIVATE: BANDWIDTH_FEATURE_ENABLED STRING "0"156

// Retrieval info: PRIVATE: BANDWIDTH_FREQ_UNIT STRING "MHz"

// Retrieval info: PRIVATE: BANDWIDTH_FREQ_UNIT STRING "MHz"157

// Retrieval info: PRIVATE: BANDWIDTH_PRESET STRING "Low"

// Retrieval info: PRIVATE: BANDWIDTH_PRESET STRING "Low"158

// Retrieval info: PRIVATE: BANDWIDTH_USE_AUTO STRING "1"

// Retrieval info: PRIVATE: BANDWIDTH_USE_AUTO STRING "1"159

// Retrieval info: PRIVATE: BANDWIDTH_USE_CUSTOM STRING "0"

// Retrieval info: PRIVATE: BANDWIDTH_USE_CUSTOM STRING "0"160

// Retrieval info: PRIVATE: BANDWIDTH_USE_PRESET STRING "0"

// Retrieval info: PRIVATE: BANDWIDTH_USE_PRESET STRING "0"161

// Retrieval info: PRIVATE: CLKBAD_SWITCHOVER_CHECK STRING "0"

// Retrieval info: PRIVATE: CLKBAD_SWITCHOVER_CHECK STRING "0"162

// Retrieval info: PRIVATE: CLKLOSS_CHECK STRING "0"

// Retrieval info: PRIVATE: CLKLOSS_CHECK STRING "0"163

// Retrieval info: PRIVATE: CLKSWITCH_CHECK STRING "1"

// Retrieval info: PRIVATE: CLKSWITCH_CHECK STRING "1"164

// Retrieval info: PRIVATE: CNX_NO_COMPENSATE_RADIO STRING "0"

// Retrieval info: PRIVATE: CNX_NO_COMPENSATE_RADIO STRING "0"165

// Retrieval info: PRIVATE: CREATE_CLKBAD_CHECK STRING "0"

// Retrieval info: PRIVATE: CREATE_CLKBAD_CHECK STRING "0"166

// Retrieval info: PRIVATE: CREATE_INCLK1_CHECK STRING "0"

// Retrieval info: PRIVATE: CREATE_INCLK1_CHECK STRING "0"167

// Retrieval info: PRIVATE: CUR_DEDICATED_CLK STRING "c0"

// Retrieval info: PRIVATE: CUR_DEDICATED_CLK STRING "c0"168

// Retrieval info: PRIVATE: CUR_FBIN_CLK STRING "e0"

// Retrieval info: PRIVATE: CUR_FBIN_CLK STRING "e0"169

// Retrieval info: PRIVATE: DEVICE_SPEED_GRADE STRING "Any"

// Retrieval info: PRIVATE: DEVICE_SPEED_GRADE STRING "Any"170

// Retrieval info: PRIVATE: DEV_FAMILY STRING "Cyclone II"

// Retrieval info: PRIVATE: DEV_FAMILY STRING "Cyclone II"171

// Retrieval info: PRIVATE: DIV_FACTOR0 NUMERIC "1"

// Retrieval info: PRIVATE: DIV_FACTOR0 NUMERIC "1"172

// Retrieval info: PRIVATE: DIV_FACTOR1 NUMERIC "2"

// Retrieval info: PRIVATE: DIV_FACTOR1 NUMERIC "2"173

// Retrieval info: PRIVATE: DIV_FACTOR2 NUMERIC "1"

// Retrieval info: PRIVATE: DIV_FACTOR2 NUMERIC "1"174

// Retrieval info: PRIVATE: DUTY_CYCLE0 STRING "50.00000000"

// Retrieval info: PRIVATE: DUTY_CYCLE0 STRING "50.00000000"175

// Retrieval info: PRIVATE: DUTY_CYCLE1 STRING "50.00000000"

// Retrieval info: PRIVATE: DUTY_CYCLE1 STRING "50.00000000"176

// Retrieval info: PRIVATE: DUTY_CYCLE2 STRING "50.00000000"

// Retrieval info: PRIVATE: DUTY_CYCLE2 STRING "50.00000000"177

// Retrieval info: PRIVATE: EXT_FEEDBACK_RADIO STRING "0"

// Retrieval info: PRIVATE: EXT_FEEDBACK_RADIO STRING "0"178

// Retrieval info: PRIVATE: GLOCKED_COUNTER_EDIT_CHANGED STRING "1"

// Retrieval info: PRIVATE: GLOCKED_COUNTER_EDIT_CHANGED STRING "1"179

// Retrieval info: PRIVATE: GLOCKED_FEATURE_ENABLED STRING "1"

// Retrieval info: PRIVATE: GLOCKED_FEATURE_ENABLED STRING "1"180

// Retrieval info: PRIVATE: GLOCKED_MODE_CHECK STRING "0"

// Retrieval info: PRIVATE: GLOCKED_MODE_CHECK STRING "0"181

// Retrieval info: PRIVATE: GLOCK_COUNTER_EDIT NUMERIC "1048575"

// Retrieval info: PRIVATE: GLOCK_COUNTER_EDIT NUMERIC "1048575"182

// Retrieval info: PRIVATE: HAS_MANUAL_SWITCHOVER STRING "1"

// Retrieval info: PRIVATE: HAS_MANUAL_SWITCHOVER STRING "1"183

// Retrieval info: PRIVATE: INCLK0_FREQ_EDIT STRING "50.000"

// Retrieval info: PRIVATE: INCLK0_FREQ_EDIT STRING "50.000"184

// Retrieval info: PRIVATE: INCLK0_FREQ_UNIT_COMBO STRING "MHz"

// Retrieval info: PRIVATE: INCLK0_FREQ_UNIT_COMBO STRING "MHz"185

// Retrieval info: PRIVATE: INCLK1_FREQ_EDIT STRING "50.000"

// Retrieval info: PRIVATE: INCLK1_FREQ_EDIT STRING "50.000"186

// Retrieval info: PRIVATE: INCLK1_FREQ_EDIT_CHANGED STRING "1"

// Retrieval info: PRIVATE: INCLK1_FREQ_EDIT_CHANGED STRING "1"187

// Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_CHANGED STRING "1"

// Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_CHANGED STRING "1"188

// Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_COMBO STRING "MHz"

// Retrieval info: PRIVATE: INCLK1_FREQ_UNIT_COMBO STRING "MHz"189

// Retrieval info: PRIVATE: INT_FEEDBACK__MODE_RADIO STRING "1"

// Retrieval info: PRIVATE: INT_FEEDBACK__MODE_RADIO STRING "1"190

// Retrieval info: PRIVATE: LOCKED_OUTPUT_CHECK STRING "0"

// Retrieval info: PRIVATE: LOCKED_OUTPUT_CHECK STRING "0"191

// Retrieval info: PRIVATE: LONG_SCAN_RADIO STRING "1"

// Retrieval info: PRIVATE: LONG_SCAN_RADIO STRING "1"192

// Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE STRING "Not Available"

// Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE STRING "Not Available"193

// Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE_DIRTY NUMERIC "0"

// Retrieval info: PRIVATE: LVDS_MODE_DATA_RATE_DIRTY NUMERIC "0"194

// Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT0 STRING "deg"

// Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT0 STRING "deg"195

// Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT1 STRING "ps"

// Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT1 STRING "ps"196

// Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT2 STRING "ps"

// Retrieval info: PRIVATE: LVDS_PHASE_SHIFT_UNIT2 STRING "ps"197

// Retrieval info: PRIVATE: MIRROR_CLK0 STRING "0"

// Retrieval info: PRIVATE: MIRROR_CLK0 STRING "0"198

// Retrieval info: PRIVATE: MIRROR_CLK1 STRING "0"

// Retrieval info: PRIVATE: MIRROR_CLK1 STRING "0"199

// Retrieval info: PRIVATE: MIRROR_CLK2 STRING "0"

// Retrieval info: PRIVATE: MIRROR_CLK2 STRING "0"200

// Retrieval info: PRIVATE: MULT_FACTOR0 NUMERIC "1"

// Retrieval info: PRIVATE: MULT_FACTOR0 NUMERIC "1"201

// Retrieval info: PRIVATE: MULT_FACTOR1 NUMERIC "1"

// Retrieval info: PRIVATE: MULT_FACTOR1 NUMERIC "1"202

// Retrieval info: PRIVATE: MULT_FACTOR2 NUMERIC "1"

// Retrieval info: PRIVATE: MULT_FACTOR2 NUMERIC "1"203

// Retrieval info: PRIVATE: NORMAL_MODE_RADIO STRING "1"

// Retrieval info: PRIVATE: NORMAL_MODE_RADIO STRING "1"204

// Retrieval info: PRIVATE: OUTPUT_FREQ0 STRING "50.00000000"

// Retrieval info: PRIVATE: OUTPUT_FREQ0 STRING "50.00000000"205

// Retrieval info: PRIVATE: OUTPUT_FREQ1 STRING "100.00000000"

// Retrieval info: PRIVATE: OUTPUT_FREQ1 STRING "100.00000000"206

// Retrieval info: PRIVATE: OUTPUT_FREQ2 STRING "25.00000000"

// Retrieval info: PRIVATE: OUTPUT_FREQ2 STRING "25.00000000"207

// Retrieval info: PRIVATE: OUTPUT_FREQ_MODE0 STRING "1"

// Retrieval info: PRIVATE: OUTPUT_FREQ_MODE0 STRING "1"208

// Retrieval info: PRIVATE: OUTPUT_FREQ_MODE1 STRING "1"

// Retrieval info: PRIVATE: OUTPUT_FREQ_MODE1 STRING "1"209

// Retrieval info: PRIVATE: OUTPUT_FREQ_MODE2 STRING "1"

// Retrieval info: PRIVATE: OUTPUT_FREQ_MODE2 STRING "1"210

// Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT0 STRING "MHz"

// Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT0 STRING "MHz"211

// Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT1 STRING "MHz"

// Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT1 STRING "MHz"212

// Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT2 STRING "MHz"

// Retrieval info: PRIVATE: OUTPUT_FREQ_UNIT2 STRING "MHz"213

// Retrieval info: PRIVATE: PHASE_SHIFT0 STRING "-3.00000000"

// Retrieval info: PRIVATE: PHASE_SHIFT0 STRING "-3.00000000"214

// Retrieval info: PRIVATE: PHASE_SHIFT1 STRING "0.00000000"

// Retrieval info: PRIVATE: PHASE_SHIFT1 STRING "0.00000000"215

// Retrieval info: PRIVATE: PHASE_SHIFT2 STRING "0.00000000"

// Retrieval info: PRIVATE: PHASE_SHIFT2 STRING "0.00000000"216

// Retrieval info: PRIVATE: PHASE_SHIFT_UNIT0 STRING "ns"

// Retrieval info: PRIVATE: PHASE_SHIFT_UNIT0 STRING "ns"217

// Retrieval info: PRIVATE: PHASE_SHIFT_UNIT1 STRING "ps"

// Retrieval info: PRIVATE: PHASE_SHIFT_UNIT1 STRING "ps"218

// Retrieval info: PRIVATE: PHASE_SHIFT_UNIT2 STRING "ps"

// Retrieval info: PRIVATE: PHASE_SHIFT_UNIT2 STRING "ps"219

// Retrieval info: PRIVATE: PLL_ADVANCED_PARAM_CHECK STRING "0"

// Retrieval info: PRIVATE: PLL_ADVANCED_PARAM_CHECK STRING "0"220

// Retrieval info: PRIVATE: PLL_ARESET_CHECK STRING "0"

// Retrieval info: PRIVATE: PLL_ARESET_CHECK STRING "0"221

// Retrieval info: PRIVATE: PLL_AUTOPLL_CHECK NUMERIC "1"

// Retrieval info: PRIVATE: PLL_AUTOPLL_CHECK NUMERIC "1"222

// Retrieval info: PRIVATE: PLL_ENA_CHECK STRING "0"

// Retrieval info: PRIVATE: PLL_ENA_CHECK STRING "0"223

// Retrieval info: PRIVATE: PLL_ENHPLL_CHECK NUMERIC "0"

// Retrieval info: PRIVATE: PLL_ENHPLL_CHECK NUMERIC "0"224

// Retrieval info: PRIVATE: PLL_FASTPLL_CHECK NUMERIC "0"

// Retrieval info: PRIVATE: PLL_FASTPLL_CHECK NUMERIC "0"225

// Retrieval info: PRIVATE: PLL_LVDS_PLL_CHECK NUMERIC "0"

// Retrieval info: PRIVATE: PLL_LVDS_PLL_CHECK NUMERIC "0"226

// Retrieval info: PRIVATE: PLL_PFDENA_CHECK STRING "0"

// Retrieval info: PRIVATE: PLL_PFDENA_CHECK STRING "0"227

// Retrieval info: PRIVATE: PLL_TARGET_HARCOPY_CHECK NUMERIC "0"

// Retrieval info: PRIVATE: PLL_TARGET_HARCOPY_CHECK NUMERIC "0"228

// Retrieval info: PRIVATE: PRIMARY_CLK_COMBO STRING "inclk0"

// Retrieval info: PRIVATE: PRIMARY_CLK_COMBO STRING "inclk0"229

// Retrieval info: PRIVATE: SACN_INPUTS_CHECK STRING "0"

// Retrieval info: PRIVATE: SACN_INPUTS_CHECK STRING "0"230

// Retrieval info: PRIVATE: SCAN_FEATURE_ENABLED STRING "0"

// Retrieval info: PRIVATE: SCAN_FEATURE_ENABLED STRING "0"231

// Retrieval info: PRIVATE: SELF_RESET_LOCK_LOSS STRING "0"

// Retrieval info: PRIVATE: SELF_RESET_LOCK_LOSS STRING "0"232

// Retrieval info: PRIVATE: SHORT_SCAN_RADIO STRING "0"

// Retrieval info: PRIVATE: SHORT_SCAN_RADIO STRING "0"233

// Retrieval info: PRIVATE: SPREAD_FEATURE_ENABLED STRING "0"

// Retrieval info: PRIVATE: SPREAD_FEATURE_ENABLED STRING "0"234

// Retrieval info: PRIVATE: SPREAD_FREQ STRING "50.000"

// Retrieval info: PRIVATE: SPREAD_FREQ STRING "50.000"235

// Retrieval info: PRIVATE: SPREAD_FREQ_UNIT STRING "KHz"

// Retrieval info: PRIVATE: SPREAD_FREQ_UNIT STRING "KHz"236

// Retrieval info: PRIVATE: SPREAD_PERCENT STRING "0.500"

// Retrieval info: PRIVATE: SPREAD_PERCENT STRING "0.500"237

// Retrieval info: PRIVATE: SPREAD_USE STRING "0"

// Retrieval info: PRIVATE: SPREAD_USE STRING "0"238

// Retrieval info: PRIVATE: SRC_SYNCH_COMP_RADIO STRING "0"

// Retrieval info: PRIVATE: SRC_SYNCH_COMP_RADIO STRING "0"239

// Retrieval info: PRIVATE: STICKY_CLK0 STRING "1"

// Retrieval info: PRIVATE: STICKY_CLK0 STRING "1"240

// Retrieval info: PRIVATE: STICKY_CLK1 STRING "1"

// Retrieval info: PRIVATE: STICKY_CLK1 STRING "1"241

// Retrieval info: PRIVATE: STICKY_CLK2 STRING "1"

// Retrieval info: PRIVATE: STICKY_CLK2 STRING "1"242

// Retrieval info: PRIVATE: SWITCHOVER_COUNT_EDIT NUMERIC "1"

// Retrieval info: PRIVATE: SWITCHOVER_COUNT_EDIT NUMERIC "1"243

// Retrieval info: PRIVATE: SWITCHOVER_FEATURE_ENABLED STRING "1"

// Retrieval info: PRIVATE: SWITCHOVER_FEATURE_ENABLED STRING "1"244

// Retrieval info: PRIVATE: USE_CLK0 STRING "1"

// Retrieval info: PRIVATE: USE_CLK0 STRING "1"245

// Retrieval info: PRIVATE: USE_CLK1 STRING "1"

// Retrieval info: PRIVATE: USE_CLK1 STRING "1"246

// Retrieval info: PRIVATE: USE_CLK2 STRING "1"

// Retrieval info: PRIVATE: USE_CLK2 STRING "1"247

// Retrieval info: PRIVATE: USE_CLKENA0 STRING "0"

// Retrieval info: PRIVATE: USE_CLKENA0 STRING "0"248

// Retrieval info: PRIVATE: USE_CLKENA1 STRING "0"

// Retrieval info: PRIVATE: USE_CLKENA1 STRING "0"249

// Retrieval info: PRIVATE: USE_CLKENA2 STRING "0"

// Retrieval info: PRIVATE: USE_CLKENA2 STRING "0"250

// Retrieval info: PRIVATE: ZERO_DELAY_RADIO STRING "0"

// Retrieval info: PRIVATE: ZERO_DELAY_RADIO STRING "0"251

// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all

// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all252

// Retrieval info: CONSTANT: CLK0_DIVIDE_BY NUMERIC "1"

// Retrieval info: CONSTANT: CLK0_DIVIDE_BY NUMERIC "1"253

// Retrieval info: CONSTANT: CLK0_DUTY_CYCLE NUMERIC "50"

// Retrieval info: CONSTANT: CLK0_DUTY_CYCLE NUMERIC "50"254

// Retrieval info: CONSTANT: CLK0_MULTIPLY_BY NUMERIC "1"

// Retrieval info: CONSTANT: CLK0_MULTIPLY_BY NUMERIC "1"255

// Retrieval info: CONSTANT: CLK0_PHASE_SHIFT STRING "-3000"

// Retrieval info: CONSTANT: CLK0_PHASE_SHIFT STRING "-3000"256

// Retrieval info: CONSTANT: CLK1_DIVIDE_BY NUMERIC "1"

// Retrieval info: CONSTANT: CLK1_DIVIDE_BY NUMERIC "1"257

// Retrieval info: CONSTANT: CLK1_DUTY_CYCLE NUMERIC "50"

// Retrieval info: CONSTANT: CLK1_DUTY_CYCLE NUMERIC "50"258

// Retrieval info: CONSTANT: CLK1_MULTIPLY_BY NUMERIC "2"

// Retrieval info: CONSTANT: CLK1_MULTIPLY_BY NUMERIC "2"259

// Retrieval info: CONSTANT: CLK1_PHASE_SHIFT STRING "0"

// Retrieval info: CONSTANT: CLK1_PHASE_SHIFT STRING "0"260

// Retrieval info: CONSTANT: CLK2_DIVIDE_BY NUMERIC "2"

// Retrieval info: CONSTANT: CLK2_DIVIDE_BY NUMERIC "2"261

// Retrieval info: CONSTANT: CLK2_DUTY_CYCLE NUMERIC "50"

// Retrieval info: CONSTANT: CLK2_DUTY_CYCLE NUMERIC "50"262

// Retrieval info: CONSTANT: CLK2_MULTIPLY_BY NUMERIC "1"

// Retrieval info: CONSTANT: CLK2_MULTIPLY_BY NUMERIC "1"263

// Retrieval info: CONSTANT: CLK2_PHASE_SHIFT STRING "0"

// Retrieval info: CONSTANT: CLK2_PHASE_SHIFT STRING "0"264

// Retrieval info: CONSTANT: COMPENSATE_CLOCK STRING "CLK0"

// Retrieval info: CONSTANT: COMPENSATE_CLOCK STRING "CLK0"265

// Retrieval info: CONSTANT: INCLK0_INPUT_FREQUENCY NUMERIC "20000"

// Retrieval info: CONSTANT: INCLK0_INPUT_FREQUENCY NUMERIC "20000"266

// Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone II"

// Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone II"267

// Retrieval info: CONSTANT: LPM_TYPE STRING "altpll"

// Retrieval info: CONSTANT: LPM_TYPE STRING "altpll"268

// Retrieval info: CONSTANT: OPERATION_MODE STRING "NORMAL"

// Retrieval info: CONSTANT: OPERATION_MODE STRING "NORMAL"269

// Retrieval info: CONSTANT: PLL_TYPE STRING "FAST"

// Retrieval info: CONSTANT: PLL_TYPE STRING "FAST"270

// Retrieval info: CONSTANT: PORT_ACTIVECLOCK STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_ACTIVECLOCK STRING "PORT_UNUSED"271

// Retrieval info: CONSTANT: PORT_ARESET STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_ARESET STRING "PORT_UNUSED"272

// Retrieval info: CONSTANT: PORT_CLKBAD0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_CLKBAD0 STRING "PORT_UNUSED"273

// Retrieval info: CONSTANT: PORT_CLKBAD1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_CLKBAD1 STRING "PORT_UNUSED"274

// Retrieval info: CONSTANT: PORT_CLKLOSS STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_CLKLOSS STRING "PORT_UNUSED"275

// Retrieval info: CONSTANT: PORT_CLKSWITCH STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_CLKSWITCH STRING "PORT_UNUSED"276

// Retrieval info: CONSTANT: PORT_FBIN STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_FBIN STRING "PORT_UNUSED"277

// Retrieval info: CONSTANT: PORT_INCLK0 STRING "PORT_USED"

// Retrieval info: CONSTANT: PORT_INCLK0 STRING "PORT_USED"278

// Retrieval info: CONSTANT: PORT_INCLK1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_INCLK1 STRING "PORT_UNUSED"279

// Retrieval info: CONSTANT: PORT_LOCKED STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_LOCKED STRING "PORT_UNUSED"280

// Retrieval info: CONSTANT: PORT_PFDENA STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_PFDENA STRING "PORT_UNUSED"281

// Retrieval info: CONSTANT: PORT_PLLENA STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_PLLENA STRING "PORT_UNUSED"282

// Retrieval info: CONSTANT: PORT_SCANACLR STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANACLR STRING "PORT_UNUSED"283

// Retrieval info: CONSTANT: PORT_SCANCLK STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANCLK STRING "PORT_UNUSED"284

// Retrieval info: CONSTANT: PORT_SCANDATA STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANDATA STRING "PORT_UNUSED"285

// Retrieval info: CONSTANT: PORT_SCANDATAOUT STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANDATAOUT STRING "PORT_UNUSED"286

// Retrieval info: CONSTANT: PORT_SCANDONE STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANDONE STRING "PORT_UNUSED"287

// Retrieval info: CONSTANT: PORT_SCANREAD STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANREAD STRING "PORT_UNUSED"288

// Retrieval info: CONSTANT: PORT_SCANWRITE STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_SCANWRITE STRING "PORT_UNUSED"289

// Retrieval info: CONSTANT: PORT_clk0 STRING "PORT_USED"

// Retrieval info: CONSTANT: PORT_clk0 STRING "PORT_USED"290

// Retrieval info: CONSTANT: PORT_clk1 STRING "PORT_USED"

// Retrieval info: CONSTANT: PORT_clk1 STRING "PORT_USED"291

// Retrieval info: CONSTANT: PORT_clk2 STRING "PORT_USED"

// Retrieval info: CONSTANT: PORT_clk2 STRING "PORT_USED"292

// Retrieval info: CONSTANT: PORT_clk3 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clk3 STRING "PORT_UNUSED"293

// Retrieval info: CONSTANT: PORT_clk4 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clk4 STRING "PORT_UNUSED"294

// Retrieval info: CONSTANT: PORT_clk5 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clk5 STRING "PORT_UNUSED"295

// Retrieval info: CONSTANT: PORT_clkena0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena0 STRING "PORT_UNUSED"296

// Retrieval info: CONSTANT: PORT_clkena1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena1 STRING "PORT_UNUSED"297

// Retrieval info: CONSTANT: PORT_clkena2 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena2 STRING "PORT_UNUSED"298

// Retrieval info: CONSTANT: PORT_clkena3 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena3 STRING "PORT_UNUSED"299

// Retrieval info: CONSTANT: PORT_clkena4 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena4 STRING "PORT_UNUSED"300

// Retrieval info: CONSTANT: PORT_clkena5 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_clkena5 STRING "PORT_UNUSED"301

// Retrieval info: CONSTANT: PORT_enable0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_enable0 STRING "PORT_UNUSED"302

// Retrieval info: CONSTANT: PORT_enable1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_enable1 STRING "PORT_UNUSED"303

// Retrieval info: CONSTANT: PORT_extclk0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclk0 STRING "PORT_UNUSED"304

// Retrieval info: CONSTANT: PORT_extclk1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclk1 STRING "PORT_UNUSED"305

// Retrieval info: CONSTANT: PORT_extclk2 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclk2 STRING "PORT_UNUSED"306

// Retrieval info: CONSTANT: PORT_extclk3 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclk3 STRING "PORT_UNUSED"307

// Retrieval info: CONSTANT: PORT_extclkena0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclkena0 STRING "PORT_UNUSED"308

// Retrieval info: CONSTANT: PORT_extclkena1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclkena1 STRING "PORT_UNUSED"309

// Retrieval info: CONSTANT: PORT_extclkena2 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclkena2 STRING "PORT_UNUSED"310

// Retrieval info: CONSTANT: PORT_extclkena3 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_extclkena3 STRING "PORT_UNUSED"311

// Retrieval info: CONSTANT: PORT_sclkout0 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_sclkout0 STRING "PORT_UNUSED"312

// Retrieval info: CONSTANT: PORT_sclkout1 STRING "PORT_UNUSED"

// Retrieval info: CONSTANT: PORT_sclkout1 STRING "PORT_UNUSED"313

// Retrieval info: USED_PORT: @clk 0 0 6 0 OUTPUT_CLK_EXT VCC "@clk[5..0]"

// Retrieval info: USED_PORT: @clk 0 0 6 0 OUTPUT_CLK_EXT VCC "@clk[5..0]"314

// Retrieval info: USED_PORT: @extclk 0 0 4 0 OUTPUT_CLK_EXT VCC "@extclk[3..0]"

// Retrieval info: USED_PORT: @extclk 0 0 4 0 OUTPUT_CLK_EXT VCC "@extclk[3..0]"315

// Retrieval info: USED_PORT: c0 0 0 0 0 OUTPUT_CLK_EXT VCC "c0"

// Retrieval info: USED_PORT: c0 0 0 0 0 OUTPUT_CLK_EXT VCC "c0"316

// Retrieval info: USED_PORT: c1 0 0 0 0 OUTPUT_CLK_EXT VCC "c1"

// Retrieval info: USED_PORT: c1 0 0 0 0 OUTPUT_CLK_EXT VCC "c1"317

// Retrieval info: USED_PORT: c2 0 0 0 0 OUTPUT_CLK_EXT VCC "c2"

// Retrieval info: USED_PORT: c2 0 0 0 0 OUTPUT_CLK_EXT VCC "c2"318

// Retrieval info: USED_PORT: inclk0 0 0 0 0 INPUT_CLK_EXT GND "inclk0"

// Retrieval info: USED_PORT: inclk0 0 0 0 0 INPUT_CLK_EXT GND "inclk0"319

// Retrieval info: CONNECT: @inclk 0 0 1 0 inclk0 0 0 0 0

// Retrieval info: CONNECT: @inclk 0 0 1 0 inclk0 0 0 0 0320

// Retrieval info: CONNECT: c0 0 0 0 0 @clk 0 0 1 0

// Retrieval info: CONNECT: c0 0 0 0 0 @clk 0 0 1 0321

// Retrieval info: CONNECT: c1 0 0 0 0 @clk 0 0 1 1

// Retrieval info: CONNECT: c1 0 0 0 0 @clk 0 0 1 1322

// Retrieval info: CONNECT: c2 0 0 0 0 @clk 0 0 1 2

// Retrieval info: CONNECT: c2 0 0 0 0 @clk 0 0 1 2323

// Retrieval info: CONNECT: @inclk 0 0 1 1 GND 0 0 0 0

// Retrieval info: CONNECT: @inclk 0 0 1 1 GND 0 0 0 0324

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.v TRUE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.v TRUE FALSE325

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.inc FALSE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.inc FALSE FALSE326

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.cmp FALSE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.cmp FALSE FALSE327

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.bsf FALSE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.bsf FALSE FALSE328

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL_inst.v FALSE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL_inst.v FALSE FALSE329

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL_bb.v FALSE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL_bb.v FALSE FALSE330

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL_waveforms.html FALSE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL_waveforms.html FALSE FALSE331

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL_wave*.jpg FALSE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL_wave*.jpg FALSE FALSE332

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.ppf TRUE FALSE

// Retrieval info: GEN_FILE: TYPE_NORMAL SDRAM_PLL.ppf TRUE FALSE

你一定會問,為什麼還要自己加上Reset_Delay.v和SDRAM_PLL.v,明明我只用到SRAM,卻還要用到SDRAM的pll?

這是參考友晶科技reference design的作法,所以加上Reset_Delay.v和SDRAM_PLL.v。

先談SDRAM_PLL.v,這是由MegaWizard透過MegaCore產生出來的code,主要有三個功能,c0產生SDRAM所需要的50MHz相位延遲60度的clock,c1產生100MHz給Nios II CPU使用,c2產生除頻的25MHz,由於要讓Nios II CPU跑100MHz,所以才動用SDRAM_PLL.v。

Reset_Delay.v則是延緩reset的時間,詳細理由我還不清楚。

根據實驗,若你願意只讓Nios II CPU只跑50MHz,的確可以不加SDRAM_PLL.v和Reset_Delay.v,依然可以正常運作。

hello_ucosii.v

module hello_ucosii (

module hello_ucosii (2

//////////////////// Clock Input ////////////////////

//////////////////// Clock Input ////////////////////

3

CLOCK_27,

//

On Board 27 MHz

CLOCK_27,

//

On Board 27 MHz

4

CLOCK_50,

//

On Board 50 MHz

CLOCK_50,

//

On Board 50 MHz

5

EXT_CLOCK,

//

External Clock

EXT_CLOCK,

//

External Clock

6

//////////////////// Push Button ////////////////////

//////////////////// Push Button ////////////////////

7

KEY,

//

Pushbutton[3:0]

KEY,

//

Pushbutton[3:0]

8

//////////////////// Flash Interface ////////////////

//////////////////// Flash Interface ////////////////

9

FL_DQ,

//

FLASH Data bus 8 Bits

FL_DQ,

//

FLASH Data bus 8 Bits

10

FL_ADDR,

//

FLASH Address bus 20 Bits

FL_ADDR,

//

FLASH Address bus 20 Bits

11

FL_WE_N,

//

FLASH Write Enable

FL_WE_N,

//

FLASH Write Enable

12

FL_RST_N,

//

FLASH Reset

FL_RST_N,

//

FLASH Reset

13

FL_OE_N,

//

FLASH Output Enable

FL_OE_N,

//

FLASH Output Enable

14

FL_CE_N,

//

FLASH Chip Enable

FL_CE_N,

//

FLASH Chip Enable

15

//////////////////// SRAM Interface ////////////////

//////////////////// SRAM Interface ////////////////

16

SRAM_DQ,

//

SRAM Data bus 16 Bits

SRAM_DQ,

//

SRAM Data bus 16 Bits

17

SRAM_ADDR,

//

SRAM Address bus 18 Bits

SRAM_ADDR,

//

SRAM Address bus 18 Bits

18

SRAM_UB_N,

//

SRAM High-byte Data Mask

SRAM_UB_N,

//

SRAM High-byte Data Mask

19

SRAM_LB_N,

//

SRAM Low-byte Data Mask

SRAM_LB_N,

//

SRAM Low-byte Data Mask

20

SRAM_WE_N,

//

SRAM Write Enable

SRAM_WE_N,

//

SRAM Write Enable

21

SRAM_CE_N,

//

SRAM Chip Enable

SRAM_CE_N,

//

SRAM Chip Enable

22

SRAM_OE_N

//

SRAM Output Enable

SRAM_OE_N

//

SRAM Output Enable

23

);

);24

25

//////////////////////// Clock Input ////////////////////////

//////////////////////// Clock Input ////////////////////////

26

input CLOCK_27;

//

On Board 27 MHz

input CLOCK_27;

//

On Board 27 MHz

27

input CLOCK_50;

//

On Board 50 MHz

input CLOCK_50;

//

On Board 50 MHz

28

input EXT_CLOCK;

//

External Clock

input EXT_CLOCK;

//

External Clock

29

30

//////////////////////// Push Button ////////////////////////

//////////////////////// Push Button ////////////////////////

31

input [

3

:

0

] KEY;

//

Pushbutton[3:0]

input [

3

:

0

] KEY;

//

Pushbutton[3:0]

32

33

//////////////////////// Flash Interface ////////////////////////

//////////////////////// Flash Interface ////////////////////////

34

inout [

7

:

0

] FL_DQ;

//

FLASH Data bus 8 Bits

inout [

7

:

0

] FL_DQ;

//

FLASH Data bus 8 Bits

35

output [

21

:

0

] FL_ADDR;

//

FLASH Address bus 22 Bits

output [

21

:

0

] FL_ADDR;

//

FLASH Address bus 22 Bits

36

output FL_WE_N;

//

FLASH Write Enable

output FL_WE_N;

//

FLASH Write Enable

37

output FL_RST_N;

//

FLASH Reset

output FL_RST_N;

//

FLASH Reset

38

output FL_OE_N;

//

FLASH Output Enable

output FL_OE_N;

//

FLASH Output Enable

39

output FL_CE_N;

//

FLASH Chip Enable

output FL_CE_N;

//

FLASH Chip Enable

40

41

//////////////////////// SRAM Interface ////////////////////////

//////////////////////// SRAM Interface ////////////////////////

42

inout [

15

:

0

] SRAM_DQ;

//

SRAM Data bus 16 Bits

inout [

15

:

0

] SRAM_DQ;

//

SRAM Data bus 16 Bits

43

output [

17

:

0

] SRAM_ADDR;

//

SRAM Address bus 18 Bits

output [

17

:

0

] SRAM_ADDR;

//

SRAM Address bus 18 Bits

44

output SRAM_UB_N;

//

SRAM Low-byte Data Mask

output SRAM_UB_N;

//

SRAM Low-byte Data Mask

45

output SRAM_LB_N;

//

SRAM High-byte Data Mask

output SRAM_LB_N;

//

SRAM High-byte Data Mask

46

output SRAM_WE_N;

//

SRAM Write Enable

output SRAM_WE_N;

//

SRAM Write Enable

47

output SRAM_CE_N;

//

SRAM Chip Enable

output SRAM_CE_N;

//

SRAM Chip Enable

48

output SRAM_OE_N;

//

SRAM Output Enable

output SRAM_OE_N;

//

SRAM Output Enable49

50

//

Flash

//

Flash

51

assign FL_RST_N

=

1

'

b1;

assign FL_RST_N

=

1

'

b1;

52

53

nios_ii u0 (

nios_ii u0 (54

//

1) global signals:

//

1) global signals:

55

.clk(CPU_CLK),

.clk(CPU_CLK),56

.reset_n(KEY[

0

]),

.reset_n(KEY[

0

]),57

58

//

the_sram_0

//

the_sram_0

59

.SRAM_ADDR_from_the_sram_16bit_512k_0(SRAM_ADDR),

.SRAM_ADDR_from_the_sram_16bit_512k_0(SRAM_ADDR),60

.SRAM_CE_N_from_the_sram_16bit_512k_0(SRAM_CE_N),

.SRAM_CE_N_from_the_sram_16bit_512k_0(SRAM_CE_N),61

.SRAM_DQ_to_and_from_the_sram_16bit_512k_0(SRAM_DQ),

.SRAM_DQ_to_and_from_the_sram_16bit_512k_0(SRAM_DQ),62

.SRAM_LB_N_from_the_sram_16bit_512k_0(SRAM_LB_N),

.SRAM_LB_N_from_the_sram_16bit_512k_0(SRAM_LB_N),63

.SRAM_OE_N_from_the_sram_16bit_512k_0(SRAM_OE_N),

.SRAM_OE_N_from_the_sram_16bit_512k_0(SRAM_OE_N),64

.SRAM_UB_N_from_the_sram_16bit_512k_0(SRAM_UB_N),

.SRAM_UB_N_from_the_sram_16bit_512k_0(SRAM_UB_N),65

.SRAM_WE_N_from_the_sram_16bit_512k_0(SRAM_WE_N),

.SRAM_WE_N_from_the_sram_16bit_512k_0(SRAM_WE_N),66

67

//

the_tri_state_bridge_0_avalon_slave

//

the_tri_state_bridge_0_avalon_slave

68

.select_n_to_the_cfi_flash(FL_CE_N),

.select_n_to_the_cfi_flash(FL_CE_N),69

.address_to_the_cfi_flash(FL_ADDR),

.address_to_the_cfi_flash(FL_ADDR),70

.data_to_and_from_the_cfi_flash(FL_DQ),

.data_to_and_from_the_cfi_flash(FL_DQ),71

.read_n_to_the_cfi_flash(FL_OE_N),

.read_n_to_the_cfi_flash(FL_OE_N),72

.write_n_to_the_cfi_flash(FL_WE_N)

.write_n_to_the_cfi_flash(FL_WE_N)73

);

);74

75

endmodule

endmodule

處理pin腳

Step 1:

pins.tcl

cmp add_assignment

"

hello_ucosii

"

""

"

CLOCK_27

"

"

LOCATION

"

"

PIN_D13

"

cmp add_assignment

"

hello_ucosii

"

""

"

CLOCK_27

"

"

LOCATION

"

"

PIN_D13

"

2

cmp add_assignment

"

hello_ucosii

"

""

"

CLOCK_50

"

"

LOCATION

"

"

PIN_N2

"

cmp add_assignment

"

hello_ucosii

"

""

"

CLOCK_50

"

"

LOCATION

"

"

PIN_N2

"

3

cmp add_assignment

"

hello_ucosii

"

""

"

EXT_CLOCK

"

"

LOCATION

"

"

PIN_N26

"

cmp add_assignment

"

hello_ucosii

"

""

"

EXT_CLOCK

"

"

LOCATION

"

"

PIN_N26

"

4

cmp add_assignment

"

hello_ucosii

"

""

"

EXT_CLOCK

"

"

LOCATION

"

"

PIN_N26

"

cmp add_assignment

"

hello_ucosii

"

""

"

EXT_CLOCK

"

"

LOCATION

"

"

PIN_N26

"

5

cmp add_assignment

"

hello_ucosii

"

""

"

KEY[0]

"

"

LOCATION

"

"

PIN_G26

"

cmp add_assignment

"

hello_ucosii

"

""

"

KEY[0]

"

"

LOCATION

"

"

PIN_G26

"

6

cmp add_assignment

"

hello_ucosii

"

""

"

KEY[1]

"

"

LOCATION

"

"

PIN_N23

"

cmp add_assignment

"

hello_ucosii

"

""

"

KEY[1]

"

"

LOCATION

"

"

PIN_N23

"

7

cmp add_assignment

"

hello_ucosii

"

""

"

KEY[2]

"

"

LOCATION

"

"

PIN_P23

"

cmp add_assignment

"

hello_ucosii

"

""

"

KEY[2]

"

"

LOCATION

"

"

PIN_P23

"

8

cmp add_assignment

"

hello_ucosii

"

""

"

KEY[3]

"

"

LOCATION

"

"

PIN_W26

"

cmp add_assignment

"

hello_ucosii

"

""

"

KEY[3]

"

"

LOCATION

"

"

PIN_W26

"

9

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[0]

"

"

LOCATION

"

"

PIN_AE4

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[0]

"

"

LOCATION

"

"

PIN_AE4

"

10

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[1]

"

"

LOCATION

"

"

PIN_AF4

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[1]

"

"

LOCATION

"

"

PIN_AF4

"

11

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[2]

"

"

LOCATION

"

"

PIN_AC5

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[2]

"

"

LOCATION

"

"

PIN_AC5

"

12

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[3]

"

"

LOCATION

"

"

PIN_AC6

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[3]

"

"

LOCATION

"

"

PIN_AC6

"

13

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[4]

"

"

LOCATION

"

"

PIN_AD4

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[4]

"

"

LOCATION

"

"

PIN_AD4

"

14

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[5]

"

"

LOCATION

"

"

PIN_AD5

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[5]

"

"

LOCATION

"

"

PIN_AD5

"

15

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[6]

"

"

LOCATION

"

"

PIN_AE5

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[6]

"

"

LOCATION

"

"

PIN_AE5

"

16

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[7]

"

"

LOCATION

"

"

PIN_AF5

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[7]

"

"

LOCATION

"

"

PIN_AF5

"

17

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[8]

"

"

LOCATION

"

"

PIN_AD6

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[8]

"

"

LOCATION

"

"

PIN_AD6

"

18

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[9]

"

"

LOCATION

"

"

PIN_AD7

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[9]

"

"

LOCATION

"

"

PIN_AD7

"

19

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[10]

"

"

LOCATION

"

"

PIN_V10

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[10]

"

"

LOCATION

"

"

PIN_V10

"

20

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[11]

"

"

LOCATION

"

"

PIN_V9

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[11]

"

"

LOCATION

"

"

PIN_V9

"

21

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[12]

"

"

LOCATION

"

"

PIN_AC7

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[12]

"

"

LOCATION

"

"

PIN_AC7

"

22

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[13]

"

"

LOCATION

"

"

PIN_W8

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[13]

"

"

LOCATION

"

"

PIN_W8

"

23

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[14]

"

"

LOCATION

"

"

PIN_W10

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[14]

"

"

LOCATION

"

"

PIN_W10

"

24

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[15]

"

"

LOCATION

"

"

PIN_Y10

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[15]

"

"

LOCATION

"

"

PIN_Y10

"

25

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[16]

"

"

LOCATION

"

"

PIN_AB8

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[16]

"

"

LOCATION

"

"

PIN_AB8

"

26

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[17]

"

"

LOCATION

"

"

PIN_AC8

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_ADDR[17]

"

"

LOCATION

"

"

PIN_AC8

"

27

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_CE_N

"

"

LOCATION

"

"

PIN_AC11

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_CE_N

"

"

LOCATION

"

"

PIN_AC11

"

28

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[0]

"

"

LOCATION

"

"

PIN_AD8

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[0]

"

"

LOCATION

"

"

PIN_AD8

"

29

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[1]

"

"

LOCATION

"

"

PIN_AE6

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[1]

"

"

LOCATION

"

"

PIN_AE6

"

30

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[2]

"

"

LOCATION

"

"

PIN_AF6

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[2]

"

"

LOCATION

"

"

PIN_AF6

"

31

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[3]

"

"

LOCATION

"

"

PIN_AA9

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[3]

"

"

LOCATION

"

"

PIN_AA9

"

32

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[4]

"

"

LOCATION

"

"

PIN_AA10

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[4]

"

"

LOCATION

"

"

PIN_AA10

"

33

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[5]

"

"

LOCATION

"

"

PIN_AB10

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[5]

"

"

LOCATION

"

"

PIN_AB10

"

34

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[6]

"

"

LOCATION

"

"

PIN_AA11

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[6]

"

"

LOCATION

"

"

PIN_AA11

"

35

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[7]

"

"

LOCATION

"

"

PIN_Y11

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[7]

"

"

LOCATION

"

"

PIN_Y11

"

36

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[8]

"

"

LOCATION

"

"

PIN_AE7

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[8]

"

"

LOCATION

"

"

PIN_AE7

"

37

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[9]

"

"

LOCATION

"

"

PIN_AF7

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[9]

"

"

LOCATION

"

"

PIN_AF7

"

38

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[10]

"

"

LOCATION

"

"

PIN_AE8

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[10]

"

"

LOCATION

"

"

PIN_AE8

"

39

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[11]

"

"

LOCATION

"

"

PIN_AF8

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[11]

"

"

LOCATION

"

"

PIN_AF8

"

40

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[12]

"

"

LOCATION

"

"

PIN_W11

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[12]

"

"

LOCATION

"

"

PIN_W11

"

41

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[13]

"

"

LOCATION

"

"

PIN_W12

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[13]

"

"

LOCATION

"

"

PIN_W12

"

42

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[14]

"

"

LOCATION

"

"

PIN_AC9

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[14]

"

"

LOCATION

"

"

PIN_AC9

"

43

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[15]

"

"

LOCATION

"

"

PIN_AC10

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_DQ[15]

"

"

LOCATION

"

"

PIN_AC10

"

44

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_LB_N

"

"

LOCATION

"

"

PIN_AE9

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_LB_N

"

"

LOCATION

"

"

PIN_AE9

"

45

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_OE_N

"

"

LOCATION

"

"

PIN_AD10

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_OE_N

"

"

LOCATION

"

"

PIN_AD10

"

46

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_UB_N

"

"

LOCATION

"

"

PIN_AF9

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_UB_N

"

"

LOCATION

"

"

PIN_AF9

"

47

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_WE_N

"

"

LOCATION

"

"

PIN_AE10

"

cmp add_assignment

"

hello_ucosii

"

""

"

SRAM_WE_N

"

"

LOCATION

"

"

PIN_AE10

"

48

cmp add_assignment

"

hello_ucosii

"

""

"

FL_CE_N

"

"

LOCATION

"

"

PIN_V17

"

cmp add_assignment

"

hello_ucosii

"

""

"

FL_CE_N

"

"

LOCATION

"

"

PIN_V17

"

49

cmp add_assignment

"

hello_ucosii

"

""

"

FL_ADDR[0]

"

"

LOCATION

"

"

PIN_AC18

"

cmp add_assignment

"

hello_ucosii

"

""

"

FL_ADDR[0]

"

"

LOCATION

"

"

PIN_AC18

"

50

cmp add_assignment

"

hello_ucosii

"

""

"

FL_ADDR[1]

"

"

LOCATION

"

"

PIN_AB18