RTL Compiler之Example

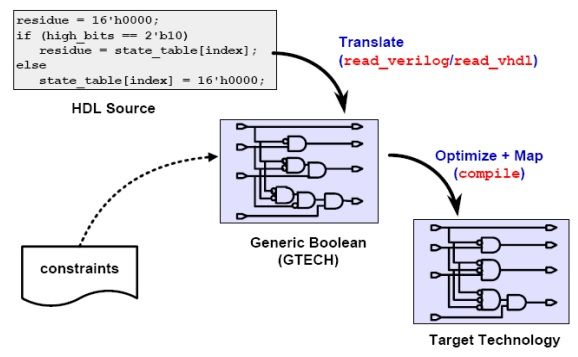

Synthesis = Translation + Logic Optimization + Mapping

Step 1 Source files

1) make directory

1 mkdir Lab 2 cd Lab 3 mkdir HDL 4 cd HDL

2) Verilog code

1 // --------- Full Adder ----------------- 2 module fulladder(sum, c_out, x, y, c_in); 3 output sum, c_out; 4 input x, y, c_in; 5 6 wire a, b, c; 7 8 xor(a, x, y); 9 xor(sum, a, c_in); 10 and(b, x, y); 11 and(c, a, c_in); 12 or(c_out, c, b); 13 14 endmodule

1 // ------- 4-Bit Adder --------------------- 2 module FourBitAdder(sum, c_out, x, y, c_in); 3 output [3:0] sum; 4 output c_out; 5 input [3:0] x, y; 6 input c_in; 7 wire c1,c2,c3; 8 9 fulladder fa0(sum[0], c1, x[0], y[0], c_in); 10 fulladder fa1(sum[1], c2, x[1], y[1], c1); 11 fulladder fa2(sum[2], c3, x[2], y[2], c2); 12 fulladder fa3(sum[3], c_out, x[3], y[3], c3); 13 14 endmodule

Step 2 Invoke RTL Compiler

rc -gui

Step 3 Setting the lib

# This tells the compiler where to look for the libraries set_attribute lib_search_path /home/cadence/ic-6.1.0/tools.lnx86/dfII/local/ncsu-cdk-1.6.0.bet a/lib/tsmc025/signalstorm # This defines the libraries to use set_attribute library {osu025_stdcells.lib}

This step I got the following messages: (maybe the osu025 library is not configured correctly)

Could not find an attribute in the library. [LBR-436]: 101

Missing library level attribute. [LBR-516]: 1

library download: http://vlsiarch.ecen.okstate.edu/flows/MOSIS_SCMOS/

Step 4 Read and Elaborate RTL

# This must point to your VHDL/verilog file read_hdl ../HDL/FourBitAdder.v # Elaborate your top-level module set DESIGN "FourBitAdder" elaborate $DESIGN

Step 5 Apply Constraints

Since the design is a very simple, we only set the some operating conditions, for example:

# Setting constraints set_attribute wireload_mode enclosed # Use the default wireload operaqtion mode set_attribute max_dynamic_power 0.0 $DESIGN # Restrict RC to optimise for dynamic and leakage power set_attribute max_leakage_power 0.0 $DESIGN

Step 6 Synthesize/Compile

# This synthesizes your design set MAP_EFF high synthesize -to_mapped -eff $MAP_EFF -no_incr

# This section writes the mapped design and sdc file # THESE FILES YOU WILL NEED THEM WHEN SETTING UP THE PLACE & ROUTE write -mapped > ${DESIGN}_synth.v write_sdc > ${DESIGN}.sdc

Step 7 Analyze Timing and Power

# report and analyze power and timing report power > ${DESIGN}.power.rpt report timing > ${DESIGN}.timing.rpt

Step 8 Exit

# exit exit