学习笔记 -《量子计算与编程入门》- 量子计算机硬件基础

文章目录

- 1 量子芯片

-

- 1.1 超导量子芯片

-

- 1.1.1 超导量子计算的进展

- 1.2 半导体量子芯片

-

- 1.2.1 基于电荷位置的量子比特

- 1.2.2 基于自旋的量子比特

- 1.2.3 半导体量子计算也正在从科研界转向工业界

- 1.3 其他类型体系的量子计算体系

-

- 1.3.1 离子阱量子计算

- 1.3.2 原子量子计算

- 1.3.3 核自旋量子计算

- 1.3.4 拓扑量子计算

- 2 量子计算机硬件

-

- 2.1 量子芯片支持系统

- 2.2 量子计算机控制系统

- 3 量子计算机

-

- 3.1 量子计算机整体架构

-

- 3.1.1 **量子计算的定位:[异构计算**]

- 3.1.2 量子程序代码构成:宿主代码 + 设备代码

- 3.2 量子程序架构(设备代码的架构)

-

- 3.2.1 量子高级语言

- 3.2.2 量子汇编语言的编译原则

- 3.2.3 量子程序的可执行文件

1 量子芯片

1.1 超导量子芯片

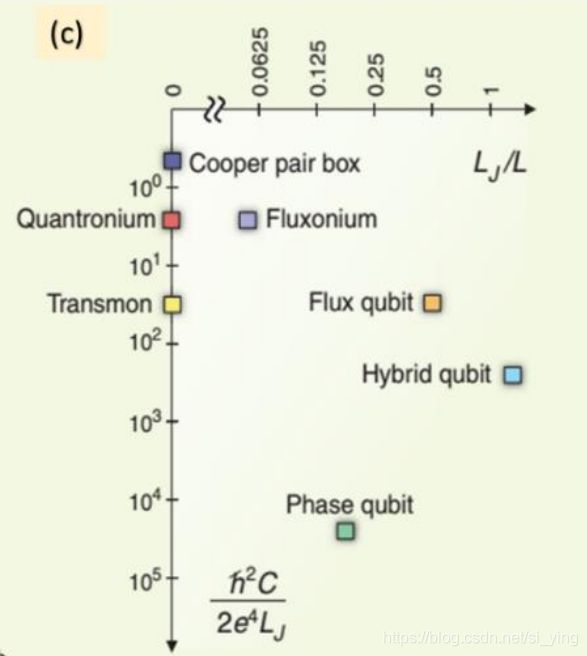

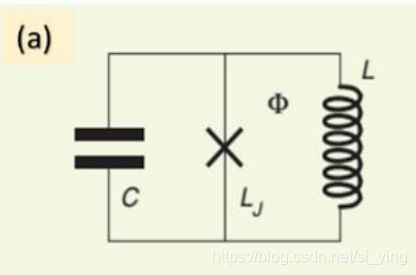

超导量子计算是基于超导电路的量子计算方案,其核心器件是超导约瑟夫森结。

超导量子电路在设计、制备和测量等方面,与现有的集成电路技术具有较高的兼容性,对量子比特的能级与耦合可以实现非常灵活的设计与控制,极具规模化的潜力。

由于近年来的迅速发展,超导量子计算已成为目前最有希望实现通用量子计算的候选方案之一。超导量子计算实验点致力于构建一个多比特超导量子计算架构平台,解决超导量子计算规模化量产中遇到的难题。

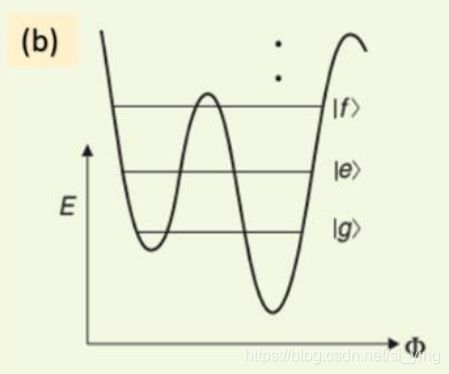

超导电路类似于传统的电子谐振电路,这种谐振电路产生了谐振子的能级。

超导约瑟夫森效应使得超导电路在不发生损耗和退相干的情况下产生非线性,非线性导致谐振子的能级间隔不再等同,其中最低的两个能级可以用来实现量子比特的操控。

与经典谐振电路不同的是,超导电路还含有由约瑟夫森结带来的电感 L j L_j Lj 这一项,改变这一项和电感 L L L、电容 C C C 的比值,物理学家提出了多种基于超导线路的比特形式。

1.1.1 超导量子计算的进展

| 2000年前后 | 开始研究 | |

|---|---|---|

| – 2009年 | 来在美国耶鲁大学 Schoelkopf 和 Devoret 研究组的推动下,将超导比特和微波腔进行耦合 | 实现了量子比特高保真度的读出和纠缠,加速了超导量子比特的研究;实现了两比特的高保真度量子算法;使得超导量子计算得到了世界的广泛关注 |

| 2014年 – | 美国企业界开始关注超导量子比特的研究,并加入了研究的大潮中 | |

| 2014年 9 月 | 美国 Google 公司与美国加州大学圣芭芭拉分校合作研究超导量子比特,使用 X-mon 形式的超导量子比特 | 2016 年基于这个芯片实现了对氢分子能量的模拟,表明了其对于量子计算商用化的决心 |

| 2017 年 | Google 发布了实现量子计算机对经典计算机的超越——“量子霸权”的发展蓝图 | |

| 2018 年 | Google设计了 72 比特的量子芯片,并着手进行制备和测量 | |

| 2016年 5 月 | IBM在云平台上发布了 Transmon 形式的5 比特量子芯片 | |

| 2017年 | IBM 制备了 20 比特的芯片,并展示了用于 50 比特芯片的测量设备,同时也公布了对 BeH2 分子能量的模拟 | 表明了在量子计算的研究上紧随 Google 的步伐 |

| IBM 发布了 QISKit 的量子软件包 | 促进了人们通过经典编程语言实现对量子计算机的操控。 | |

| 2018 年 | 美国 Intel 公司和荷兰代尔夫特理工大学合作设计了17 比特和 49 比特超导量子芯片 | 具体的性能参数还有待测试 |

| 美国初创公司 Rigetti 发布了 19 比特超导量子芯片,并演示了无人监督的机器学习算法 | 使人们见到了利用量子计算机加速机器学习的曙光 | |

| 美国微软公司开发了 Quantum Development Kit 量子计算软件包 | 通过传统的软件产品 Visual Studio 就可以进行量子程序的编写 | |

| 2017 年 | 中国科学技术大学潘建伟研究组实现了多达十个超导比特的纠缠 | |

| 2018 年 | 中科院和阿里云联合发布了 11 位量子比特芯片 | 表明了我国在超导量子计算方面也不甘落后,并迎头赶上 |

| 合肥本源量子公司也正在开发 6 比特高保真度量子芯片 | ||

| 南京大学和浙江大学也对超导量子比特进行了卓有成效的研究 | ||

| …… | …… | …… |

1.2 半导体量子芯片

由于经典计算机主要基于半导体技术,基于半导体开发量子计算也是物理学家研究的重点领域。相比超导量子计算微米级别的比特大小,量子点量子比特所占的空间是纳米级别。

类似于大规模集成电路一样,更有希望实现大规模的量子芯片。现在的主要方法是在硅或者砷化镓等半导体材料上制备门控量子点来编码量子比特。编码量子比特的方案多种多样,在半导体系统中主要是通过对电子的电荷或者自旋量子态的控制实现。

1.2.1 基于电荷位置的量子比特

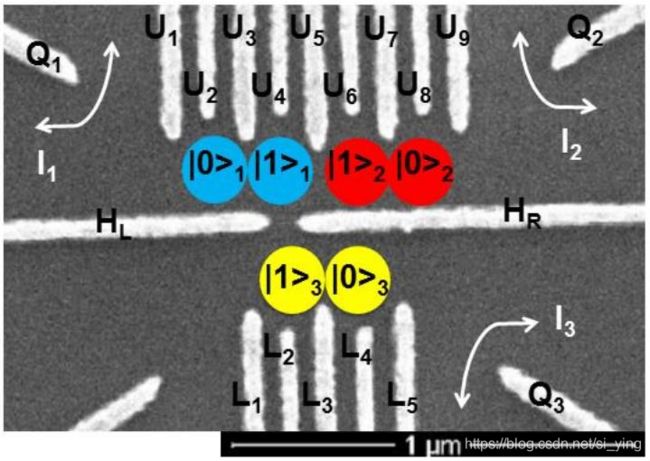

这是中国科学技术大学郭国平研究组利用 GaAs / AlGaAs 异质结制备的三电荷量子比特的样品。

图中 Q 1 Q_1 Q1、 Q 2 Q_2 Q2 和 Q 3 Q_3 Q3 作为探测器可以探测由 U U U、 L L L 电极形成的量子点中电荷的状态;

六个圆圈代表六个量子点,每种颜色代表一个电荷量子比特。以两个黄圈为例,当电子处于右边量子点中时,它处于量子比特的基态,代表 0 0 0;当电子处于左边量子点时,它处于量子比特的激发态,代表 1 1 1。

这三个比特的相互作用可以通过量子点之间的电极调节,因而可以用来形成三比特控制操作。

缺点:这种三比特操作的保真度较低,提高保真度需要进一步抑制电荷噪声。

1.2.2 基于自旋的量子比特

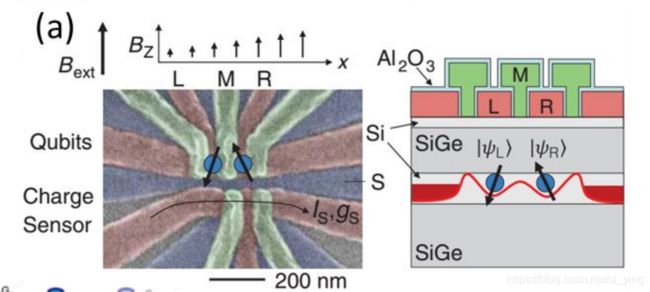

这是美国普林斯顿大学 Petta 研究组基于 Si/SiGe 异质结制备的两自旋量子比特芯片,

图中带箭头的圆圈代表不同自旋方向的电子;

自旋在磁场下劈裂产生的两个能级可以用于编码量子比特;

这两个量子比特之间的耦合可以通过中间的电极 M M M 进行控制,实现两比特操作。

优点:由于对电荷噪声有较高的免疫效果,自旋量子比特的退相干时间非常长。

1.2.3 半导体量子计算也正在从科研界转向工业界

与超导量子计算类似,半导体量子计算也正在从科研界转向工业界。

2016 年,美国芯片巨头 Intel 公司开始投资代尔夫特理工大学的硅基量子计算研究,目标是在五年内制备出第一个二维表面码结构下的逻辑量子比特;

2017 年,澳大利亚也组建了硅量子计算公司,目标是五年内制备出第一台 10 比特硅基量子计算机;

在国内,中国科学技术大学的郭国平研究组 从 2016 年开启了硅基量子比特计划,计划五年内制备出硅基高保真度的两比特量子逻辑门,实现对国际水平的追赶,并为进一步的超越做准备。

1.3 其他类型体系的量子计算体系

1.3.1 离子阱量子计算

离子阱量子计算在影响范围方面仅次于超导量子计算。早在 2003 年,基于离子阱就可以演示两比特量子算法。

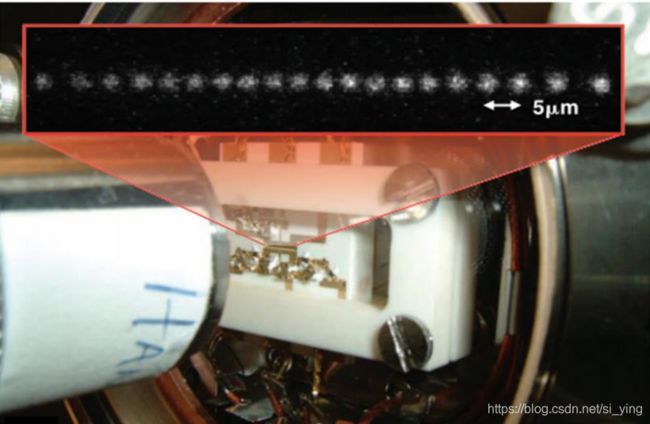

离子阱编码量子比特主要是利用真空腔中的电场囚禁少数离子,并通过激光冷却这些囚禁的离子。

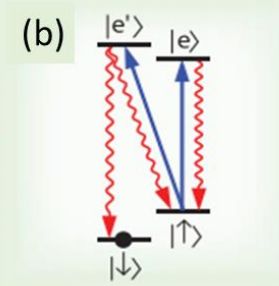

以囚禁 Yb+ 离子为例:

20 个 Yb+ 连成一排,每一个离子在超精细相互作用下产生的两个能级作为量子比特的两个能级,标记为 |↑> 和 |↓>;

下图表示通过合适的激光可以将离子调节到基态:

下图表示可以通过观察荧光来探测比特是否处于 |↑>。

优点:

离子阱的读出和初始化效率可以接近 100%,这是它超过前两种比特形式的优势。

研究进展:

国外:

2016 年,美国马里兰大学 C. Monroe 组基于离子阱制备了 5 比特可编程量子计算机,其单比特和两比特的操作保真度平均可以达到 98%,运行 Deutsch–Jozsa 算法的保真度可以达到95%;

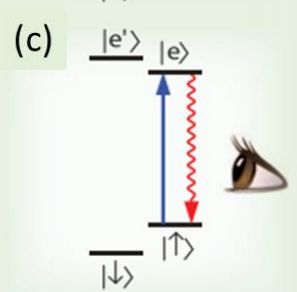

除了量子计算,离子阱还能用来进行量子模拟。2017 年,C. Monroe 组使用了 53 个离子实现了多体相互作用相位跃迁的观测,读出效率高达 99%,是迄今为止比特数目最多的高读出效率量子模拟器。

虽然不能单独控制单个比特的操作,但是这也证明了离子阱量子计算的巨大潜力。

对于两比特操控速度问题,2018 年,牛津大学的 Lucas 组通过改进激光脉冲,达到了最快 480 ns 的操作速度,展现了离子阱量子计算的丰富前景。

2015 年,马里兰大学和杜克大学联合成立了 IonQ 量子计算公司,计划在 2018 年将自己的量子计算机推向市场,这是继超导量子计算之后第二个能够面向公众的商用量子计算体系。;

国内:

清华大学的金奇奂研究组和中国科学技术大学的李传锋、黄运峰研究组已经实现了对一个离子的操控,做了一些量子模拟方面的工作;

清华大学计划在五年内实现单个离子阱中 15-20 个离子的相干操控,演示量子算法,说明中国也已经加入到了离子阱量子计算的竞赛中。

1.3.2 原子量子计算

原理:

不同于离子,原子不带电,原子之间没有库伦相互作用,因此可以非常紧密地连在一起而不相互影响。原子可以通过磁场或者光场来囚禁,用后者可以形成一维、二维甚至三维的原子阵列,如下图:

操作:

原子可以通过边带冷却的方式冷却到基态,然后同样可以通过激光对比特进行操控,比特的读出也类似于离子阱的方法。

缺点:

由于没有库伦相互作用,两比特操控在原子中较难实现,它们必须首先被激发到里德堡态,原子的能量升高,波函数展宽,再通过里德堡阻塞机制实现两比特操控。

评价:

尽管迄今为止,原子量子比特的两比特纠缠的保真度只有 75%,还远远落后于离子阱和超导比特,但是 2016 年一篇论文中,通过理论计算,经过波形修饰的两个原子量子比特的纠缠保真度可以达到 99.99%。

1.3.3 核自旋量子计算

1997 年,斯坦福大学的 Chuang 等人提出利用核磁共振来进行量子计算的实验。

之后,基于核自旋的量子计算迅速发展,Grover 搜索算法和七比特 Shor 算法相继在核自旋上实现。迄今为止,它的单比特和两比特保真度可以分别达到 99.97%和 99.5%。

原理:

这种方法一般是利用液体中分子的核自旋进行实验。

由于分子内部电子间复杂的排斥作用,不同的核自旋具有不同的共振频率,因而可以被单独操控;

不同的核自旋通过电子间接发生相互作用,可以进行两比特操作。

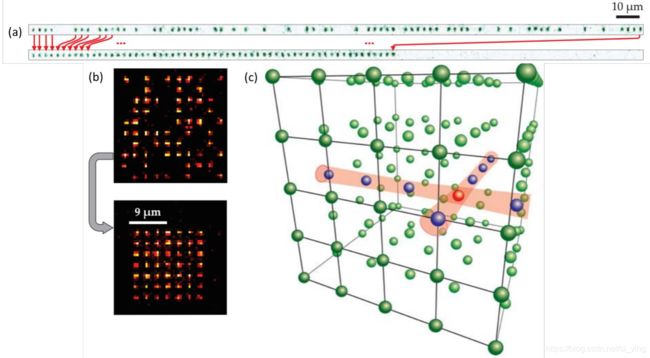

下图是一种用于核磁共振实验的分子,里面的两个 C 原子用 13C 标记,加上外面 5 个 F 原子,它们 7 个构成实验用的 7 个比特,表中显示了用于 Shor 算法的核磁共振实验的分子结构及相关参数,有比特频率、相干时间和相互作用能。

缺点:

依赖于分子结构,难以扩展,而且是利用多个分子的集体效应进行操控,初始化比较有难度。

研究进展:

国内从事核自旋量子计算实验的主要有清华大学的龙桂鲁课题组,2017 年,该课题组将核自旋量子计算连接到云端,向公众开放使用,该云服务包含四个量子比特,比特保真度超过 98%。

1.3.4 拓扑量子计算

实现原理:

利用的是一种叫做非阿贝尔任意子的准粒子。

实现过程:

· 首先要在某种系统中创造出一系列任意子-反任意子;

· 然后将这些任意子的两种熔接(fusion)结果作为量子比特的两个能级;

· 再利用编织(braiding)进行量子比特的操控;

· 最后通过测量任意子的熔接结果得到比特的末态。

优点:

这一系列操作对噪声和退相干都有极大地免疫,因为唯一改变量子态的机制就是随机产生的任意子-反任意子对干扰了比特的编织过程,但这种情况在低温下是非常罕见的,噪声和其他量子比特系统常见的电荷等相比,影响是非常小的。

研究进展:

现在国际上进行拓扑量子计算研究的实验组主要是荷兰代尔夫特理工大学的 Kouwenhoven研究组和丹麦哥本哈根大学的 Marcus 研究组。

从 2012 年首次在半导体-超导体异质结中观察到马约拉纳零模的特征开始,到 2018 年观察到量子化的电导平台,Kouwenhoven 研究组的实验已经让大多数科学家认同了可以在这种体系中产生马约拉纳费米子。不仅如此,进行拓扑量子计算的 Al-InSb 和 Al-InP 两种半导体-超导体耦合的纳米线阵列已经先后在实验中实现。未来将尝试进行编织实验,实现世界上第一个拓扑量子比特。

最近在量子反常霍尔绝缘体-超导结构中发现的一维马约拉纳模式也被认为可以用于拓扑量子计算,但是基于马约拉纳费米子进行的拓扑量子计算仍然不能满足单比特任意的旋转,它仍然需要和其他形式的量子比特互补或者通过某种方法进行近似的量子操作,不过,对高质量量子比特的追求仍然推动着科学家研究拓扑量子比特。

不同于其他美国巨头公司,微软公司在量子计算方面押注在拓扑量子计算,其与荷兰代尔夫特理工大学、丹麦哥本哈根大学、瑞士苏黎世理工大学、美国加州大学圣芭芭拉分校、普渡大学和马里兰大学在实验和理论上展开了广泛的合作,目标是五年内制备出世界上第一个拓扑量子比特,其拓扑保护的时间可长达一秒。

中国在拓扑量子计算方面也开始发力,2017 年 12 月 1 日,中国科学院拓扑量子计算卓越创新中心在中国科学院大学启动筹建,国科大卡弗里理论科学研究所所长张富春任中心负责人。未来几年可能是中国拓扑量子计算的高速发展期。

无论未来的量子计算发展情况如何,中国在各个量子计算方式上都进行了跟随式研究,这是我国现有的技术发展水平和国家实力的体现。随着国家对相关科研的进一步投入,相信未来在量子计算的实现方面,也可以领先于世界其他国家,实现弯道超车。

2 量子计算机硬件

量子芯片不等同于量子计算机,它仅仅是量子计算机中的一个核心结构。

量子计算机,是建立在量子芯片基础上的运算机器。其中最关键的两点是:

如何将运算任务转化为对量子芯片中量子比特的控制指令;

如何从量子芯片上量子比特的量子态中提取出运算结果。

除此以外,量子计算机需要提供能维持量子芯片运行的基本环境。

这些都需要特殊的硬件系统来实现,它们实现了量子计算机软件层到量子计算机芯片层的交互。

量子计算机硬件,主要包含两个部分:

· 量子芯片支持系统 —— 用于提供量子芯片所必需的运行环境;

· 量子计算机控制系统 —— 用于实现对量子芯片的控制,以完成运算过程并获得运算结果。

由于目前国际主流量子计算研发团队主要聚焦超导量子芯片与半导体量子芯片这两种体系,同时它们的量子计算机硬件有相当多的共性,因此以下将具体展开介绍这两种体系适用的量子计算机硬件。

2.1 量子芯片支持系统

超导量子芯片和半导体量子芯片对运行环境的需求类似,最基本的需求均为接近绝对零度的极低温环境。

稀释制冷机能够提供量子芯片所需的工作温度和环境。

在 2018 年 IBM’s inaugural Index 开发者大会上,IBM 展示的“50 位量子计算机原型机”,实际上就是维持 50 位量子芯片运行的稀释制冷机以及其内部的线路构造。

量子计算研究人员需要花费大量精力设计、改造、优化稀释制冷机内部的控制线路与屏蔽装置,以全面地抑制可能造成量子芯片性能下降的噪声因素。其中最主要的三点是热噪声、环境电磁辐射噪声以及控制线路带来的噪声。

- 抑制热噪声的主要方式

在稀释制冷机的基础上,为量子芯片设计能迅速带走热量的热沉装置,该装置需要兼容量子芯片的封装。下图是包含多种热沉结构的量子芯片封装照片,包含半导体量子芯片以及超导量子芯片,其中热沉主要使用了无氧紫铜材料。

- 抑制环境电磁辐射噪声

环境电磁辐射噪声是较难控制的环境干扰,其中又可以分为电场辐射以及磁场辐射。

工作于极低温环境的电磁屏蔽技术,一直是伴着量子计算研究人员的需求发展的。下图展示了伯克利大学 Sidiqqi 研究组使用的一种红外辐射屏蔽技术。他们设计了用于包裹量子芯片的屏蔽桶,并在桶的内壁使用了一种黑色的特殊涂层,用于增强对红外辐射的吸收。

- 抑制控制线路携带的噪声

控制线路携带的噪声主要也是由热效应引起的。

由于量子芯片工作环境的特殊性,从量子计算机控制系统发出的控制信号,要从稀释制冷机接入,经过漫长的低温线路,最后到达量子芯片。而热噪声近似和温度成正比,可想而知,从室温(约 300 K)传入的噪声,相比前面所说的量子比特能级对应的噪声温度(约 300 mK)相差了近 1000 倍。这么大的噪声如果直接到达维持在 10 mK 温度的量子芯片,则会直接破坏量子比特的量子相干性。

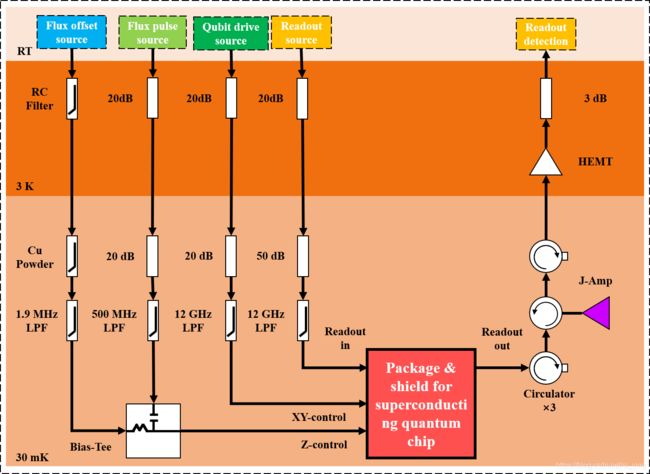

解决办法是尽可能地抑制从室温传入的信号,使从室温传入的噪声降至和量子芯片的工作温度一个级别。同时,我们还要通过各类特种低温滤波器,设法将除了控制信号以外的其他所有频段的无关信号一并滤除。下图是适用于超导量子芯片的量子芯片支持系统中极低温控制线路的设置。

2.2 量子计算机控制系统

量子计算机控制系统提供的是以下两个关键问题的解决方案:如何将运算任务转化为对量子芯片中量子比特的控制指令;

如何从量子芯片上量子比特的量子态中提取出运算结果。

其背后的基础是:

如何实施量子逻辑门操作;

如何实施量子比特读取。

- 如何实施量子逻辑门操作

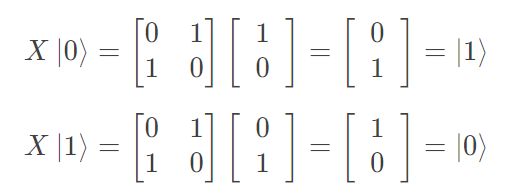

量子逻辑门操作的本质是使一组量子比特经过指定的受控量子演化过程。 例如,使得量子比特从基态(或者称 |0⟩ 态)到激发态(或者称 |1⟩ 态),可以借助一个单量子比特 X 门来实现。

实施这样的受控量子演化过程,需要借助精密的脉冲信号,通常可以使用高速任意波形发生器、商用微波源、混频线路等的组合来实现。当然,通过对光场、磁场甚至机械声波的调控,也可以在某些量子芯片体系中实现量子逻辑门操作。

商用设备的性能越高,越容易实现高保真度的量子逻辑门操作,当然,前提是量子比特的质量可靠。

- 如何实施量子比特读取

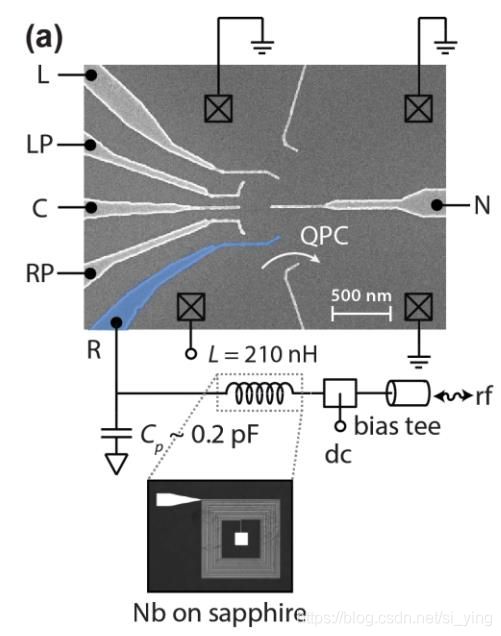

量子态的读取有多种方式,但考虑到需要读取量子芯片中某个或者某组量子比特的量子态,必须要使用一种称之为非破坏性测量的方式,以消除因测量导致的反作用。通常的方法是在量子比特结构旁边额外设计一个对量子态敏感的探测器,间接地通过探测探测器的响应来推测量子比特的量子态。下图是一个半导体量子芯片以及其探测器结构:

该探测器为一个 RF 探测器,通过该探测器的指定频率的微波信号会随着半导体量子芯片中电子状态变化,进而能从 RF 探测器的信号中计算出量子比特的量子态变化。捕获 RF 探测器的信号的装置通常为网络分析仪或者高速数字采集卡。

随着量子芯片集成度的提高,纯粹采用商用仪器搭建量子芯片的控制与读取系统的方法的弊端越来越大:成本昂贵,功能冗余,兼容性差,难以集成,并不满足未来量子计算机的发展需要。为量子计算机专门设计并研制适用的量子计算机控制系统,是明智的选择。

· 量子计算机控制系统的研究进展

2016 年,苏黎世仪器公司与代尔夫特理工大学研究团队成立的 QuTech 公司合作,研制了一套可用于 7 位超导量子芯片工作的集成量子芯片测控系统,包含最高可扩展至 64 通道的 AWG 以及同步的高速 ADC 采集通道。

2017 年底,是德科技自主研发了一套 100 通道的量子芯片测控系统,具备百 ps 级系统同步性能与百 ns 级量子芯片信号实时处理能力,最高可用于 20 位超导量子芯片完整运行。

2018 年,合肥本源量子计算科技有限责任公司也研制出 40 通道的量子芯片测控系统,可以应用于 8 位超导量子芯片或者 2 位半导体量子芯片,这是国内第一套完整的量子计算机控制系统。

除此之外,加州大学-圣塔芭芭拉分校、苏黎世理工学院、中国科学技术大学合肥微尺度物质科学国家实验室、Raytheon BBN Technologies 公司等都有自主研发的量子计算机控制系统或者模块。为了降低功耗,提高信号质量,代尔夫特理工大学和悉尼大学的研究团队开展了 4K 到 100mK 温度的极低温量子计算机控制系统的研究。

3 量子计算机

3.1 量子计算机整体架构

3.1.1 量子计算的定位:[异构计算]

量子计算领域属于一个新兴高速发展的领域,在近二十年间,不论是量子算法的研究,还是量子芯片的研发均取得了巨大的进展。

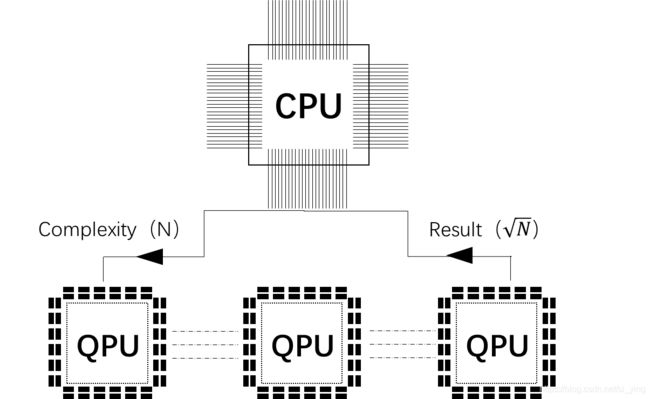

由于量子计算的理论研究有限,目前所说的量子计算机并非是一个可独立完成计算任务的设备,而是一个可以对特定问题有指数级别加速的协处理器。相应的,目前所说的量子计算,本质上来说是一种异构运算,即在经典计算机执行计算任务的同时,将需要加速的程序在量子芯片上执行,如下图所示:

3.1.2 量子程序代码构成:宿主代码 + 设备代码

量子计算的程序代码实际执行中分为两种:

-

运行在 CPU 上的宿主代码(Host code)—— 主要用于执行不需要加速的任务,并为需要加速的任务提供需要的数据;

-

运行在量子芯片上的设备代码(Device code)—— 主要用于描述量子线路,控制量子程序在量子芯片上的执行顺序,以及数据的传输。

不同类型的代码由于其运行的物理位置不同,编译方式和访问的资源均不同,这跟英伟达公司推出的用 GPU 解决复杂的计算问题的并行计算架构 CUDA 非常类似。

以下所提及的量子程序,指的是 Device code。

3.2 量子程序架构(设备代码的架构)

3.2.1 量子高级语言

与经典计算机语言类似,描述量子程序的语言也有高级语言与低级语言之分。

量子高级语言,类似于经典计算机语言中 C++。在描述量子线路时,不需要考虑量子芯片的底层物理实现,包括可执行量子逻辑门的种类,量子比特的连通性等,这就像一个经典的程序设计师并不需要考虑底层的执行芯片是 x86 架构,还是 RISC 架构一样。

QPanda,QRunes 均属于量子高级语言。

量子高级语言的作用:

用于描述量子线路的逻辑门构成、量子程序段之间的执行顺序,如 Qif,QWhile 等,以及内存之间的通信。

3.2.2 量子汇编语言的编译原则

量子高级语言会根据底层芯片的特点,通过量子程序编译器,编译为量子汇编语言。

量子程序编译器一般会考虑两个方面:

- 量子芯片可执行的量子逻辑门种类

- 量子比特的连通性

不可直接执行的量子比特逻辑门拆分

量子芯片提供的可直接执行的逻辑门是完备的,即可以表征所有的量子比特逻辑门,因此,如果量子高级语言描述的量子程序中包含了量子芯片不可直接执行的量子逻辑门,量子程序编译器会根据量子芯片提供的量子逻辑门将其转化为可执行量子逻辑门构成的序列。

量子比特连通性与不连通门的转换

相同数量的量子比特对于不同的量子芯片结构,可执行两量子比特逻辑门的量子比特对可能完全不同。

目前常见的量子芯片结构有链式结构,十字结构,以及全连通结构。

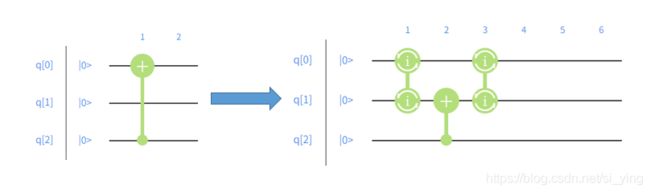

如果量子高级语言描述的量子程序中包含量子芯片不可直接执行的两量子比特逻辑门,量子程序编译器会根据量子芯片的连通性,利用交换门和可执行的两比特门的序列,取代量子程序中的两量子比特逻辑门。

例如下图:

左边是一个三量子比特的链式结构量子芯片,可执行两量子比特逻辑门的量子比特对有 { {1,2},{2,3}},图中显示的 CNOT 1,3 对于此量子芯片是不可执行的逻辑门,因为对于链式结构,量子比特成链状排布,每个量子比特只能与其相邻的两个量子比特执行两量子比特逻辑门。因此,我们可以先用 SWAP 1,2 进行交换、然后进行操作 CNOT 2,3、最后再用 SWAP1,2 换回原来的位置,这样构成的量子逻辑门序列就可以取代在原来结构中的 CNOT1,3。

3.2.3 量子程序的可执行文件

对于经典程序来说,汇编语言转化为计算机可直接执行二进制文件,即可被经典计算机执行;而量子芯片可直接执行的文件并非一串 0 1 组合的二进制文件,而是由测控设备产生的精密的脉冲模拟信号,因此对于量子汇编语言,应该转化成测控设备所能执行的文件。

此文件中不仅包含着每个量子比特逻辑门的脉冲波形,还需要包含波形的执行顺序,根据波形执行顺序的表征形式不同,量子计算硬件架构可细分为两类。

-

顺序执行的传统量子体系结构的可执行文件:量子程序的整段波形文件

在传统的量子体系结构中,波形执行顺序体现在波形文件中,即编译器将量子汇编程序中的量子比特逻辑门的波形,按照执行顺序拼接为一个整体的波形,并将此波形以二进制文件的形式存放至测控设备的内存中。

优点:

测控设备可以从内存中直接读取波形,并施加到量子芯片上,延时极短,执行效率很高;

缺点:

但由于上位机与测控设备之间的通信时间很长,远大于量子比特的退相干时间,即在量子比特完成测量发送至上位机,以及上位机根据测量结果将后续要执行的波形文件发送至测控设备内存的期间,量子比特已经退相干,无法继续执行量子比特逻辑门。

因此,这种架构只能运行顺序执行的上位机发送的波形文件,在执行期间不可改变波形的执行顺序,进而无法执行包含基于测量结果的跳转量子程序。

改进:

将量子程序中可能执行的量子程序段的波形,全部上传至测控设备的内存中,当测量设备得到量子比特的测量结果时,根据测量结果决定接下来输出的波形在内存中的地址,且整个反馈过程的延时远小于量子比特的退相干时间。 -

增强扩展性的新量子体系结构

增强扩展性的新量子体系结构的可执行文件构成:所有逻辑门的波形文件 + 微处理器程序

为了降低任意波形发生器的内存开销,增加系统的可扩展性,目前已有科研团队提出另一种量子计算机架构:上位机-微处理器-测控设备-量子芯片架构。

优点:

测控设备无需存放量子程序对应的所有波形,大大减少了内存开销;

缺点:

通过执行微处理器程序控制测控设备,对微处理器的执行速度要求较高。