基于PYNQ-Z2蜂鸟E203移植完全攻略

基于PYNQ-Z2蜂鸟E203移植完全攻略

Author:蛋糕店老板

Special thanks to @雪天鱼

参考:..\e200_opensource-master\boards\nucleikit\蜂鸟FPGA开发板原理图.pdf

..\e200_opensource-master\boards\nucleikit\蜂鸟FPGA开发板和JTAG调试器介绍.pdf

..\e200_opensource-master\boards\nucleikit\蜂鸟FPGA开发板约束文件.pdf

PYNQz2原理图:

..\pynq\TUL_PYNQ_Schematic_R12.pdf

- 建立频率计

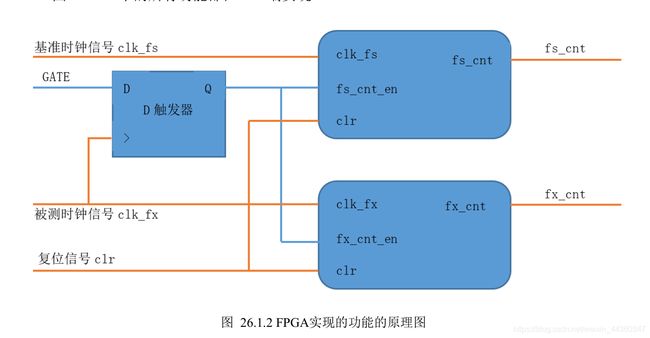

目的:制作频率计是为了监测板上时钟是否真正得到了16Mhz与实时时钟32.768KHz

A.设计指标

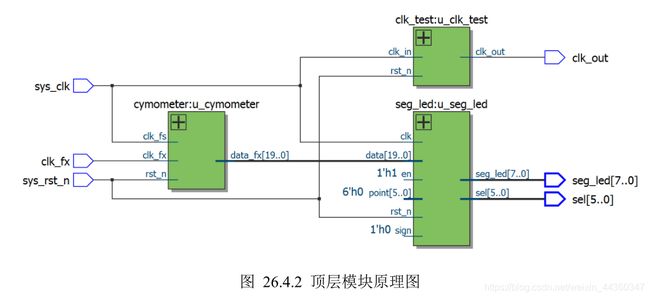

- 首先参考:..\文档\新起点FPGA开发指南_V1.3.pdf第26章

- 测量范围是100hz到50.0000Mhz(因为clk_fs 的限制)

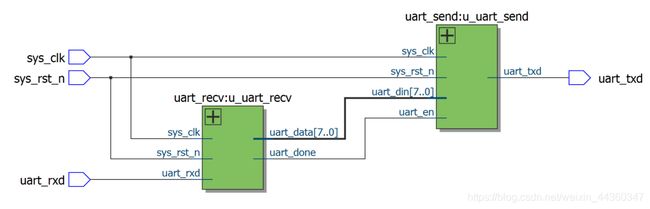

- 频率计还可通过串口在电脑终端显示

过程:

现在开始开发串口:

详细开发流程请见连接:

..\pynq\cymometer\doc\频率计.rtf

工程地址:

..\pynq\tradition_cymometer

..\pynq\cymometer

实际上我用的是tradition_cymometer这个工程,而不是等精度测量法的工程,传统频率计在某种程度上来说好用。

- 在pynq上进行时钟的测试,将分频后的时钟引出端口,通过频率计进行测试

- 约束时钟管脚

首先看时钟管脚的绑定,MCU SoC 的两个输入时钟输入在nuclei-kit上分别按照如下方式产生:

- 低速的实时时钟直接由 FPGA 开发板上的 32.768KHz 时钟源输入。

- 高速时钟由 FPGA 开发板上的 100MHz 时钟经过 FPGA 内部 PLL 降频而得(16MHz) [1]

我的粉色PYNQ-z2只有125Mhz时钟

Pynqz2 User manual原文描述:

The PYNQ-Z2 also has an external 125 MHz reference clock connected to pin H16 of the PL. The external reference clock allows the PL to be used independently of the PS.

Figure 6.1(上图) outlines the clocking scheme used on the PYNQ-Z2. Note that the reference clock output from the Ethernet PHY(以太网物理层) is used as the 125 MHz reference clock to the PL. When the PHYRSTB signal is driven low, the Ethernet PHY (U5) is held in reset disabling the CLK125.

RTC和16Mhz时钟分频测试通过。工程连接:..\pynq\tradition_cymometer

- 注意事项

1.复位rst_n要约束到switch上,方便复位。

2.代码逻辑一定要正确,尤其是内部计数器位数。

- 测量结果记录

对RTC测量值:32.9Khz。

对16M测量值:复位后大概稳定在17Mhz。

- 对e203进行约束和移植

- 复位约束

复位管脚

nuclei-kit它的rtl顶层模块有两个复位信号,分别是 fpga_rst 和 mcu_rst,即FPGA开发板自身的复位和为MCU设置的复位,这两个复位通过一个与操作生成一个为SoC使用的复位信号,即SoC复位的条件是这两个复位信号至少有一个生效。由于这两个复位信号都是低电平有效,故分别绑定到达芬奇开发板上的 RESET 和 KEY0 按键即可,其中RESET 是FPGA自身的复位键,而KEY0 是为MUC设置的复位键(达芬奇开发板上的按键都是按下去为0,松开为1,满足低电平有效的要求)【2】

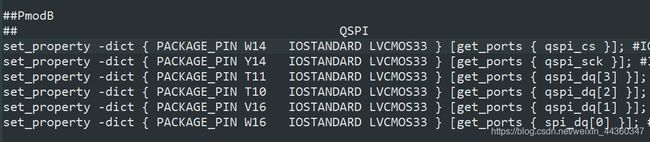

- QSPI接口

蜂鸟E203 有三个qspi接口,分别为QSPI0、QSPI1、QSPI2,其中QSPI0专门是为外部FLASH准备的,而其余两个都是通过GPIO口复用进行使用。所以rtl顶层需要绑定的是专为外部FLASH准备的QSPI接口,目前由于没有外部FLASH,所以先绑定到达芬奇开发板上的空闲IO口上。【3】

我打算将外部flash绑定在空闲IO上,板载的flash未给可绑定接口

- PMU管脚

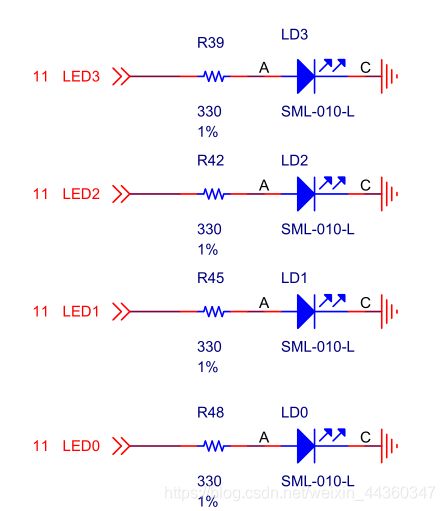

PMU用于控制主域电源,可以使主域被置于断电状态以节省功耗,或者重新唤醒。pmu_paden 用于MCU的电源指示,pmu_padrst 指示MCU的复位,这两个可以接达芬奇开发板上的LED,而mcu_wakeup 用于唤醒,低电平有效,可以接达芬奇开发板的按键。【4】

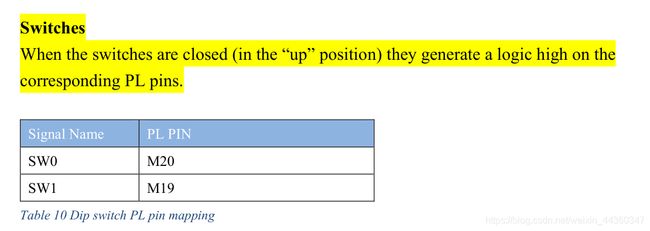

图:Switch up:高电平 Switch down:低电平

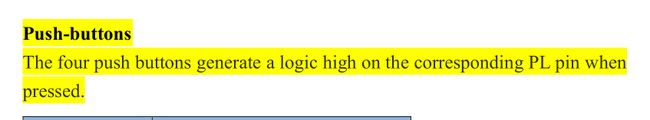

图:Button pressed:高电平

总结:

- switch 没被推高就是低电平,button未触动是低电平。

- 保密需要略

- 保密需要略

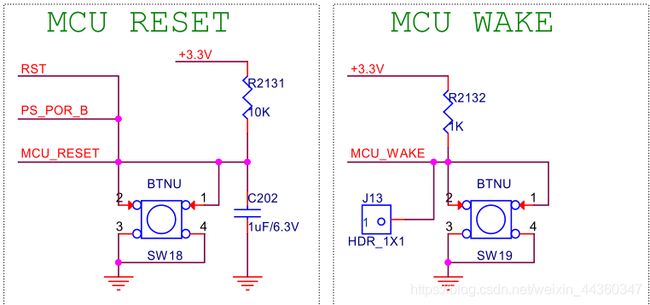

- fpga_rst不再需要了,原因如下:

- 板载按键(button)未触动是低电平

- 开关(switch)只有两个,且已被占用

- 观察顶层文件可知,fpga_rst,mcu_rst的存在二选一即可

图: nucleikit开发板的reset和wake

所以:

保密需要略

- 其他管脚:

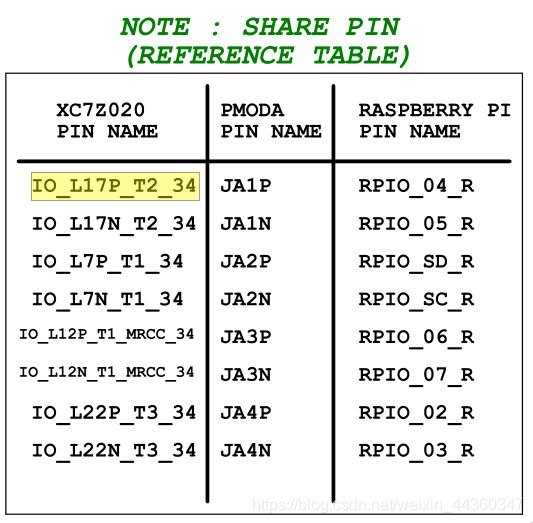

注意在pynq上有部分管脚是重复的:具体是PMODA和Raspberry的部分管脚。在我的xdc中pmodA已经不能再被约束了。

供hello world测试用的约束文件:

..\pynq\pynq_z2约束文件备份2月6日.xdc

在约束GPIO时要避开

- 我在约束时加入下面四句话

保密需要略

CLOCK_DEDICATED_ROUTE的用法:

https://www.cnblogs.com/xuzhi-fpga/p/3507403.html

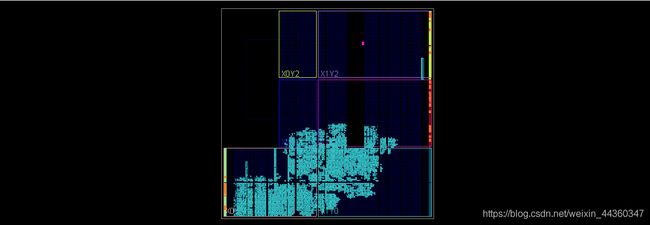

综合实现:

目前遗留的问题:

如何解决:

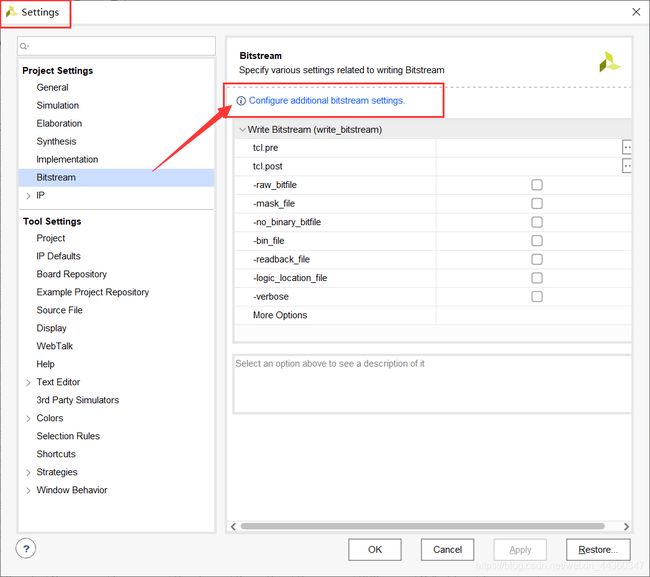

需要在完成Implementation 后,打开schematic后,在Project Manager下点击setting,跳出

至于为什么要打开schematic,如果没有打开,则在相应位置没有蓝色的那句话

这里遗留一个问题:zynq即pynq如何烧写mcs程序到flash中?

参考文献:

https://bestfpga.blog.csdn.net/article/details/81812288?utm_medium=distribute.pc_relevant_t0.none-task-blog-BlogCommendFromBaidu-1.control&depth_1-utm_source=distribute.pc_relevant_t0.none-task-blog-BlogCommendFromBaidu-1.control

其他文章连接:

FPGA 的I/O BANK介绍

- https://blog.csdn.net/wordwarwordwar/article/details/79779401

FPGA配置及文件生成烧写

- https://www.pianshen.com/article/21811956062/

- 工具链开发

目前两个问题:

- 如何下载程序?

- 下载程序到了哪里?

- elf文件是什么

《RISC-V嵌入式开发快速入门》第8.4章

- 如何写上电引导程序

底层文件详细分析.docx

- 什么是物理地址和虚拟地址

物理地址虚拟地址.docx

- 如何下载程序

调试riscv程序指南.docx

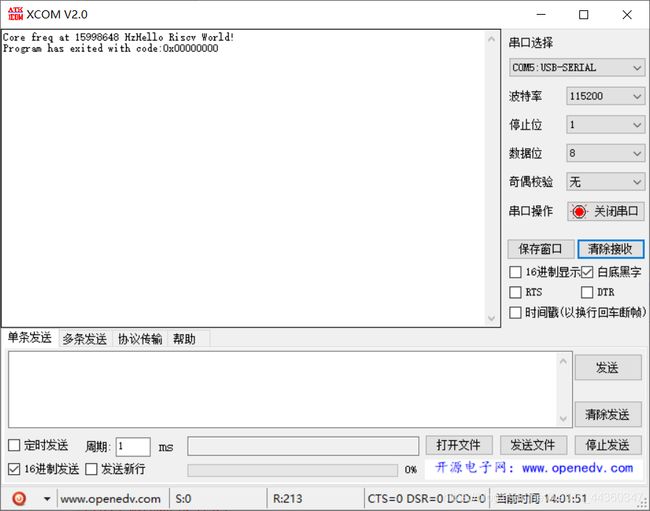

- JTAG下载程序Hello RiscV World !

vivado工程链接:..\pynq\hbird_e203备份

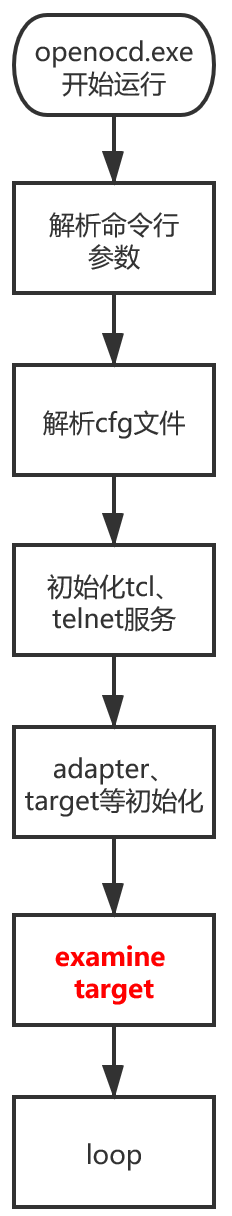

openocd启动时的主要流程如图18所示

- 如何调试程序+常见错误类型?

详情参见:调试riscv程序指南.docx

- 引脚连接引脚?

保密需要略

- 展示结果

源程序:

// See LICENSE for license details.

#include

int main(void)

{

printf("Hello Riscv World!" "\n");

return 0;

}

- 附录 引用文献

保密需要略

https://www.bilibili.com/video/BV1jb411g7fC/?spm_id_from=333.788.videocard.0