关于inputdelay和outputdelay的学习笔记

一、inputdelay

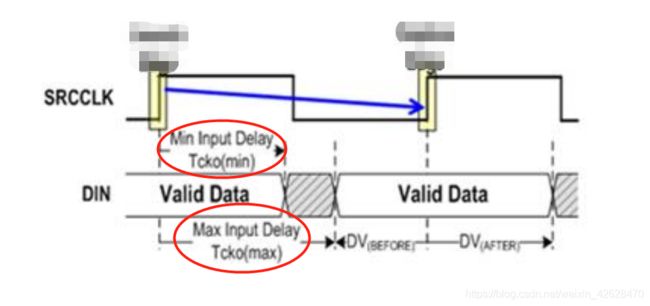

首先要知道inputdelay约束的是什么?inputdelay就是要告诉fpga,以fpga时钟输入引脚为参考点,时钟采样沿到数据有效的max和min延迟。如下图的红圈所示。

对于inputdelay可以分为下图中的几个类型。

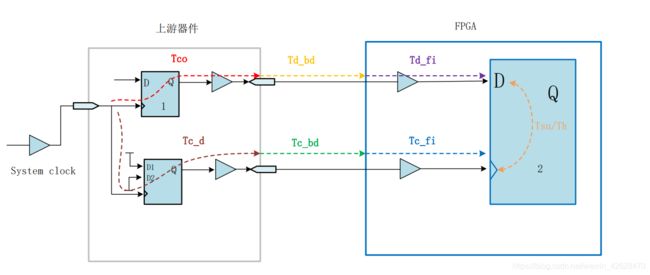

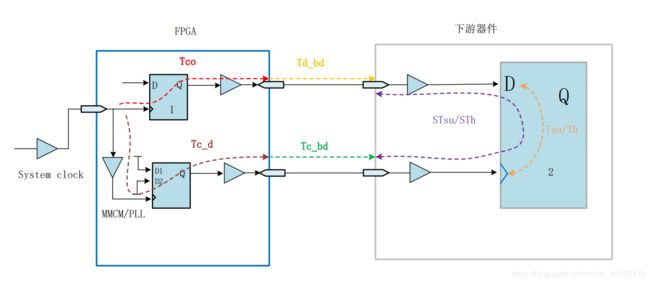

因为现在主要用到的是源同步,中心对齐。所以只对这两类进行了学习。下图是源同步接口类型的inputdelay分析模型。

我们需要知道inputdelay中约束的max和min是由上游器件的Tco,Tc_d,布线延迟Td_bd,Tc_bd决定的。并不关fpga什么事情。inputdelay约束要做的就是告诉fpga输入时钟和数据的关系。(如果Td_bd,Tc_bd为0的话,那么上游器件的时钟和数据输出是什么关系,进入fpga的就是什么关系)。

源同步SDR类型接口

对源同步接口进行 Input 约束可以根据不同的已知条件,选用不同的约束方式。有两种方式。

1.已经知道游器件的Tco,Tc_d,布线延迟Td_bd,Tc_bd。

dmax = (Td_bdmax + Tcomax)-(Tc_d + Tc_bd)

dmin = (Tco min+ Td_bd min) – (Tc_d + Tc_bd)

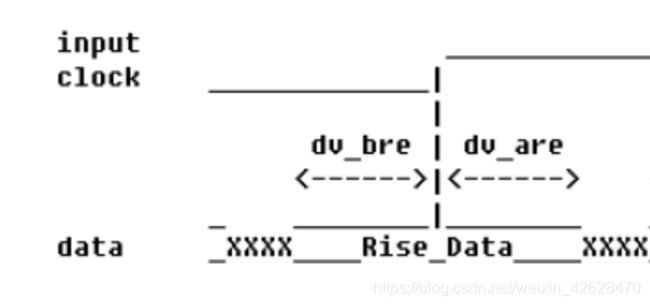

2. FPGA 作为输入接口时,数据有效窗口是已知条件。如下图所示

那么为了满足dv_bre 和 dv_are ,所以

dmax = T - dv_bre;

dmin = dv_are;

如下图所示,

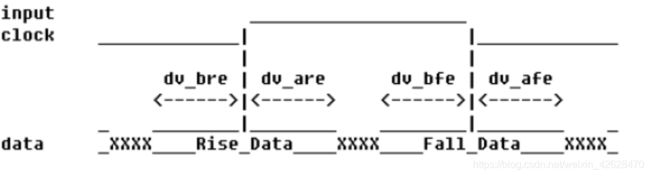

DDR 源同步中心对齐输入接口

模型如下图所示,

那么为了满足上升沿和下降沿的dv_bre , dv_are,

outputdelay的分析也有两种方法。

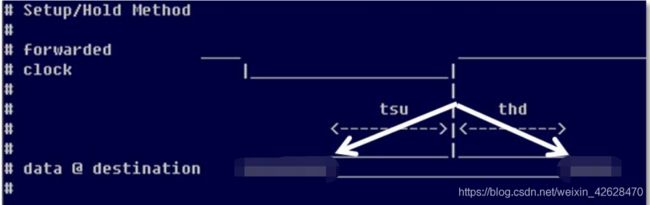

1.方法一我们称作 Setup/Hold Based Method,仅需要了解下游 器件用来锁存数据的触发器的 Tsu 与 Th 值与系统板级的延时便可以设置。

先上公式dmax = 最大布线延迟 + 下游器件的Tsu;

dmin = 最小布线延迟 - 下游器件的Thd。

我刚开始就很疑惑公式是怎么来的,估计大家刚学也是这样。下面就按照我的理解来说一下。

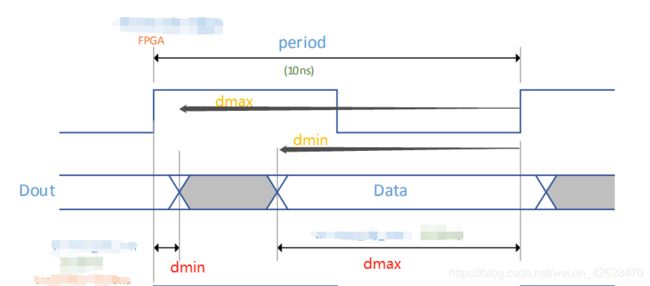

当最大布线延迟为0的时候,fpga的数据和时钟时钟输出关系只要满足下游器件的保持建立时间就可以。如下图所示。

这里先不考虑tsu和thd加起来是不是等于一个时钟周期。就只知道fpga输出数据提前时钟采样沿的时间至少有tsu这么大,然后采样沿过后数据保持时间至少有Tth这么大。

下面先分析建立时间

因为布线延迟为0,所以可以认为fpga一输出时钟上升沿(对于fpga来说就是发射沿)下游器件能无延时的收到时钟上升沿(对于下游器件来说就是采样沿),那么这时候fpga输出的数据只要提前时钟上升沿tsu的时间发送,这样到达下游器件引脚处的数据也是提前时钟上升沿tsu的。

假如布线延时不为0,这是fpga输出的时钟还是可以无延迟到下游器件(这里是相对于数据延时来说的),但由于数据有延迟,那么下游器件的采样沿到来时之前,fpga输出的数据不能提前tsu个时间来到下游器件的输入,这样就不满足下游器件的建立时间了(最糟糕的是游器件的采样时钟来了,数据还没有来)。解决办法就是,本来fpga输出的数据是提前时钟tsu个时间,现在就需要在tsu的基础上加上布线延迟,也就是数据提前时钟(tsu+布线延迟)的时间。当加上去的是最大布线延时时,这时较小的布线延时情况也是能满足下游器件的建立时间的。

所以公式dmax = 最大布线延迟 + 下游器件的Tsu, 用来分析建立时间。

然后分析保持时间

如果布线延时为0的话,在fpga输出时钟发射沿后数据保持了多长时间,到达下游器件时的数据就会在时钟采样沿之后保持多长的时间。

如果布线延迟不为0的话,设fpga输出时钟发射沿后数据保持的时间为d,那么只要这个d+布线延迟 = 下游器件的保持时间就可以满足下游器件的保持时序要求。因为fpga输出的数据在时钟发射沿之后d时间结束了以后,数据还需要经过布线延迟这段时间。所以按最小的布线延时的情况下算出这个d,这时较大的布线延迟情况也是能满足下游器件的保持时间的。

所示公式dmin = 最小布线延迟 - 下游器件的Thd,用来分析保持时间。

当布线延时小于下游器件的保持时间时,dmax、dmin就会是前面图中红色的情况; 当布线延时大于下游器件的保持时间时,dmax、dmin就会是前面图中黄色色的情况

2.方法二称作 Skew Based Method, 此时需要了解 FPGA 送出的数据相对于时钟沿的关系,根据 Skew 的大小和时钟频率来计算如何设置 Output 约束。

多数情况我们不知道目标芯片 setup 门限值或者 hold 的门限值,我们需要假设输出信号的状态也就是时钟与数据的关系,这里假设的值是 SKEW, 假设 SKEW 的目的是让综合工具知道输出的时钟采样沿不能落在 SKEW 的区 间,如果落在 SKEW 区间就出现时序违例,这样我们可以假定 SKEW 的大小来 调节时钟与数据的关系。

分析方法跟第一种一样的。

最后说下自己对outputdelay的理解:只要fpga的输出数据比时钟提前dmax的时间,理论上fpga输出的数据只需要足够存在dmax-dmin的时间就可以满足下游器件的建立和保持时间,但是实际上fpga内部存器输出的数据一定是存在一个周期。不过就算一个周期大于dmax-dmin也不会影响下游器件的建立和保持时间的。所以时序不违例的要点只需要满足fpga输出数据提前时钟dmax就可以。只不过在约束上还是要加上dmin的。