1. 亚稳态

亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。

发生情况

在跨时钟域传输或者异步信号采集时可能发生。

- 跨时钟域信号传输

由于源寄存器时钟和目的寄存器时钟相移未知,所以源寄存器数据发出数据,数据可能在任何时间到达异步时钟域的目的寄存器,所以无法保证满足目的寄存器和的要求; - 异步信号采集

由于异步信号可以在任意时间点到达目的寄存器,所以也无法保证满足目的寄存器和的要求;复位信号一般都是异步,常常会产生亚稳态。

如何避免

发生概率

概率 = (建立时间 + 保持时间)/ 采集时钟周期

可见随着clk频率的增加,亚稳态发生的几率是增加。

串扰

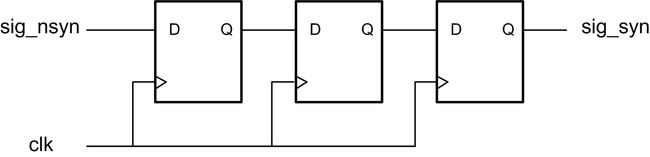

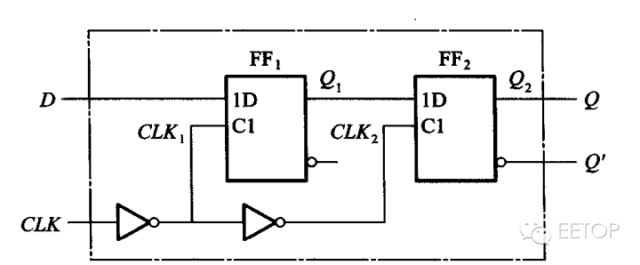

一般使用异步信号时,好的设计会采用多级D触发器级联,来同步异步信号,如下图所示。

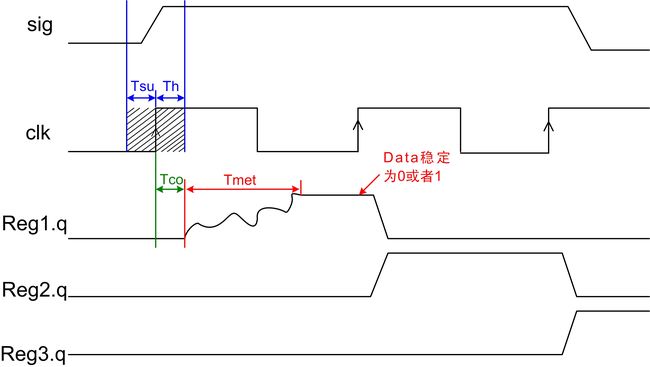

这样即使第一级产生亚稳态,第二级也有很大概率稳定输出。下图就是当第一个寄存器发生亚稳态后,经过Tmet的振荡稳定后,第二级寄存器能采集到一个稳定的值。

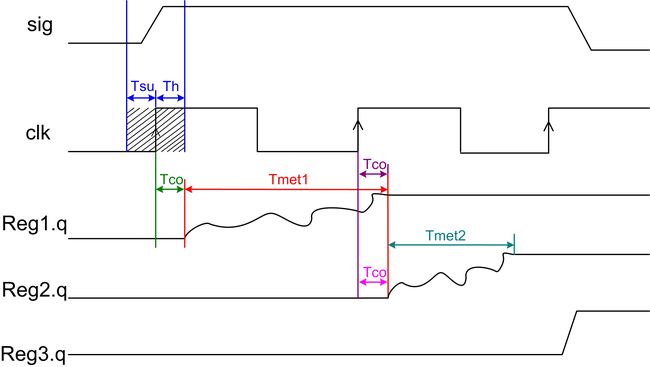

但是当Tmet时间长到大于一个采集周期后,那第二级寄存器就会采集到亚稳态,如下图所示。亚稳态产生了串扰,从第一级寄存器传到了第二级寄存器,同样也可能从第二级寄存器串扰到第三级寄存器。

两级触发器可防止亚稳态传播的原理

假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。有效的条件:

第一级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 <= 时钟周期

更确切地说,输入脉冲宽度必须大于同步时钟周期与第一级触发器所需的保持时间之和。最保险的脉冲宽度是两倍同步时钟周期。所以,这样的同步电路对于从较慢的时钟域来的异步信号进入较快的时钟域比较有效,对于进入一个较慢的时钟域,则没有作用。

常用的消除亚稳态

- 相位控制,一个时钟由DLL或PLL产生,周期不同,相位相同;

- 采用FIFO对跨时钟域数据通信进行缓冲设计;

- 打两拍技术,就是上面触发器级联;

- 降低时钟频率,根据前面的概率计算

2. 锁存器和触发器

- 锁存器 latch

透明,电平触发。

在不锁存数据时,输出端的信号随输入信号变化;锁存时,输入信号不起作用。不能过滤毛刺,避免产生锁存器很重要。 - 触发器 flip-flop

不透明,边沿触发。

可由锁存器和反相器构成。输入变化时,输出不同时变化。

3. 系统最高频率计算

:触发器中数据从输入端到输出端的延时,

:组合逻辑的延时

:建立时间

则为了确保数据能被下一级触发器接收到,在满足下一级触发器的建立时间之前,不能来新的时钟沿,所以时钟有如下约束:

即Tmin =Tco+Tdelay+Tsetup,最快的时钟频率Fmax =1/Tmin。

4. 锁相环

顾名思义,就是锁定相位的环路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位。

- PLL:Phase lock loop

又称模拟锁相环,由鉴相器、环路滤波器和压控振荡器组成,鉴相器用来鉴别输入信号Ui与输出信号Uo之间的相位差,并输出误差电压Ud。Ud中的噪声和干扰成分被低通性质的环路滤波器滤除。形成压控振荡器(Vco)的控制电压Uc,Uc作用于压控振荡器的结果是把它的输出震荡频率fo拉向环路输入信号频率fi,当二者相等时,环路被锁定,称为入锁。PLL并不是直接对晶振进行倍频,而是将频率稳定的晶振作为基准信号,与PLL内部振荡电路生成的信号分频后进行比较,使PLL输出的信号频率稳定 - DLL:Delay Lock Loop

又称数字锁相环,基于数字抽样方式,在输入时钟和反馈时钟之间插入延迟,使输入时钟和反馈时钟的上升沿一致来实现的。

上图是两者的原理,两者功能上都可以实现倍频、分频、占空比调整,但是PLL调节范围更大。DLL数字电路实现,抗噪声,低功耗,抗抖动,移植性好。

5. LUT查找表

查找表(look-up-table)简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有 4位地址线的16x1的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可

6. 常用的逻辑电平

常用逻辑电平:12V,5V,3.3V

常用逻辑电平:TTL、CMOS、LVTTL、LVCMOS、ECL(Emitter Coupled Logic)、PECL(Pseudo/Positive Emitter Coupled Logic)、LVDS(Low Voltage Differential Signaling)、GTL(Gunning Transceiver Logic)、BTL(Backplane Transceiver Logic)、ETL(enhanced transceiver logic)、GTLP(Gunning Transceiver Logic Plus);RS232、RS422、RS485(12V,5V,3.3V)

TTL和CMOS 不可以直接互连,由于TTL是在0.3-3.6V之间,而CMOS则是有在12V的有在5V的。CMOS输出接到TTL是可以直接互连。TTL接到 CMOS需要在输出端口加一上拉电阻接到5V或者12V。用CMOS可直接驱动TTL;加上拉电阻后,TTL可驱动CMOS.

7. MOORE 与 MEELEY

- Moore 状态机的输出仅与当前状态值有关, 且只在时钟边沿到来时才会有状态变化。

- Mealy 状态机的输出不仅与当前状态值有关, 而且与当前输入值有关。

8. STA与DTA

- 静态时序分析 STA

静态时序分析是采用穷尽分析方法来提取出整个电路存在的所有时序路径,计算信号在这些路径上的传播延时,检查信号的建立和保持时间是否满足时序要求,通过对最大路径延时和最小路径延时的分析,找出违背时序约束的错误。

优点:

1.它不需要输入向量就能穷尽所有的路径;

2.运行速度很快、占用内存较少,不仅可以对芯片设计进行全面的时序功能检查,而且还可利用时序分析的结果来优化设计。

缺点:

- 静态时序分析不能检验设计功能

- 静态时序分析只能对同步电路进行分析,而不能对异步电路进行时序分析。

- 动态时序分析 DTA

动态时序模拟就是通常的仿真,是所有的输入信号都会给一个不同时刻的激励,在testbech(.sp或者.v)中设置一段仿真时间,最后对仿真结果进行时序和功能分析。 这里的仿真可以是门级或者晶体管级,包括spice格式和RTL格式的网表。

优点:

比较精确,而且同静态时序相比较,它适用于更多的设计类型。

缺点:

1.分析的速度比较慢

2.关键路径无法检查全,里面可能有fail的path,芯片流片出来无法工作

关键路径就是输入到输出延时最大的路径

8. MOS管

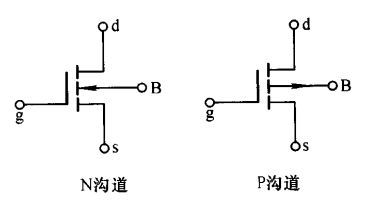

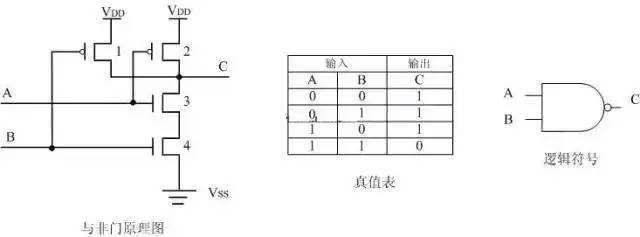

用MOS管搭与非门,上面画的是电子的流向,P沟道是G低导通。

9. 可编程逻辑器件

PAL,PLA,GAL,CPLD,FPGA

10. 建立时间和保持时间

建立时间(setup time)

触发器在时钟沿到来之前,其数据的输入端的数据必须保持不变的时间;建立时间决定了该触发器之间的组合逻辑的最大延迟。保持时间(hold time)

触发器在时钟沿到来之后,其数据输入端的数据必须保持不变的时间;保持时间决定了该触发器之间的组合逻辑的最小延迟。

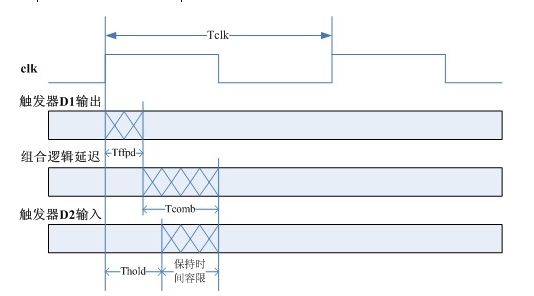

Tffpd:触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化并且稳定,也可以理解为前面的Tco。

Tcomb:触发器的输出经过组合逻辑所需要的时间,也就是前面的组合逻辑延迟Tdelay。

Tsetup:建立时间

Thold:保持时间

Tclk:时钟周期

建立时间容限:相当于保护时间,这里要求建立时间容限大于等于0。

保持时间容限:保持时间容限也要求大于等于0。

- 恢复时间

复位、清零信号在时钟有效沿之前保持的最小时间长度- 移除时间

复位、清零信号在时钟有效沿之后保持的最小时间长度

11. 用传输门和反相器器搭一个边沿触发器(DFF)

12. OTP、MASK、FLASH

MCU按其存储器类型可分为MASK(掩模)ROM、OTP(一次性可编程)ROM、FLASHROM等类型。

- MASKROM

掩模片,价格便宜,但程序在出厂时已经固化,适合程序固定不变的应用场合; - FALSHROM

程序可以反复擦写,灵活性很强,但价格较高,适合对价格不敏感的应用场合或做开发用途 - OTP ROM

One Time Programmable,仅能编程一次,价格介于前两者之间,适合既要求一定灵活性,又要求低成本的应用场合

13. 天线效应

在芯片生产过程中,暴露的金属线或者多晶硅(polysilicon)等导体,就象是一根根天线,会收集电荷(如等离子刻蚀产生的带电粒子)导致电位升高。天线越长,收集的电荷也就越多,电压就越高。若这片导体碰巧只接了MOS 的栅,那么高电压就可能把薄栅氧化层击穿,使电路失效。

随着工艺技术的发展,栅的尺寸越来越小,金属的层数越来越多,发生天线效应的可能性就越大。

14. 异步FIFO

FIFO是一种现先进先出的数据缓冲器,特点是没有外部的读写地址。根据满和空信号设计写使能和读使能来写/读FIFO,当FIFO满的时候不可以往里面写、当FIFO空的时候不能读数据。

异步FIFO常用于跨时钟域传输。

常见信号

- wfull: 满标志, 表示FIFO已经满,不能再写入数据。

- rempty:空标志,表示FIFO已经空,不能再读取数据。

- wclk: 写时钟

- rclk: 读时钟

- winc: 写使能

- rinc: 读使能

- wdata:写数据

- rdata: 读数据

- wrst_n: 写复位

- rrst_n:读复位

空满标志产生

- 判空:读指针追上写指针的时候,两者相等,为空。

- 判满:写指针追上读指针的时候,两者相等,为满。

如何判断谁追上谁

表示读写指针的数据位宽上再加1位来区分是满还是空。比如FIFO的深度位8,那么需要3位二进制数来表地址,则需要再最高之前再加一位,变成4位。一开始读写都是0000,FIFO为空。当写指针增加并越过最后一个存储单元的时候,就将这个最高位取反,变成1000。这时是写地址追上了读地址,FIFO为满。同理,当读地址越过最后一个存储单元的时候把读地址的最高位也取反。

当最高位相同,并且剩下的位也相同时,FIFO为空;

当最高位不同,并且剩下的位相同时,FIFO为满。

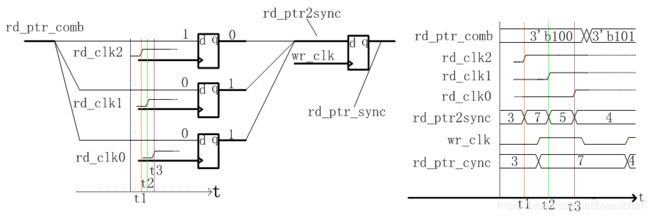

异步时钟下判断空满

需要将读写指针进行同步化才可以进行判断。通过两级D触发器。

- 在判断空的时候,需要将写地址同步到读时钟域下进行判断。

- 在判断满的时候,需要将读时钟域中的读指针同步到写时钟域进行判断。

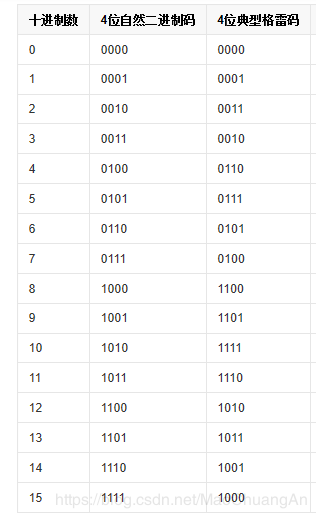

格雷码表示地址

将读指针发送到写时钟域下进行同步时,如果仍然采用自然二进制,那么就会面临地址同时有多位变化的情况。因此采用格雷码来表示地址,每次只改变一位。

格雷码与二进制转换

- 二进制转格雷码

gray = (bin >> 1) ^ bin异或 - 格雷码转二进制

格雷码记法:

- 0位:0 1 1 0重复

- 1位:00 11 11 00重复

- 2位:0000 1111 1111 0000重复

- 3位:00000000 11111111 11111111 00000000

格雷码判空满

- 判满:格雷码的最高位和次高为不同,剩下的都同,就是满。

- 判空:格雷码完全相同,就是空。

可以参考下面图片,隔8个为满,相同为空。可见前两位不同,其余相同就是满。

模块设计

如上图所示的同步模块synchronize to write clk,其作用是把读时钟域的读指针rd_ptr采集到写时钟(wr_clk)域,然后和写指针wr_ptr进行比较从而产生或撤消写满标志位wr_full;类似地,同步模块synchronize to read clk的作用是把写时钟域的写指针wr_ptr采集到读时钟域,然后和读指针rd_ptr进行比较从而产生或撤消读空标志位rd_empty。

另外还有写指针wr_ptr和写满标志位wr_full产生模块,读指针rd_ptr和读空标志位rd_empty产生模块,以及双端口存储RAM模块。

代码实现

代码搬运于网络

// 顶层模块

module AsyncFIFO#(

parameter ADDR_SIZE = 4,

parameter DATA_SIZE = 8

)

(

input [DATA_SIZE-1:0] wdata,

input winc,

input wclk,

input wrst_n,

input rinc,

input rclk,

input rrst_n,

output [DATA_SIZE-1:0] rdata,

output wfull,

output rempty

);

wire [ADDR_SIZE-1:0] waddr,raddr;

wire [ADDR_SIZE:0] wptr,rptr,wq2_rptr,rq2_wptr;

// 时钟同步

sync_r2w #(

.ADDR_SIZE(ADDR_SIZE)

)

I1_sync_r2w(

.wq2_rptr(wq2_rptr),

.rptr(rptr),

.wclk(wclk),

.wrst_n(wrst_n)

);

sync_w2r #(

.ADDR_SIZE(ADDR_SIZE)

)I2_sync_w2r(

.rq2_wptr(rq2_wptr),

.wptr(wptr),

.rclk(rclk),

.rrst_n(rrst_n)

);

// 双口RAM

DualRAM #(

.ADDR_SIZE(ADDR_SIZE),

.DATA_SIZE(DATA_SIZE)

)I3_DualRAM(

.rdata(rdata),

.wdata(wdata),

.waddr(waddr),

.raddr(raddr),

.wclken(winc),

.wclk(wclk)

);

// 空判断

rptr_empty #(

.ADDR_SIZE(ADDR_SIZE)

)I4_rptr_empty(

.rempty(rempty),

.raddr(raddr),

.rptr(rptr),

.rq2_wptr(rq2_wptr),

.rinc(rinc),

.rclk(rclk),

.rrst_n(rrst_n));

// 满判断

wptr_full #(

.ADDR_SIZE(ADDR_SIZE)

)I5_wptr_full(

.wfull(wfull),

.waddr(waddr),

.wptr(wptr),

.wq2_rptr(wq2_rptr),

.winc(winc),

.wclk(wclk),

.wrst_n(wrst_n));

endmodule

// 双口RAM模块

module DualRAM #(

parameter DATA_SIZE = 8,//数据位宽

parameter ADDR_SIZE = 4//FIFO地址宽度

)(

input wclken,

input wclk,

input [ADDR_SIZE-1:0] raddr,

input [ADDR_SIZE-1:0] waddr,

input [DATA_SIZE-1:0] wdata,

output [DATA_SIZE-1:0] rdata

);

localparam RAM_DEPTH = 1<// 写指针同步到读时钟

module sync_w2r#(

parameter ADDR_SIZE = 4

)

(

input [ADDR_SIZE:0] wptr,

input rclk,

input rrst_n,

output reg [ADDR_SIZE:0] rq2_wptr

);

reg [ADDR_SIZE:0] rq1_wptr;

//D触发器,两级同步

always@(posedge rclk or negedge rrst_n) begin

if(!rrst_n) begin

{rq2_wptr,rq1_wptr} <=0;

end

else begin

{rq2_wptr,rq1_wptr} <= {rq1_wptr,wptr};

end

end

endmodule

// 读指针同步到写时钟

module sync_r2w#(

parameter ADDR_SIZE = 4)

(

input [ADDR_SIZE:0] rptr,

input wclk,

input wrst_n,

output reg [ADDR_SIZE:0] wq2_rptr

);

reg [ADDR_SIZE:0] wq1_rptr;

//D触发器,两级同步

always@(posedge wclk or negedge wrst_n) begin

if(!wrst_n) begin

{wq2_rptr,wq1_rptr} <= 0;

end

else begin

{wq2_rptr,wq1_rptr} <= {wq1_rptr,rptr};

end

end

endmodule

// 判空模块

module rptr_empty#(

parameter ADDR_SIZE = 4

)

(

output reg rempty,

output [ADDR_SIZE-1:0] raddr,//输出到RAM的读地址

output reg [ADDR_SIZE:0] rptr,//输出到写时钟域的格雷码

input [ADDR_SIZE:0] rq2_wptr,

input rinc,

input rclk,

input rrst_n

);

reg [ADDR_SIZE:0] rbin;//二进制地址

wire [ADDR_SIZE:0] rgraynext,rbinnext;//二进制和格雷码地址

wire rempty_val;

//----------------------------

//地址逻辑

//----------------------------

always@(posedge rclk or negedge rrst_n)begin

if(!rrst_n)begin//

rbin <=0;

rptr <= 0;

end

else begin //

rbin <= rbinnext;

rptr <= rgraynext;

end

end

//地址产生逻辑

assign rbinnext = !rempty ?(rbin+rinc):rbin;

assign rgraynext = (rbinnext>>1)^(rbinnext);

assign raddr = rbin[ADDR_SIZE-1:0];

//FIFO判空

assign rempty_val = (rgraynext==rq2_wptr) ;

always@(posedge rclk or negedge rrst_n)begin

if(!rrst_n)

rempty <= 1'b1;

else begin

rempty <= rempty_val;

end

end

endmodule

// 判满模块

module wptr_full#(

parameter ADDR_SIZE = 4

)

(

output reg wfull,

output [ADDR_SIZE-1:0] waddr,

output reg [ADDR_SIZE:0] wptr,

input [ADDR_SIZE:0] wq2_rptr,

input winc,

input wclk,

input wrst_n

);

reg [ADDR_SIZE:0] wbin;

wire [ADDR_SIZE:0] wbinnext;

wire [ADDR_SIZE:0] wgraynext;

wire wfull_val;

always@(posedge wclk or negedge wrst_n) begin

if(!wrst_n)begin

wbin <= 0;

wptr <= 0;

end

else begin

wbin <= wbinnext;

wptr <= wgraynext;

end

end

//地址逻辑

assign wbinnext = !wfull?(wbin + winc):wbin;

assign wgraynext = (wbinnext>>1)^wbinnext;

assign waddr = wbin[ADDR_SIZE-1:0];

//判满

assign wfull_val = (wgraynext=={~wq2_rptr[ADDR_SIZE:ADDR_SIZE-1],wq2_rptr[ADDR_SIZE-2:0]});//最高两位取反,然后再判断

always@(posedge wclk or negedge wrst_n)begin

if(!wrst_n)

wfull <=0;

else begin

wfull <= wfull_val;

end

end

endmodule

15. 低功耗

clock gating 门控时钟

传统的设计方法是时钟信号一直是存活着的(常开),门控时钟技术就是根据设计,将暂时不用的模块的时钟信号通过一个控制信号gating住,降低这个模块的时钟信号翻转率。

几种门控时钟的比较-

power gating 门控电源

电源门控是指芯片中某个区域的供电电源被关掉,即该区域内的逻辑电路的供电电源断开。在数字IC后端设计中,经常采用这个策略降低功耗。在后端实现过程中,加入MTCMOS来控制标准单元的开关。

-

MULT-VT 多阈值电压

阈值电压Vt越高的单元,它的漏电功耗越低,但门延迟越长,也就是速度慢;

阈值电压Vt越低的单元,它的漏电功耗越高,但门延迟越短,也就是速度快。

HVT/SVT/LVT的意思

- high Vt

- Standard Vt(也有称为Regular Vt,即RVT)

- low Vt

阈值电压越低,因为饱和电流变小,所以速度性能越高;但是因为漏电流会变大,因此功耗会变差。

- MULT-Voltage 多电压域

不同的模块根据需要以不同的电压、不同的频率工作。 - DVFS 动态电压频率调节

根据的芯片当时的实际功耗需要设定工作电压和时钟频率,这样可以保证提供的功率既满足要求又不会过剩,从而可以降低功耗。比如CPU的频率。

16. 综合

综合工具:Synplify,XST,Galileo,DC(Design Complier)

综合的过程一般都分两个:systhesis和optimization。

- systhesis是把行为级的描述通过一定的算法转成门级描述,这一过程与具体的工艺库无关、更与用户的约束无关。

- Optimization是将已经转化成门级的描述,在用户的约束下,通过算法映射到相应的工艺库中的器件上。对ASIC而言是映射到厂商的Gate库,而对FPGA而言即映射到FPGA器件的单元结构中

生成文件

- 网表文件(*.v)

- 时序文件(*.SDF)

- 设计约束文件(*.SDC)

代码风格

- 资源共享的应用限制在同一个module中。这样综合工具才能最大限度发挥其资源共享的综合作用。

- 尽可能将Critical Path上所有相关逻辑放在同一个module中。这样综合工具能发挥最佳的综合效果。

- Critical Path所在的module与其它module分别综合,对critical path采用速度有限的综合策略,对其他module采用面积优先的综合策略。

- 尽可能去Register所有的Output。这样的话,方便加约束,并且一条路径上的组合逻辑不。可能分散在各个module中。可以比较方便地达到面积、速度双赢的目的。

- 一个module的Size不能太大,具体的大小得看综合工具了。

- 一个module尽量采用一个时钟,或者整个设计只有一个时钟。

搬运自风中少年的综合理解

17. 芯片设计流程

- ASIC设计流程

- 逻辑设计

芯片架构,RTL设计,功能仿真,综合,DFT(可测试性设计),等价性检验(形式验证),静态时序分析 - 物理设计

布局规划,时钟树综合,布局布线,LVS布线图与原理图比较,DRC设计规则检查,签名静态时序分析,GDSII

各个步骤用到的软件

- FPGA设计流程

- 逻辑设计

芯片架构,RTL设计,功能仿真,综合 - 物理设计

逻辑块映射,布局布线,基于仿真的SDF,签名静态时序分析,设备编程

18. 时序路径

- 始发点

组合逻辑:数据输入

时序单元:时钟输入 - 终止点

组合逻辑:数据输出

时序单元:数据输入

- 触发器到触发器(内部时序路径)

始发点为时序单元的时钟输入;

终止点为时序单元的数据输入; - 触发器到输出端(外部时序路径)

始发点为时序单元的时钟输入;

终止点为组合逻辑的数据输出; - 输入端到触发器

始发点为组合逻辑的数据输入;

终止点为时序单元的数据输入; - 输入端到输出端

始发点为组合逻辑的数据输入;

终止点为组合逻辑的数据输出;

分别为下图中的Path2、Path3、Path1、Path4

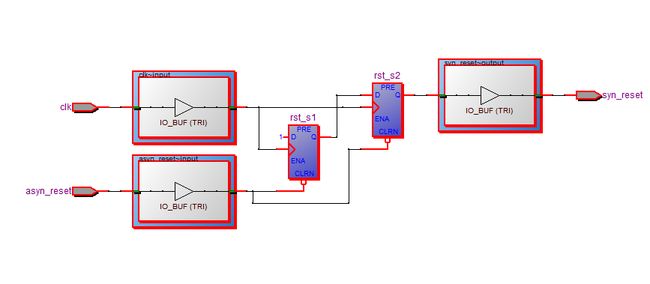

19. 异步复位同步释放

一般来说,同步系统,都使用异步复位。这是因为同步复位的电路实现,比异步复位的电路实现,要浪费更多电路资源。

当不在同一时钟域的情况下,就需要对异步复位信号做同步处理,即用异步复位同步释放,否则异步复位信号不满足恢复释放时间会产生亚稳态。

同步复位

同步复位就是指复位信号只有在时钟上升沿到来时,才能有效。

module sync_rst(

input clk,

input rst_n,

input din,

output dout

);

always @(posedge clk) begin

if(!rst_n)

dout <= 1'b0;

else

dout <= din;

end

endmodule

异步复位

异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

module async_rst(

input clk,

input rst_n,

input din,

output dout

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

dout <= 1'b0;

else

dout <= din;

end

endmodule

异步复位同步释放

所谓异步复位和同步释放,是指复位信号是异步有效的,即复位的发生与clk无关。后半句“同步释放”是指复位信号的撤除(释放)则与clk相关,即同步的。

异步复位:

显而易见,rst_async_n异步复位后,两个触发器清零,rst_sync_n将拉低,即实现异步复位。同步释放:

当复位信号rst_async_n撤除时,由于双缓冲电路的作用,rst_sync_n复位信号不会随着rst_async_n的撤除而撤除,而要等待clk信号。

代码实现如下:

module rst(

input clk,

input rst_n, // 异步复位

output rst_sync_n // 同步后的异步信号

);

always @ (posedge clk or negedge rst_n)

if (!rst_n) begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else begin

rst_s1 <= 1'b1;

rst_s2 <= rst_s1;

end

assign rst_sync_n = rst_s2;

endmodule

20. VPI接口

VPI,Verilog Procedural Interface,Verilog过程接口

进行RTL仿真时,有时候会遇到HDL工程和C语言工程进行交互,Verilog提供了VPI。

VPI使用介绍DPI,SystemVerilog提供的接口。

21. 组合逻辑消除毛刺

D触发器的D输入端,只要毛刺不能出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害。因此可以说D触发器的D输入端对毛刺不敏感。可以通过给组合逻辑的输出接触发器来消除毛刺。

但D触发器的时钟端、置位端、清零端,则都是对毛刺敏感的输入端。