XILINX DDR4 SDRAM(MIG)笔记1(基于VU250 board)

XILINX DDR4 SDRAM(MIG)笔记1(基于VU250 board)https://blog.csdn.net/linpeng_9527/article/details/105451043

XILINX DDR4 SDRAM(MIG)笔记2(基于VU9P FPGA)https://blog.csdn.net/linpeng_9527/article/details/105596704

一句话:使用以下配置,保证你的IP直接上板能work,不用仿真!!!欢迎点赞

FPGA型号:Xilinx VU250 board

IP版本:V2.2

数据手册:https://www.xilinx.com/support/documentation/ip_documentation/ultrascale_memory_ip/v1_4/pg150-ultrascale-memory-ip.pdf

先附上XDMA和MIG的整个设计拓扑

![]()

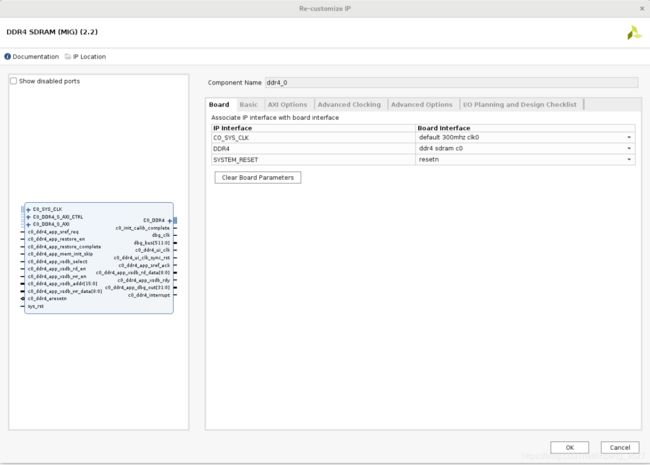

1、Board页面

选择时钟、DDR4还有复位方式,注意Xilinx VU250 board有4组系统时钟和4组DDR4(好像不用一一对应,这些时钟并不是专用于DDR4的,也可以连接MMCM IP);

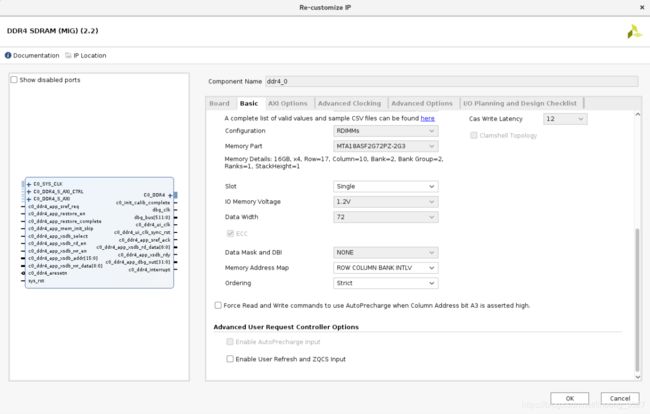

2、Basic页面

一张图截不下来,截了两张岂不是更清楚~~~

data width:DDR接口的数据位宽,选择FPGA board不可设置,如果选择FPGA 芯片的话这里是可以设置的:注意当选择64的时候IP上没有“C0_DDR4_S_AXI_CTRL”接口,当选择72的时候会多出来这个接口,这个接口怎么连接?输入接constant 0,输出为空即可;

Memory Address Map:内存地址映射,对于用户来说好像没区别;

Ordering:默认是normal,建议选择strict;

其余参数保持默认即可;

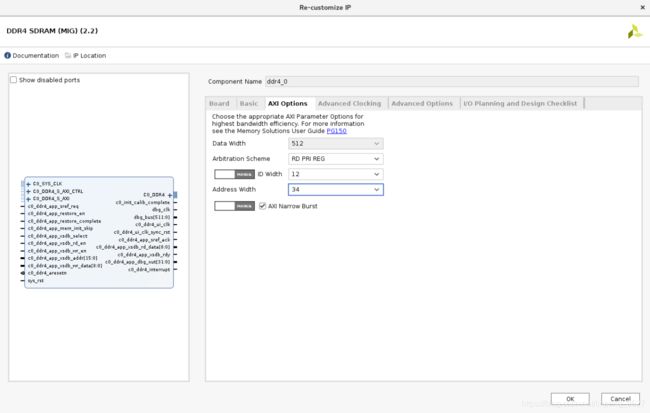

3、AXI Options页面

Data Width:按照需要设置即可;

ID Width:按照需要设置即可,啥?什么需要?当然是MIG IP前面的AXI Interconnect IP的拓扑决定这里的ID位宽;

Address Width:和FPGA DDR大小相关,4G对应32bit,8G对应33bit;

此外,一般选择支持AXI Narrow Burst;

4、Advanced Clocking页面

System Clock Option:此处用的是差分时钟

IP输出时钟频率c0_ddr4_ui_clk,为300MHz,等于tck/4,tck就是basic页面的Memory device interface speed(833ps对应1200MHz);

IP输入参考时钟频率C0_SYS_CLK,300MHz;

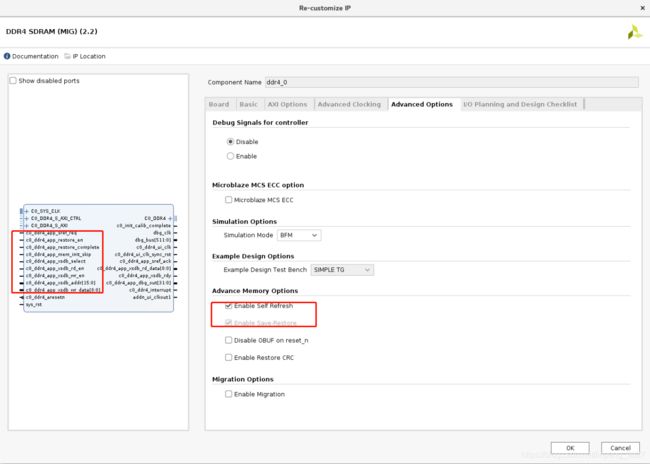

5、Advanced Options

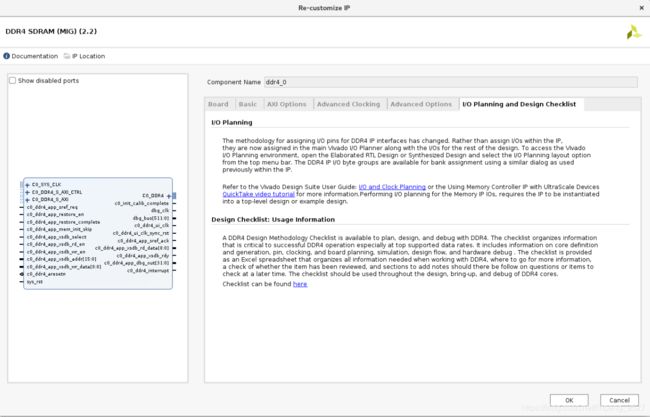

8、I/O Planning and Design Checklist

保持默认即可;

9、附上Address Editor

![]()

10、说明一点:

IP输出的c0_ddr4_ui_clk和c0_ddr4_ui_clk_sync_rst经过一个Processor System Reset IP后的复位连接到IP的c0_ddr4_aresetn。

11、提示一个深坑:不要将c0_init_calib_complete信号用作任何全局复位!!!连接Processor System Reset也不行!!!you can try