RTL Compiler之synthesis steps

1 synthesis steps

1) Search Paths

rc:/> set_attribute lib_search_path path /

rc:/> set_attribute script_search_path path /

rc:/> set_attribute hdl_search_path path /

2) Target Technology Library

rc:/> set_attribute library lib_name.lib

- Target Library: Design Compiler uses the target library to build a circuit. During mapping, Design Compiler selects functionally correct gates from the target library. It also calculates the timing of the circuit, using the vendor-supplied timing data for these gates.

3) Loading the HDL Files

- sequentially: read_hdl file1.v read_hdl file2.v read_hdl file3.v

- simultaneously: read_hdl { file1.v file2.v file3.v }

read_hdl [-v1995 | -v2001 | -sv | -vhdl [-library library_name ] | -netlist] [-define macro=value ] ... file_list

4) Performing Elaboration

This is only required for top-level design. The elaborate command automatically elaborates the top-level design and all of its references.

5) Applying Constraints

- Operating conditions; clock waveforms; I/O timing

6) Applying Optimization Constraints

7) Performing Synthesis

rc:\> synthesize -to_mapped

8) Analyzing the Synthesis Results

- generate a detailed area report, use report area

- generate a detailed gate selection and area report, use report gates

- generate a detailed timing report, including the worst critical path of the current design, use report timing

9) Exporting the Design

- gate-level netlist rc:/> write_hdl > design.v

- design constraints rc:/> write_script > constraints.g

- constraints in SDC format rc:/> write_sdc > constraints.sdc

10) Exiting RTL Compiler

quit or exit

2 recommended flow

#general setup #-------------- set_attributer lib_search_path ... set_attribute hdl_search_path .. #load the library #------------------------------ set_attribute library library_name #load and elaborate the design #------------------------------ read_hdl design.v elaborate #specify timing and design constraints #-------------------------------------- read_sdc sdc_file # add optimization constraints #---------------------------- ..... #synthesize the design #--------------------- synthesize -to_mapped #analyze design ------------------ report area report timing report gates #export design #------------- write_hdl > dessign.vm write_sdc > constraints.sdc write_script > constraints.g # export design for EDI #----------------------- write_design [-basename string ] [-gzip_files] [-tcf] [-encounter] [-hierarchical] [ design ]

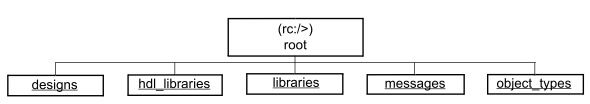

3 working in the top-level(root) directory

Root is a special object that contains all other objects represented as a ‘tree’ underneath it.

The root object is always present in RTL Compiler and is represented by a “/”, as shown in above Figure.

Root attributes contain information about all loaded designs.