modelsim仿真vivado ip核方法

对应modelsim工程案例:

https://download.csdn.net/download/cigarliang1/15988588

其他类似参考:

https://blog.csdn.net/weixin_43265132/article/details/104436412

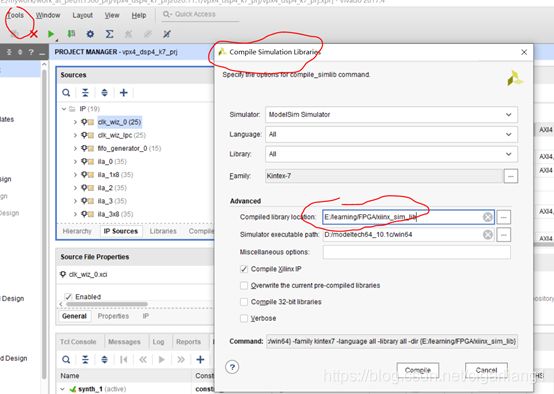

生成仿真库

首先,使用vivado生成仿真库文件

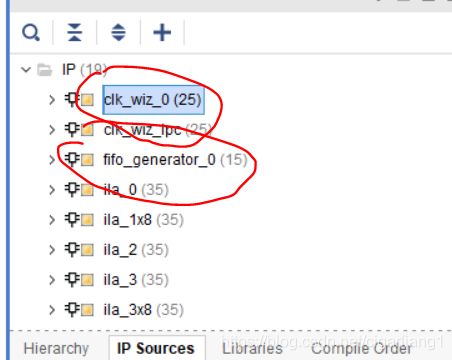

本文以仿真fifo ip核和clk_wiz ip核为例,介绍如何使用modelsim仿真。

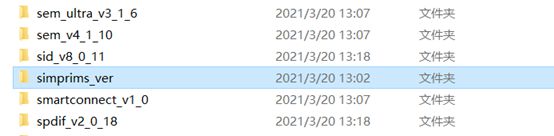

会使用生成的unisims_ver和simprims_ver库文件

生成ip核

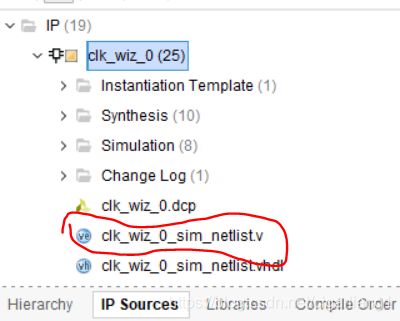

使用vivado生成相应的ip核。Ip核中会使用相应的*_sim_netlist.v文件。

Testbench文件

写出相应的tb文件,另存为tb_fifo.v文件,如下:

///

`timescale 1ns/1ps

module tb_fifo();

reg CLK;

parameter PERIOD = 10;

always begin

CLK = 1'b0;

#(PERIOD/2) CLK = 1'b1;

#(PERIOD/2);

end

glbl glbl();

reg srst;

reg [7 : 0] din = 'h0;

reg wr_en = 1'b0;

reg rd_en = 1'b0;

wire [7 : 0] dout;

wire full;

wire empty;

wire valid;

initial begin

srst = 1'b1;

#40;

srst = 1'b0;

#10;

wr_en = 1'b1;

din = 8'ha5;

#10;

rd_en = 1'b1;

#100;

rd_en = 1'b0;

end

clk_wiz_0 instance_name

(

// Clock out ports

.clk_out1(clk_out1), // output clk_out1

.clk_out2(clk_out2), // output clk_out2

.clk_out3(clk_out3), // output clk_out3

// Status and control signals

.reset(srst), // input reset

.locked(locked), // output locked

// Clock in ports

.clk_in1(CLK)); // input clk_in1

fifo_generator_0 fifo_generator_0_inst (

.clk(CLK), // input wire clk

.srst(srst), // input wire srst

.din(din), // input wire [7 : 0] din

.wr_en(wr_en), // input wire wr_en

.rd_en(rd_en), // input wire rd_en

.dout(dout), // output wire [7 : 0] dout

.full(full), // output wire full

.empty(empty), // output wire empty

.valid(valid) // output wire valid

);

endmodule

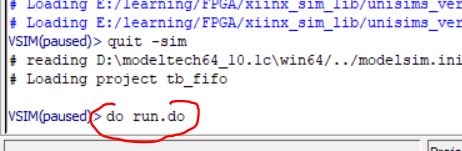

do脚本

写出相应的仿真do脚本,另存为run.do文件,如下:

quit -sim

#退出上一次的仿真

.main clear

vlib work

#在lib中,创建work

vlog ./*.v

vlog ./scrs/*.v

#vcom ./scrs/*.vhd

#增加当前目录下(./当前目录,./../上一级目录,./../../上上一级目录,以此类推)的所有v文件

#vsim -voptargs=+acc work.tb_fifo

#vsim -novopt work.tb_fifo

#仿真当前work下的clk_div_tb文件

#加入仿真库进行仿真,仿真库的路径更具实际填写

vsim -L E:/learning/FPGA/xiinx_sim_lib/unisims_ver \

-L E:/learning/FPGA/xiinx_sim_lib/simprims_ver -novopt work.tb_fifo

add wave tb_fifo/*

#增加clk_div_tb层级中的所有信号

run 1us

#运行1us时间

拷贝Glbl文件和sim_netlist文件

拷贝D:\Xilinx\Vivado\2017.4\data\verilog\src目录下的glbl.v文件(注意是按照目录的,本机是装在D盘),到仿真文件夹的scrs文件夹。

拷贝对应ip核的sim_netlist.v文件到仿真文件夹的scrs文件夹。

新建仿真工程

打开modelsim,新建仿真工程。工程路径为仿真文件夹。

输入 do run.do执行脚本。

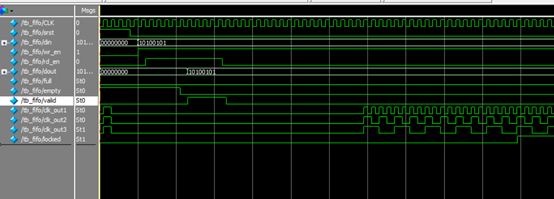

仿真波形: