沧小海笔记之《xapp523》串行通信方案介绍

目录

一、XAPP523方案简介

二、多相位采样

三、数据解析

四、时钟架构

一、XAPP523方案简介

一般来讲,低压差分信号 (LVDS) 实现设备之间实现数据交换常用的有这种方法,一种是收发器的数据传输伴随同步时钟,保证了采样的准确性,一般背板通信常用这种方案,另一种方案是在数据中包含时钟信息,在接收端采样时钟恢复技术将时钟从数据中恢复出来,当然,并不是真的从数据中分离出时钟,而是能够实现相位对齐,例如曼切斯特编码,还有GTP的CDR等等。还有一种是多倍频时钟采样,但至少得两倍频,一般五倍频的采样速率,保证数据采集的准确性,对于低速数据交换还是不错的,但对传输速率较高的通信场景就无能为力了。

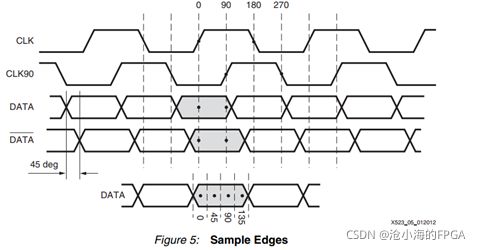

XAPP523提供的方案是上述三种之外的另外一种方案,该方案可在数据传输速率与采样时钟同频的情况下实现高达1.25Gbps的异步串行通信。实现原理是通过同频不同相的时钟对数据进行多次采样,以获得最理想的数据采样点。如下图所示,数据采用625MHZ的DDR模式进行发送,也就是1.25Gbps,在接收端将差分信号的P和N相移45度,用相位差90度的4个时钟进行采样,时钟速率是625MHZ,如此对于每bit数据就相当于有四个采样点,每两个采样点间隔为45度,对于625M时钟也就是200ps。

如下图是xilinx提供的该方案源码结构,大致可分为四个部分:

1、采样,对串行数据进行多相位采样

2、解析,对采样数据进行解析得到10bit的原始数据,但该模块并没有进行对齐操作

3、MMCM,提供本方案所需的时钟,包括采样时钟,IDELAY_CTRL时钟和解析时钟

4、对齐

二、多相位采样

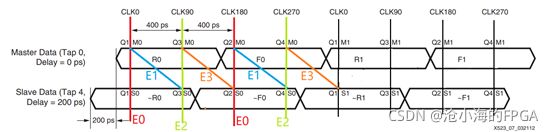

多相位采样就是用多个同频不同相的时钟对数据进行采样,关键点就是如何构造出一个这样一个模型。Xilinx提供的方案是利用IDELAY使得输出差分信号间产生一定的相位差,再用多个时钟去进行采样,这就相当于对单bit进行了4次采样,如下图所示。数据采样DDR模式进行发送,所以在时钟的上升沿和下降沿都要进行采样。所以在同一时刻,4个时钟是对前后两个周期的数据进行采样,所以相当于对每bit采了两个点,而通过对差分信号的相移,也就是同时刻“P”和“N”的不同位置进行采样,且偏差为45度,而此刻“P”和“N”表示的是同一个数,所以也就是对同一个数4个位置进行采样,分别是0度、45度、90度和135度。

“P”和“N”的相位差是由“IDLEAY”和 “IDELAYCTRL”这两个原语共同实现的。如下图是采样的示意图。

每一个BANK都有一个IDELAYCTRL,用来对该BANK的所有IDLEAYE2和ODLEAYE2进行校准。如下图所示,其中IDLEAY的参考时钟不能任意取值,可以为 190到210、290 到310,390到410这几种,但不同系列不一定都能设置,例如A7就不能设置390到410MHZ。

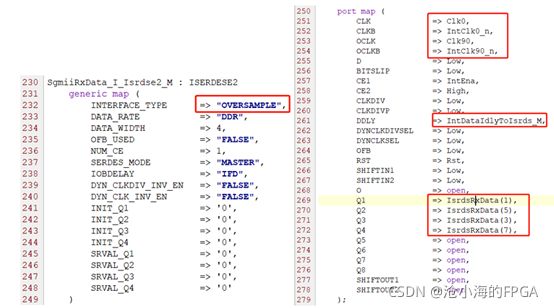

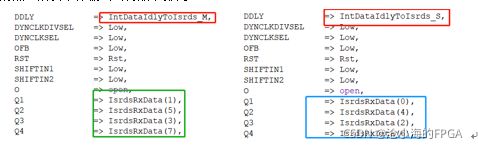

如下图是IDELAYE,差分信号分别进入这两个IDLEAY,这两个原语调用的区别就在于“IDELAY_VALUE”值得不同。其中M的是0,S的是4。这样设置就可以实现由IDELAY输出相位差45度了,也就是200ps。

IDELAY的输出相位偏移是根据参考时钟和“IDELAY_VALUE”值来决定,最大偏移是半个时钟周期,对于该参考时钟就是1.6ns,“IDELAY_VALUE”值最大为31,故每份为1600ps/31=51.6ps,我们需要偏移200ps,所以200/51.6 = 3.875≈4。

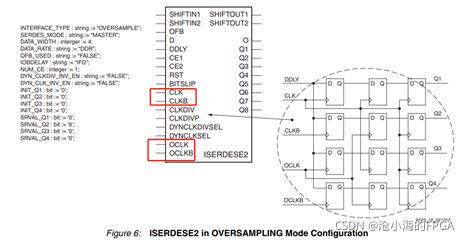

完成偏移后就要将信号分别送入ISERDESE2模块,该模块配置为“OVERSAMPLE”模式,可见需要四个输入时钟,其中“IntClk0_n”是“Clk0”的取反,“IntClk90_n”是“Clk90”的取反,输出是4bit数据。

本模块逻辑的示意图如下图所示,简单理解就是实现4个时钟的采样。采的是2bit的数据,每bit是两个采样点。

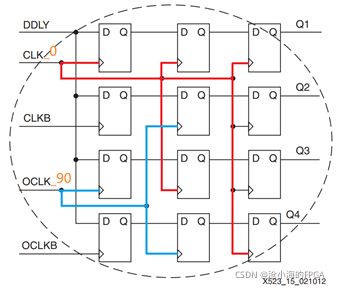

如下图是过采样逻辑图的放大图片。可见第一拍是用各自的时钟进行采样,第二拍出现了跨时钟域的情况,例如用CLK采OCLK输出数据,第三排则统一用CLK采样,为什么要这样做呢?不担心出现亚稳态么?其实采样并非正真意义上的跨时钟域,因为4个时钟有着严格的相位关系且都是单沿采样。例如偏移“OCLK”要滞后“CLK”90度,在第二拍采样时相当于在“OCLK”采样延时270度后采样,所以不会出现亚稳态,用“OCLK”采“CLKB”、“OCLKB”也是同样的道理,分别延时90度和180度采样,在第三排则都可以用“CLK”来采样,使其信号均在“CLK”时钟下进行处理

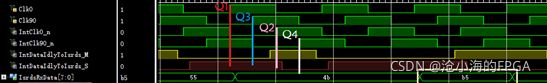

数据发送是采用DDR模式,也就是在时钟的上升沿和下降沿都发送数据,所以每个“ISERDES”完成了单比特数据的两个采样点的采样,所以Q1、Q3可认为是上升沿采样数据,Q2、Q4可认为是下降沿采样数据。差分信号“P”和“N”通过IDELAY实现了角度偏移,且“N”要比“P”滞后45度,根据PN特性通过两个ISERDES采样点的组合则实现了单比特的4倍采样。

根据上图可见“N”要滞后“P”45度,而在CLK采样时,可认为采的“N”的是最开始的点,所以采样输出会有如下排列

三、数据解析

采样是在IOB中完成的,但采样输出数据并非可用数据,只是单纯的完成了采样步骤。我们采集了8个点,包含了两比特的数据信息,需要筛选得出真正的可靠数据,解析的逻辑是在“Dru.vhd”模块实现,如下图所示。总的来说是根据采样方案以找沿的方式找到理想采样点,并对多个周期数据进行组合,最终形成一个10bit的原始数据输出,这个原始数据并不是恢复的与发送端一样的数据,还需要完成对齐操作,例如采样8B/10B编码进行数据对齐。在阐述这部分内容时

如下图是在“SgmiiRxData.vhd”模块的采样时序,对此我们再次进行分析,以便理解数据解析模块的逻辑。据图我们可以得出在标注时钟下的采样数据,由于“S”要滞后“M”45度且Q1为CLK0,所以Q1采样点的“S”应该为第一个数据,我们定义为bit0,所以组成的8bit数据为“B5”,这个数据里面包括了2bit我们需要的信息。其实据图可知Q2是在跳变沿,那么Q3、Q4就是我们需要的数据了,但逻辑是如何实现呢?

| 采样点 |

Q1 |

Q3 |

Q2 |

Q4 |

| M(P) |

bit1=0 |

bit3=0 |

bit5=1 |

bit7=1 |

| S(N) |

bit0=1 |

bit2=1 |

bit4=1 |

bit6=0 |

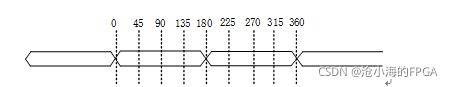

其实对于解析,我们可以做如下理解:

1、判断0~45、180~225度有没有跳变沿,如果有那么延后90度左右肯定是稳定数据,

2、判断45~90、225~270度有没有跳变沿,如果有那么延后90度左右肯定是稳定数据,

2、判断90~135、270~315度有没有跳变沿,如果有那么延后90度左右肯定是稳定数据,

2、判断135~180、315~360度有没有跳变沿,如果有那么延后90度左右肯定是稳定数据,

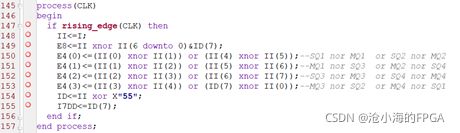

原理知道了,接下来就是如去采跳变沿,由于“S”和“M”是极性相反的,所以跳变沿的表现形式就是在同一时刻值相同。如下图是相关逻辑,注释代表相关采样点。

E0即如下图情形,MQ3、Q4或S Q3、Q4均可视为理想采样点。

E1即如下图情形,MQ3、Q4或S Q1、Q2均可视为理想采样点。

E2即如下图情形,MQ1、Q2或S Q1、Q2均可视为理想采样点。

E3即如下图情形,MQ1、Q2或S Q3、Q4均可视为理想采样点。

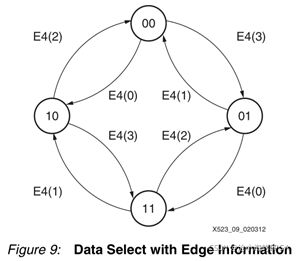

据此,可以得出如下状态机以及数据选择的映射表。

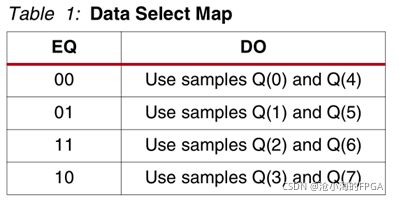

在表1中,EQ列显示了状态机的当前位置,其输入来自等式1到等式4。DO列显示互连逻辑中使用的样本集。请记住,过采样模式下的每个ISERDESE1充当两组IDDR触发器,DO指示应将哪个IDDR触发器用作理想采样点。图9显示了对于每个给定的状态或样本集,状态机下一步将去哪里。例如,假设状态机在使用Q(1)和Q(5)信号的状态01下启动。这映射到ISERDESE1主节点中的Q1和Q2,分别是CLK0和CLK180。然后,如果数据边向左移动,则中心点将从CLK0/CLK180移动到CLK90/CLK270。E4(3)将其值从0更改为1可以看出这一点。发生这种情况时,状态机将从状态00移动到状态01

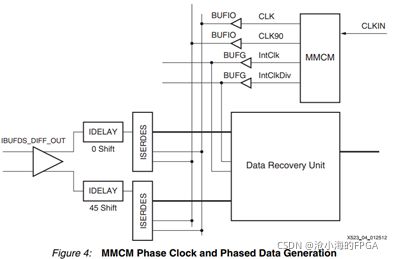

四、时钟架构

如下图是该方案的时钟架构,在《XAPP523》中进行了详细的阐述,主要内容有:

1、数据输入频率1.25Gb/s

ISERDESE2使用运行频率为625 MHz的CLK和CLK90时钟。这些通过单区域BUFIO时钟应用,这是本设计的一个要求。ISERDESE2输出的捕获使用BUFG时钟域中的片触发器完成。这种跨域时钟强制在BUFIO时钟域中运行的ISERDESE2的输出和在BUFG时钟域中捕获数据的寄存器之间施加600 ps的强制约束。(HDL源代码中提供了这些约束。)

2、DRU

a.用于iSeries 2的CLK和CLK90时钟仅适用于I/O组中的设备时钟。数据必须从ISERDESE2传输到片触发器中。捕获数据的片触发器必须在单独的625 MHz时钟下运行。要从BUFIO时钟网络移动到BUFG时钟网络,必须使用时钟域交叉(CDC)技术。在这种情况下,ISERDESE2的时钟和DRU逻辑的时钟使用状态机进行相位对齐。从ISERDESE2到DRU中寄存器的延迟不超过600ps也是非常重要的。

b. 在DRU的这一阶段,处理从625 MHz BUFG时钟到312.5 MHz BUFG时钟的数据。这些时钟彼此同步,因此没有特殊要求。

3、数据/时钟显示

来自DRU的10位数据以312.5 MHz时钟速率和时钟启用呈现给用户互连逻辑。

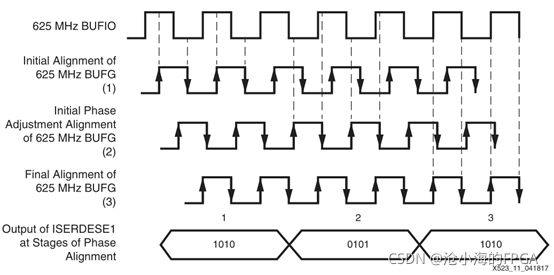

4、时钟对齐状态机

BUFIO和BUFG彼此之间存在未定义的相位关系(路由长度、时钟缓冲区延迟等)。为了在两个时钟域之间传输数据,需要CDC逻辑,或者,正如这里使用的,时钟必须是相位对齐的。为了进行时钟相位校准,建立了校准方案。时钟校准电路使用FPGA I/O组中的所有I/O都相同的知识,因此具有相同的定时

OSERDESE2加载固定的数据模式,并通过BUFG时钟树(IntClk、IntClkDiv)中的时钟进行计时。OSERDESE2的输出是IntClk(625MHz,BUFG)时钟速率下的时钟模式。通过反馈路径,从BUFIO时钟树运行的邻居ISERDESE2捕获时钟模式。数据捕获ISERDESE2在同一时钟树上运行。

使用这种技术,可以测量两个时钟之间的相位关系。利用MMCM与小型状态机的独立相移能力,BUFG时钟相移至与BUFIO时钟相匹配的相位。CLK90时钟(625 MHz)与CLK时钟(625 MHz)一起移相,而IntClk时钟(625 MHz)与IntClkDiv时钟(312.5MHz)一起移相。