【正点原子FPGA连载】第一章FPGA简介 -摘自【正点原子】新起点之FPGA开发指南_V2.1

1)实验平台:正点原子新起点V2开发板

2)平台购买地址:https://detail.tmall.com/item.htm?id=609758951113

2)全套实验源码+手册+视频下载地址:http://www.openedv.com/thread-300792-1-1.html

3)对正点原子FPGA感兴趣的同学可以加群讨论:994244016

4)关注正点原子公众号,获取最新资料更新

第一章FPGA简介

FPGA(Field Programmable Gate Array),即现场可编程门阵列,它是一种半定制的数字集成电路。FPGA凭借其灵活性高、开发周期短、处理性能强(并行)等特点,广泛应用于通信、图像处理、医疗等领域。随着科技的进步,FPGA在人工智能、5G和自动驾驶等领域也有一席之地。本章节我们将会详细介绍什么是FPGA,让大家对FPGA有个初步的认识。

本章包括以下两个部分:

1.1初识FPGA

1.2深度剖析FPGA

1.1初识FPGA

其实我很好奇当大家拿到我们的开发板,看到板子上镶嵌的那一块黑不溜秋的像饼干一样的控制芯片时,大家心里会想些什么。犹记当年我第一次见到这玩意时,忍不住用手在上面不停的抚摸,你还别说,这么贵的玩意摸起来手感真挺不错的,很有质感,可是没几分钟,新鲜劲一过我就开始犯愁了,我买的到底是个什么玩意儿,有啥用啊,我学它干嘛?现在回想起来感觉恍如昨日,感叹一句岁月不饶人啊,所以我在写这篇文章的时候就在想大家第一次拿到FPGA开发板后是啥反应,是不是像当初的我一样,乍见欣喜,然后满脑袋问号,迫切的想了解到底什么是FPGA呢,它有什么用呢,我学了它后又能干什么呢,以后有前途吗?莫急,听我娓娓道来。

1.2FPGA是什么

首先我们先来聊聊什么是FPGA,其实这个问题不好回答,简单点来说FPGA(Field Programmable Gate Array,即现场可编程门阵列)它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路个数有限的缺点,这就是FPGA。我相信这种回答很少有人能够理解,因为它涉及到的专业名词和知识面是非常广泛的,我要是把这段话就作为对FPGA的简介一定会被大家痛骂,大家可能会觉得什么玩意儿,你这说的还不如我百度呢,糊弄我吧。也确实,我自己当初看到这句话时也是一脸懵,还是不明白自己手上拿的这个“黑块块”到底是个啥,所以接下来我准备好好跟大家唠唠你们手中的“黑块块”到底是个什么东西。

我先给大家上一张图(图片来源于网络),如所示,这张图应该是一个电子类专业的学生作品。

图 1.2.1 面包板搭建数字时钟电路

从图中我们可以看到该电路是一个数字时钟,里面有晶振、蜂鸣器、数码管,以及各种74 系列的小芯片,这些小芯片能够实现的功能也就相当于几个逻辑门,如果你亲自动手去搭建它,肯定会知道搭建该电路是非常麻烦的,一根线一根线去连接,不断对照原理图,生怕搭错一根线,搞不好心态就崩了。大家可以想一想,这仅仅是搭建一个简单的数字时钟就这么多跟线了,密密麻麻的,看起来就很复杂。如果我们想要实现更加复杂的功能,那么我们就要犯难了,因为我们需要使用几十个或者上百个这种专用小芯片来完成,这样就会使得电路板的布局、布线变得困难,还会极大的影响到整个系统的性能,而且搭出来的电路体积庞大,也不美观,实用性极差,所以这种方式毫无疑问是不行的。为了改变这种情况,大家就想到了一个办法,那就是通过专用集成电路(ASIC)来实现,我们可以将要实现的特定需求交给 ASIC 厂商,让他们设计出一个专用集成电路芯片,这样就可以解决这种问题了。比如说,我们把数字时钟功能要求交给 ASIC 厂商,ASIC 厂商就会根据数字时钟功能要求设计出一个专用集成电路芯片,这一个小小的芯片它其实就完成了我们数字时钟电路功能。这种方法虽然很好,但同时也会带来很多其他的问题,比如说,生成周期长,芯片难验证,芯片内部电路不可以更改等等问题。于是人们就开始不断地去探索,看看有没有什么办法既能让我很好的实现功能,又能解决定制电路的不足。

图 1.2.2 Xilinx A7系列FPGA芯片

于是FPGA应运而生(如图 1.2.2),于 1985 年由 Xilinx 创始人之一 Ross Freeman 发明,属于可编程逻辑器件 PLD(Programmable Logic Device)的一种。真正意义上的第一颗FPGA 芯片 XC2064 为 Xilinx 所发明,这个时间差不多比著名的摩尔定律晚 20 年左右,但是 FPGA一经问世,后续的发展速度之快,超出大多数人的想象。为什么FPGA能如此迅速的发展呢,这与它本身独特的优越性密不可分。我们要知道一块专用的ASIC定制集成电路的芯片他在出厂前功能就已经定死了,就拿上面的数字时钟来举例,假如我现在拿到一块全新的数字时钟芯片,那么我只需要看看厂家给我提供的数据手册,看看它是怎么操作的,可能仅仅只需要给它通上电然后简单的配置一下它就能工作了。它的功能是不可更改的,就只能跑个数字时钟,而且它内部电路是啥样的我也不知道,虽然用起来简单,但是缺乏灵活性,但FPGA就不一样了,它在出厂的那一刻是不具备任何功能的,可以说就是一张白纸。你可以在这张白纸上肆意创作,你想要它实现数字时钟的功能没问题,通过特定的编辑语言,例如Verilog、VHDL等硬件描述语言将数字时钟的逻辑编写好,下载到FPGA内部,它就会生成一个数字时钟的电路,去完成数字时钟的功能。当你不想要这个功能了,没问题你可以随时将内部程序擦除,或者用一个新的设计去覆盖原有的设计。理论上我们可以用FPGA去生成一个任意我们想要的功能,正是基于这种强大的可编辑能力,FPGA近年来越来越受到市场的认可,在未来FPGA的适用范围必将越来越广阔。

1.2.1FPGA有什么用

跟大家聊完了什么是FPGA之后,我想大家应该对自己手中那个“黑方块”有了一定的主观印象,至少明白了它和普通芯片的区别了,那么接下来,另一个问题就出现了,FPGA我能用它做什么,我学会它之后在未来我可以从事哪些领域的工作。这个问题我觉得是大家最想要关注的问题,因为兴趣是最好的老师,如果你发现FPGA所能从事的领域你压根就不感兴趣,那么你去学习它就有可能是在浪费时间,比如你将来想当个会计,你想当个医生那你学习FPGA就没有什么必要了,当然也不排除你在学习过程中突然发现了它的魅力,从而喜欢上它。

FPGA所能应用的领域大概可以分成六大类:

1)通信领域:FPGA在通信领域的应用可以说是无所不能,得益于FPGA内部结构的特点,它可以很容易地实现分布式的算法结构,这一点对于实现无线通信中的高速数字信号处理十分有利。因为在无线通信系统中,许多功能模块通常都需要大量的滤波运算,而这些滤波函数往往需要大量的乘和累加操作。而通过FPGA来实现分布式的算术结构,就可以有效地实现这些乘和累加操作。尤其是Xilinx公司的FPGA内部集成了大量的适合通信领域的一些资源比如:基带处理(通道卡)、接口和连接功能以及RF(射频卡)三大类:

(1)基带处理资源

基带处理主要包括信道编解码(LDPC、Turbo、卷积码以及RS码的编解码算法)和同步算法的实现(WCDMA系统小区搜索等)。

(2)接口和连接资源

接口和连接功能主要包括无线基站对外的高速通信接口(PCI Express、以太网MAC、高速AD/DA接口)以及内部相应的背板协议(OBSAI、CPRI、EMIF、LinkPort)的实现。

(3)RF应用资源

RF应用主要包括调制/解调、上/下变频(WiMAX、WCDMA、TD-SCDMA以及CDMA2000系统的单通道、多通道DDC/DUC)、削峰(PC-CFR)以及预失真(Predistortion)等关键技术的实现。

总而言之只要你FPGA学的好,在通信领域你绝对可以大展身手。

图 1.2.3 FPGA无线通信

2)数字信号处理领域:在数字信号处理领域FPGA同样所向披靡,主要是因为它的高速并行处理能力。FPGA最大优势是其并行处理机制,即利用并行架构实现数字信号处理的功能。这一并行机制使得FPGA特别适合于完成FIR等数字滤波这样重复性的数字信号处理任务,对于高速并行的数字信号处理任务来说,FPGA性能远远超过通用DSP处理器的串行执行架构,还有就是它接口的电压和驱动能力都是可编程配置的不像传统的DSP需要受指令集控制,因为指令集的时钟周期的限制,不能处理太高速的信号,对于速率级为Gbps的LVDS之类信号就难以涉及。所以在数字信号处理领域FPGA的应用也是十分广泛的。

图 1.2.4 FPGA数字信号处理

3)视频图像处理领域:随着时代的变换,人们对图像的稳定性、清晰度、亮度和颜色的追求越来越高,像以前的标清(SD)慢慢演变成高清(HD),到现在人们更是追求蓝光品质的图像。这使得处理芯片需要实时处理的数据量越来越大,并且图像的压缩算法也是越来越复杂,使得单纯的使用ASSP或者DSP已经满足不了如此大的数据处理量了。这时FPGA的优势就凸显出来了,它可以更加高效的处理数据,所以在图像处理领域在综合考虑成本后,FPGA也越来越受到市场的欢迎。

图 1.2.5 FPGA图像处理

4)高速接口设计领域:其实看了FPGA在通信领域和数字信号处理领域的表现,我想大家也已应该猜到了在高速接口设计领域,FPGA必然也是有一席之地的。它的高速处理能力和多达成百上千个的IO决定了它在高速接口设计领域的独特优势。比如说我需要和PC端做数据交互,将采集到的数据送给PC机处理,或者将处理后的结果传给PC机进行显示。PC机与外部系统通信的接口比较丰富,如ISA、PCI、PCI Express、PS/2、USB等。传统的做法是对应的接口使用对应的接口芯片,例如PCI接口芯片,当我需要很多接口时我就需要多个这样的接口芯片,这无疑会使我们的硬件外设变得复杂,体积变得庞大,会很不方便,但是如果使用FPGA优势立马就出来了,因为不同的接口逻辑都可以在FPGA内部去实现,完全没必要那么多的接口芯片,在配合DDR存储器的使用,将使我们接口数据的处理变得更加得心应手。

图 1.2.6高速光纤接口眼图

5)人工智能领域:如果大家比较喜欢关注科技板块的新闻的话最近一定会被5G通信和人工智能充斥眼球,确实21世纪已经不知不觉走到了2020年,在这20年间,人工智能迅速发展,5G的顺利研发也使人工智能如虎添翼,可以预见,未来必将是人工智能的天下。FPGA在人工智能系统的前端部分也是得到了广泛的应用,例如自动驾驶,需要对行驶路线、红绿灯、路障和行驶速度等各种交通信号进行采集,需要用到多种传感器,对这些传感器进行综合驱动和融合处理就可以使用FPGA。还有一些智能机器人,需要对图像进行采集和处理,或者对声音信号进行处理都可以使用FPGA去完成,所以FPGA在人工智能系统的前端信息处理上使用起来得心应手。

图 1.2.7 FPGA与人工智能

6)IC验证领域:IC这个词大家可能一听到就觉得特别高深,不是凡人所能触及到的,而IC设计更是一些神人才能胜任的工作。不可否认的是IC设计门槛确实比较高,但是我们也没必要把它过于神话,其实简单点来讲我们可以拿PCB设计来与之比较,PCB是拿一个个元器件在印制线路板上去搭建一个特定功能的电路组合,而IC设计呢是拿一个个MOS管,PN节在硅基衬底上去搭建一个特定功能的电路组合,一个宏观一个微观。PCB如果设计废了大不了重新设计再打样也不会造成太大损失,但是如果IC设计废了再重新设计那损失就很惨重了,俗话说大炮一开,黄金万两,那么在IC领域光刻机一开黄金万两也不是吹的,光刻胶贵的要命,光刻板开模也不便宜,加上其他多达几百上千道工序,其中人力、物力、机器损耗、机器保养,绝对是让人肉疼的损失,所以IC设计都要强调一版成功。保证IC一版成功就要进行充分的仿真测试和FPGA验证,仿真验证是在服务器上面跑仿真软件进行测试,类似ModelSim/VCS软件;FPGA验证主要是把IC的代码移植到FPGA上面,使用FPGA综合工具进行综合、布局布线到最终生成bit文件,然后下载到FPGA验证板上面进行验证,对于复杂的IC我们还可以给他拆成几个部分功能去分别验证,每个功能模块放在一个FPGA上面,FPGA生成的电路非常接近真实的IC芯片。这样极大的方便我们IC设计人员去验证自己的IC设计。

图 1.2.8 华为麒麟芯片

1.2.2FPGA的现状

根据统计以及预测,在2013年全球FPGA的市场规模在45.63亿美元,至2018年全球FPGA的市场规模缓步增长至63.35亿美元。但随着目前5G时代的进展以及AI的推进速度,预计FPGA在2025年有望达到约125.21亿美元。对于全球FPGA的市场分布而言,FPGA的下游应用地区分布而言,目前最大的为亚太地区,其占比39.15%,北美占比33.94%,欧洲占比19.42%,而至2025年,亚太地区的占比将会继续的提高至43.94%,此间原因也主要因为下游应用市场在未来的主要增长大部分集中在亚太地区。按照FPGA下游应用来分拆FPGA的市场规模的话,可以看到对于2018年而言,通讯领域所用FPGA占据约40%,消费电子占据23%,为最大的应用下游;根据预测至2025年时最大的应用领域将是汽车,占比29%,而数据中心以及工业的占比也将直线上升至13%和19%(数据来源于中国产业信息网)。

图 1.2.9 FPGA全球市场规模走势

看完了市场规模我们再来看看FPGA的生产厂商,我总结了目前国际市场是两大巨头和一群小弟,很遗憾的是我国的国产FPGA也是属于小弟一列,但是我相信随着时间的积累技术和经验的积累中国FPGA发展将会越来越好。其中两大巨头分别是Xilinx和Altera:

Xilinx(赛灵思):它是全球领先的可编程逻辑完整解决方案的供应商。Xilinx研发、制造并销售范围广泛的高级集成电路、软件设计工具以及作为预定义系统级功能的IP(Intellectual Property)核。客户使用Xilinx及其合作伙伴的自动化软件工具和IP核对器件进行编程,从而完成特定的逻辑操作。Xilinx公司成立于 1984年,Xilinx首创了现场可编程逻辑阵列(FPGA)这一创新性的技术,并于1985年首次推出商业化产品。眼下Xilinx满足了全世界对 FPGA产品一半以上的需求。Xilinx产品线还包括复杂可编程逻辑器件(CPLD)。在某些控制应用方面CPLD通常比FPGA速度快,但其提供的逻辑资源较少。Xilinx可编程逻辑解决方案缩短了电子设备制造商开发产品的时间并加快了产品面市的速度,从而减小了制造商的风险。与采用传统方法如固定逻辑门阵列相比,利用Xilinx可编程器件,客户可以更快地设计和验证他们的电路。由于Xilinx器件是只需要进行编程的标准部件,客户不需要像采用固定逻辑芯片时那样等待样品或者付出巨额成本。Xilinx产品已经被广泛应用于从无线电话基站到DVD播放机的数字电子应用技术中。

传统的半导体公司只有几百个客户,而Xilinx在全世界有7500多家客户及50000多个设计开端。其客户包括Alcatel、Cisco Systems、EMC、Ericsson、Fujitsu、Hewlett-Packard、IBM、Lucent Technologies、Motorola、NEC、Nokia、Nortel、Samsung、Siemens、Sony、Oracle以及Toshiba。目前Xilinx比较火的具有代表性的FPGA芯片有Spartan7系列、Artix7系列、Kintex7系列、Virtex7系列以及Zynq系列,其中Zynq系列内嵌了ARM核,可以实现嵌入式和FPGA的联合开发(想了解更多关于Zynq系列的内容可以参考正点原子领航者开发板资料),Spartan6系列、Artix7系列可以参考超越者和达芬奇开发板的资料。 (数据资料来源于网络)。

图 1.2.10 Xilinx公司logo

Altera(阿尔特拉):它秉承了创新的传统,是世界上“可编程芯片系统”(SOPC)解决方案倡导者。Altera结合带有软件工具的可编程逻辑技术、知识产权(IP)和技术服务,在世界范围内为14000多个客户提供高质量的可编程解决方案。我们新产品系列将可编程逻辑的内在优势、灵活性、产品及时面市和更高级性能以及集成化结合在一起,专为满足当今大范围的系统需求而开发设计。在2015年,英特尔宣布以167亿美元收购FPGA厂商Altera,这是英特尔公司历史上规模最大的一笔收购。随着收购完成,Altera将成为英特尔旗下可编程解决方案事业部。Altera使用最广泛的是Cyclone系列FPGA芯片,我个人觉得它用的比较多的是Cyclone IV和Cyclone V系列的FPGA芯片,其中大家需要注意一下Cyclone V,因为该系列包括6种型号,有只含逻辑的E型号、3.125-Gbps收发器GX型号、5-Gbps收发器GT型号,还有集成了基于双核ARM®的硬核处理器系统(HPS)的SE、SX、STSoC型号。除了Cyclone系列,Altera公司还有Agilex系列Stratix系列、Arria系列、Max系列:

Agilex系列:首款采用10纳米工艺和第二代英特尔 Hyperflex FPGA 架构,可将性能提升多达40%,将数据中心、网络和边缘计算应用的功耗降低40%。英特尔Agilex SoC FPGA还集成了四核Arm Cortex-A53处理器,可提供高集成系统级水平的开发,该系列属于超高性能的SoC芯片,一般用于高端市场。

Stratix系列:这个系列也是属于高端高性能产品,拥有高密度、高性能和丰富的IO特性,可最大程度地提高系统带宽,实现多种多样的功能设计。主要应用于Open CL高性能计算、高速数据采集、高速串行通讯高频交互等领域。

Arria系列:这个系列定位为中端产品,它兼顾性能和成本,是一款性价比非常高的FPGA芯片,它内存资源丰富,信号处理能力和数据运算性能相对来说都还不错,并且收发器速度高达 25.78Gbps,支持用户集成更多功能并最大限度地提高系统带宽。此外,Arria V 和英特尔 Arria 设备家族的 SoC 产品可提供基于 ARM 的硬核处理器系统(HPS),从而进一步提高集成度和节省更多成本。

Max系列:这个系列是比较低端的,准确的说这个系列是CPLD产品,主要是应对成本敏感性的设计应用,虽然低端但是它功能也还是可圈可点的,它提供支持模数转换器 (ADC) 的瞬时接通双配置,和特性齐全的 FPGA 功能,尤其对各种成本敏感性的大容量应用进行了优化,要注意的是除了MAX 10以外,该系列的其他产品都是CPLD。

图 1.2.11 Intel公司旗下的Altera

剩余的小弟们这里就不做过多介绍了,因为所有小弟们加在一起的市场份额只有一成左右,远不是两大巨头所能比的,在这里提一句我国的FPGA厂商主要有紫光同创、京微雅格、高云半导体、上海安路、西安智多晶等,但是同国外领先厂商相比,国产FPGA厂商不论从产品性能、功耗、功能上都有较大差距。革命尚未成功,同志们仍需努力。

1.2.3FPGA的就业前景

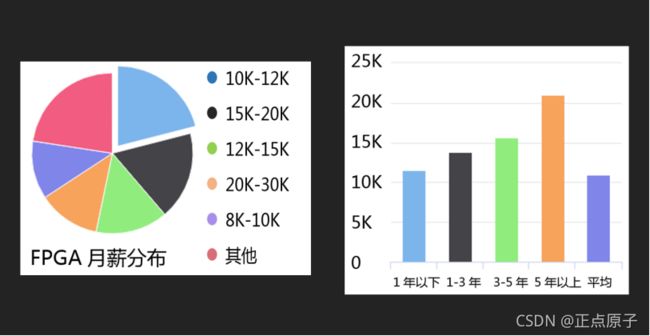

一路说下来我想大家们对于FPGA到底是什么,有什么用以及现状都有所了解了,那大家可能就要问了,学习FPGA就业前景怎么样呢?好找工作吗?我这里也很诚实,很真实的跟大家聊聊就业情况。其实相比较那些纯粹搞软件的程序员来讲呢,FPGA的就业面没有他们广,因为各行各业都需要软件信息技术的支持,哪怕你开个小超市,你还需要一个收银系统,而FPGA在适用面上就窄了一些,它大多用于图像算法、信号处理、IC验证、汽车控制等领域,不像软件开发那样各行各业都涉及到。但是有缺点就有优点,FPGA的两大巨头在不断的打造嵌入式与FPGA联合的开发模式,大量的提供IP核,使得FPGA的适用面越来越广,FPGA工程师的需求量与日剧增。在5G、虚拟现实和人工智能的冲击下,传统的微处理器在性能上越来越不能满足需求,这个时候FPGA的优势就尤为突出,我相信在未来FPGA一定会成为市场的主流。即使就目前而言FPGA工程师的福利待遇也是非常高的,如图 1.2.12所示我们可以看到FPGA工程师的平均薪资都已经达到了一万以上了,而软件工程师的薪资除了那些大牛级人物,普通程序员的薪资并没有你想象的那么高,所以在这里我非常衷心的希望大家好好学习FPGA,你们未来可期。

图 1.2.12月薪分布图

1.3深度剖析FPGA

我们在学习一个新的事物的时候一定要知其然还要知其所以然,前文我们都是表层的跟大家聊聊什么是FPGA,它能干什么,现状如何,就业前景咋样,让大家对FPGA有个直观的认识,下面我们将带领大家深度剖析FPGA的内部结构是什么样的,让大家更深层次的去认识FPGA。

1.3.1FPGA的发展由来

谈到FPGA的发展我们不妨先看看数字电路的发展,在数字集成电路中,门电路是最基本的逻辑单元,用以实现最基本的逻辑运算(与、或、非)和复合逻辑运算(与非、异或等)。与上述逻辑运算相对应,常用的门电路有与门、或门、非门、与非门、异或门等,其电路符号如下图所示:

图 1.3.1门电路符号

在最初的数字逻辑电路中,每个门电路都是用若干个分立的半导体器件和电阻、电容连接而成的。不难想象,用这种单元电路组成大规模的数字电路是非常困难的,这就严重制约了数字电路的普遍应用。1961年,美国德州仪器公司(TI)率先将数字电路的元器件制作在同一片硅片上,制成了集成电路(Intergrated Circuits,IC),并迅速取代了分立器件电路。

早期的数字逻辑设计需要设计师在一块电路板上或者如下图所示的面包板上用导线将多个芯片连接在一起。每个芯片包含一个或多个逻辑门,或者一些简单的逻辑结构(比如触发器或多路复用器等)。如下图中所示的芯片是在1960和1970年代,很多设计中都会使用的德州仪器7400系列的器件。

图 1.3.2使用74系列器件搭建的电路

自20世纪60年代以来,随着集成电路工艺水平的不断进步,集成电路的集成度也不断提高。数字集成电路经历了从小规模集成电路(Small Scale Integrated circuit,SSI),到中规模集成电路(Medium Scale Integrated circuit,MSI),再到大规模集成电路(Large Scale Integrated circuit,LSI),然后是超大规模集成电路(Very Large Scale Integrated circuit,VLSI),以及甚大规模集成电路(Ultra Large Scale Integrated circuit,ULSI)的发展过程。今天我们已经可以把十分复杂的数字系统制作在一个很小的硅片上,构成“片上系统”。

我们从逻辑功能的特点上将数字集成电路分类,可以分为通用型和专用型两类。前面介绍到的中、小规模集成电路(如74系列)都属于通用型数字集成电路。它们的逻辑功能都比较简单,而且是固定不变的。由于它们的这些功能在组成复杂数字系统时经常要用到,所以这些器件具有很强的通用性。

从理论上来讲,用这些通用型的中、小规模集成电路可以组成任何复杂的数字系统。随着集成电路的集成度越来越高,如果能把所设计的数字系统做成一片大规模集成电路,则不仅能减小电路的体积、重量和功耗,而且可以使电路的可靠性大为提高。像这种为某种专门用途而设计的集成电路称为专用集成电路,即所谓的ASIC(Application Specific Integrated Circuit)。

ASIC的使用在生产、生活中非常普遍,比如手机、平板电脑中的主控芯片都属于专用集成电路。

图 1.3.3 华为Mate 30手机中的麒麟990芯片

虽然ASIC有诸多优势,但是在用量不大的情况下,设计和制造这样的专用集成电路不仅成本很高,而且设计制造的周期也很长。可编程逻辑器件(Programmable Logic Device,PLD)的出现成功解决了这个矛盾。

可编程逻辑器件PLD是作为一种通用器件生产,但它的逻辑功能是由用户通过对器件进行编程来设定的。而且有些PLD的集成度很高,足以满足设计一般数字系统的需要。这样就可以由设计人员自行编程从而将一个数字系统“集成”在一片PLD上,做成“片上系统”(System on Chip,SoC),而不必去请芯片制造厂商设计和制作专用集成电路芯片了。

最后,我们再来总结这三种数字集成电路之间的差异。通用型数字集成电路和专用集成电路内部的电路连接都是固定的,所以它们的逻辑功能也是固定不变的。而可编程逻辑器件则不同,它们内部单元之间的连接是通过“写入”编程数据来确定的,写入不同的编程数据就可以得到不同的逻辑功能。

自20世纪70年代以来,PLD的研制和应用得到了迅速的发展,相继开发出了多种类型和型号的产品。PLD的发展历程如下图所示:

图 1.3.4 PLD的发展历程

目前常见的PLD大体上可以分为SPLD(simple PLD,简单PLD)、CPLD(complex PLD,复杂PLD)和FPGA(field-programmable gate array,现场可编程门阵列)。SPLD中又可分为PLA、PAL和GAL几种类型。FPGA也是一种可编程逻辑器件,但由于在电路结构上与早期已经广为应用的PLD不同,所以采用FPGA这个名称,以示区别。

通过对数字电路的学习我们知道,任何一个逻辑函数式都可以变换成与-或表达式,因而任何一个逻辑函数都能用一级与逻辑电路和一级或逻辑电路来实现。PLD最初的研制思想就来源于此。

图 1.3.5 PAL器件的基本电路结构

上图是SPLD中PAL(可编程阵列逻辑)的电路结构图。通过对输入端(inputs)到与门之间的可编程阵列(programmable array)进行编程,利用PAL可以获得不同形式的组合逻辑函数。数字电路课程告诉我们,任何逻辑函数式都可以转化为若干乘积项(product tems)之和的形式,亦称“积之和”形式。通过对可编程阵列进行编程,与逻辑电路输出所需要的乘积项,再通过或逻辑电路将这些乘积项相加,就得到了最终的功能输出。然后该输出送给输出电路中的寄存器用于存储或者同步,当然也可以忽略寄存器直接输出。这就是PAL作为一种“可编程逻辑器件”能够实现不同逻辑功能的原理。

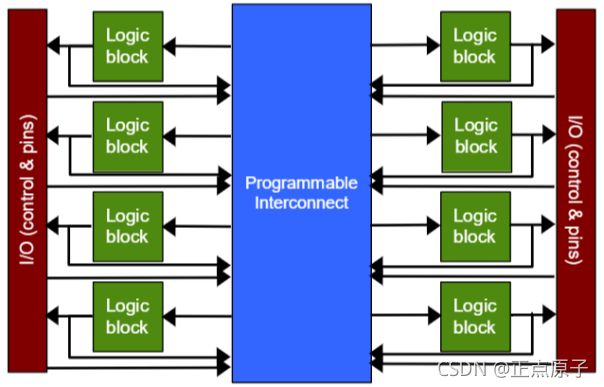

通过扩展SPLD的概念就可以得到CPLD。CPLD是复杂可编程逻辑器件,相当于将多个PAL用可编程互联阵列(Programmable Interconnect Array,PIA)连接起来,形成一个大的PLD,如下图所示:

图 1.3.6 CPLD结构示意图

上图中的Logic block(逻辑块)通常被称为逻辑阵列模块,或者LAB(Logic Array Block)。每个LAB相当于一个PAL电路,不同型号的CPLD器件可以包含十几个甚至上百个LAB。通过PIA将这些LAB连接起来,就可以构成规模更大的逻辑电路了。另外,在PAL中,I/O管脚是直接连接到逻辑的。而在CPLD中,I/O管脚是通过PIA从器件的主要逻辑中分离出来的。I/O管脚有它自己的控制逻辑,I/O控制单元可以根据需要将相应的引脚设置成输入、输出或双向工作模式。

CPLD相对于SPLD最大的优势就是拥有更大的逻辑资源和布线的可能性。CPLD中LAB逻辑和PIA是完全可编程的,使得它具有在单芯片中非凡的设计灵活性。CPLD的I/O特性和功能也远比SPLD中简单的I/O更有价值。

FPGA是在PAL、GAL和CPLD等可编程逻辑器件的基础上进一步发展的产物,但是FPGA和其前辈CPLD有着非常大的差异。我们用一张表格来罗列他们之间的差别如下表所示:

表 1.3.1 FPGA与CPLD的差别

那为什么会产生这么大的差别呢,主要是由于FPGA的内部结构决定的,下面我们就来看看FPGA的内部结构。

1.3.2FPGA的内部结构

简化的FPGA基本结构由6部分组成,分别为可编程输入/输出单元、基本可编程逻辑单元、嵌入式块RAM、丰富的布线资源、底层嵌入功能单元和内嵌专用硬核等,如下图所示。

图 1.3.7 FPGA基本结构

每个单元的基本概念介绍如下。

1)可编程输入/输出单元

输入/输出(Input/Ouput)单元简称I/O单元,它们是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配需求,为了使FPGA具有更灵活的应用,目前大多数FPGA的I/O单元被设计为可编程模式,即通过软件的灵活配置,可以适配不同的电气标准与I/O物理特性;可以调整匹配阻抗特性、上下拉电阻、以及调整驱动电流的大小等。

可编程I/O单元支持的电气标准因工艺而异,不同芯片商、不同器件的FPGA支持的I/O标准不同,一般来说,常见的电气标准有LVTTL,LVCMOS,SSTL,HSTL,LVDS,LVPECL和PCI等。值得一提的是,随着ASIC工艺的飞速发展,目前可编程I/O支持的最高频率越来越高,一些高端FPGA通过DDR寄存器技术,甚至可以支持高达2Gbit/s的数据数率。

2)基本可编程逻辑单元

基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改变其内部连接与配置,完成不同的逻辑功能。FPGA一般是基于SRAM工艺的,其基本可编程逻辑单元几乎都是由查找表(LUT,Look Up Table)和寄存器(Register)组成。FPGA内部查找表一般为4输入,查找表一般完成纯组合逻辑功能。FPGA内部寄存器结构相当灵活,可以配置为带同步/异步复位或置位,时钟使能的触发器,也可以配置成锁存器,FPGA依赖寄存器完成同步时序逻辑设计。一般来说,比较经典的基本可编程逻辑单元的配置是一个寄存器加一个查找表,但是不同厂商的寄存器与查找表也有一定的差异,而且寄存器与查找表的组合模式也不同。例如,Altera可编程逻辑单元通常被称为LE(Logic Element),由一个寄存器加一个LUT构成。Altera大多数FPGA将10个LE有机地组合在一起,构成更大的功能单元——逻辑阵列模块(LAB,Logic Array Block),LAB中除了LE还包含LE之间的进位链,LAB控制信号,局部互联线资源,LUT级联链,寄存器级联链等连线与控制资源。Xilinx可编程逻辑单元叫Slice,它是由上下两个部分组成,每个部分都由一个寄存器加一个LUT组成,被称为LC(Logic Cell,逻辑单元),两个LC之间有一些共用逻辑,可以完成LC之间的配合与级联。Lattice的底层逻辑单元叫PFU(Programmable Function Unin,可编程功能单元),它是由8个LUT和8~9个寄存器构成,当然这些可编程逻辑单元的配置结构随着器件的不断发展也在不断更新,最新的一些可编程逻辑器件常常根据需求设计新的LUT和寄存器的配置比率,并优化其内部的连接构造。

学习底层配置单元的LUT和寄存器比率的一个重要意义在于器件选型和规模估算。很多器件手册上用器件的ASIC门数或等效的系统门数表示器件的规模。但是由于目前FPGA内部除了基本可编程逻辑单元外,还包含丰富的嵌入式RAM,PLL或DLL,专用Hard IP Core(如PCIE、Serdes硬核)等,这些功能模块也会等效出一定规模的系统门,所以用系统门权衡基本可编程逻辑单元的数量是不准确的,常常混淆设计者。比较简单科学的方法是用器件的寄存器或LUT的数量衡量。例如,Xilinx的Spartan系列的XC3S1000有15360个LUT,而Lattice的EC系列LFEC15E也有15360个LUT,所以这两款FPGA的可编程逻辑单元数量基本相当,属于同一规模的产品。同样道理,Altera的Cyclone IV器件族的EP4CE10的LUT数量是10320个,就比前面提到的两款FPGA规模略小。需要说明的是,器件选型是一个综合性的问题,需要将设计的需求、成本、规模、速度等级、时钟资源、I/O特性、封装、专用功能模块等诸多因素综合考虑进来。

3)嵌入式块RAM

目前大多数FPGA都有内嵌的块RAM(Block RAM),FPGA内部嵌入可编程RAM模块,大大地拓展了FPGA的应用范围和使用灵活性。FPGA内嵌的块RAM一般可配置为单口RAM,双口RAM,伪双口RAM,CAM,FIFO等常用存储结构。RAM的概念和功能读者应该非常熟悉,在此不再赘述。FPGA中其实并没有专用的ROM硬件资源,实现ROM的思路是对RAM赋予初值。所谓CAM,即内容地址存储器,CAM这种存储器在其每个存储单元都包含了一个内嵌的比较逻辑,写入CAM的数据会和其内部存储的每一个数据进行比较,并返回与端口数据相同的所有内部数据的地址。概括的讲,RAM是一种根据地址读,写数据的存储单元;而CAM和RAM恰恰相反,它返回的是端口数据相同的所有内部地址。CAM的应用也十分广泛,比如在路由器中的交换表等。FIFO是先进先出队列的存储结构。FPGA内部实现RAM,ROM,CAM,FIFO等存储结构都可以基于嵌入式块RAM单元,并根据需求自动生成相应的粘合逻辑以完成地址和片选等控制逻辑。

不同器件商或不同器件族的内嵌块RAM的结构不同,Xilinx常见的块RAM大小是4kbit和18kbit两种结构,Lattice常用的块RAM大小是9KBIT,Altera的块RAM最灵活,一些高端器件内部同时含有3种块RAM结构,分别是M512 RAM,M4K RAM,M9K RAM。

需要补充的一点是,除了块RAM,还可以灵活地将LUT配置成RAM,ROM,FIFO等存储结构,这种技术被称为分布式RAM。根据设计需求,块RAM的数量和配置方式也是器件选型的一个重要标准。

4)丰富的布线资源

布线资源连通FPGA内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA芯片内部有着丰富的布线资源,这些布线资源根据工艺、长度、宽度和分布位置的不同而划分为4类不同的类别:

第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

第二类是长线资源,用以完成芯片Bank间的高速信号和第二全局时钟信号的布线;

第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;

第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

在实际中设计者不需要直接选择布线资源,布局布线器可自动地根据输入逻辑网表的拓扑结构和约束条件选择布线资源来连通各个模块单元。从本质上讲,布线资源的使用方法和设计的结果有直接的关系。

5)底层嵌入功能单元

底层嵌入功能单元的概念比较笼统,这里我们指的是那些通用程度较高的嵌入式功能模块,比如PLL(Phase Locked Loop)、DLL(Delay Locked Loop)、DSP、CPU等。随着FPGA的发展,这些模块被越来越多地嵌入到FPGA的内部,以满足不同场合的需求。

目前大多数FPGA厂商都在FPGA内部集成了DLL或者PLL硬件电路,用以完成时钟的高精度、低抖动的倍频、分频、占空比调整、相移等功能。目前,高端FPGA产品集成的DLL和PLL资源越来越丰富,功能越来越复杂,精度越来越高。Altera芯片集成的是PLL,Xilinx集成的是DLL,Lattice的新型FPGA同时集成了PLL与DLL以适应不同的需求。Altera芯片的PLL模块分为增强型PLL和快速PLL等。Xilinx芯片DLL的模块名称为CLKDLL,在高端FPGA中,CLKDLL的增强型模块为DCM。这些时钟模块的生成和配置方法一般分为两种,一种是在HDL代码和原理图中直接例化,另一种是在IP核生成器中配置相关参数,自动生成IP。另外可以通过在综合、实现步骤的约束文件中编写约束文件来完成时钟模块的约束。

越来越多的高端FPGA产品将包含DSP或CPU等软处理核,从而FPGA将由传统的硬件设计手段逐步过渡到系统级设计平台。例如Altera的Stratix IV、Stratix V等器件族内部集成了DSP core,配合同样逻辑资源,还可实现ARM、MIPS、NIOS II等嵌入式处理系统;Xilinx的Virtes II和Virtex II pro系列FPGA内部集成了Power PC450的CPU Core和MicroBlaze RISC处理器Core;Lattice的ECP系列FPGA内部集成了系统DSP Core模块,这些CPU或DSP处理模块的硬件主要由一些加、乘、快速进位链、Pipelining和Mux等结构组成,加上用逻辑资源和块RAM实现的软核部分,就组成了功能强大的软运算中心。这种CPU或DSP比较适合实现FIR滤波器、编码解码、FFT等运算密集型运用。FPGA内部嵌入CPU或DSP等处理器,使FPGA在一定程度上具备了实现软硬件联合系统的能力,FPGA正逐步成为SOPC的高效设计平台。Altera的系统级开发工具是SOPC Buider和DSP Builder,专用硬件结构与软硬件协同处理模块等;Xilinx的系统设计工具是EDK和Platform Studio;Lattice的嵌入式DSP开发工具是Matlab的Simulink。

6)内嵌专用硬核

这里的内嵌专用硬核与前面的底层嵌入单元是有区分的,这里讲的内嵌专用硬核主要指那些通用性相对较弱,不是所有FPGA器件都包含硬核。我们称FPGA和CPLD为通用逻辑器件,是区分于专用集成电路(ASIC)而言的。其实FPGA内部也有两个阵营:一方面是通用性较强,目标市场范围很广,价格适中的FPGA;另一方面是针对性较强,目标市场明确,价格较高的FPGA。前者主要指低成本FPGA,后者主要指某些高端通信市场的可编程逻辑器件。

1.3.3Cyclone IV系列芯片简介

Altera 的 Cyclone IV系列FPGA器件巩固了Cyclone系列在低成本、低功耗FPGA市场的领导地位。并且Cyclone IV器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

Cyclone IV器件系列是建立在一个优化的低功耗工艺基础之上,并提供以下两种型号:

■ Cyclone IV E—最低的功耗,通过最低的成本实现较高的功能性

■ Cyclone IV GX—最低的功耗,集成了3.125 Gbps收发器的最低成本的FPGA

下面我们对Cyclone IV FPGA芯片的主要特点做了一个罗列:

■ 低成本、低功耗的 FPGA 架构:

■ 6 K到150 K的逻辑单元

■ 高达6.3 Mb的嵌入式存储器

■ 高达360个18 × 18乘法器,实现DSP处理密集型应用

■ 协议桥接应用,实现小于1.5 W的总功耗

■ Cyclone IV GX器件提供高达八个高速收发器以支持:

■ 高达3.125 Gbps的数据速率

■ 8B/10B编码器/解码器

■ 8-bit或者10-bit位物理介质附加子层 (PMA) 到物理编码子层 (PCS) 接口

■ 字节串化器/解串器 (SERDES)

■ 字对齐器

■ 速率匹配FIFO

■ 公共无线电接口 (CPRI) 的TX位滑块

■ 电路空闲

■ 动态通道重配置以实现数据速率及协议的即时修改

■ 静态均衡及预加重以实现最佳的信号完整性

■ 每通道150mW的功耗

■ 灵活的时钟结构以支持单一收发器模块中的多种协议

■ Cyclone IV GX器件对PCI Express (PIPE)(PCIe)Gen 1提供了专用的硬核IP:

■ ×1,×2,和×4通道配置

■ 终点和根端口配置

■ 高达256-byte的有效负载

■ 一个虚拟通道

■ 2 KB重试缓存

■ 4 KB接收 (Rx) 缓存

■ Cyclone IV GX 器件提供多种协议支持:

■ PCIe (PIPE) Gen 1×1,×2,和×4 (2.5 Gbps)

■ 千兆以太网 (1.25 Gbps)

■ CPRI (高达3.072 Gbps)

■ XAUI (3.125 Gbps)

■ 三倍速率串行数字接口 (SDI)(高达2.97 Gbps)

■ 串行 RapidIO(3.125 Gbps)

■ Basic 模式 (高达3.125 Gbps)

■ V-by-One(高达3.0 Gbps)

■ DisplayPort(2.7 Gbps)

■ 串行高级技术附件 (Serial Advanced Technology Attachment (SATA))(高达3.0 Gbps)

■ OBSAI(高达3.072 Gbps)

■ 高达532个用户I/O

■ 高达840 Mbps发送器 (Tx),875 Mbps Rx的LVDS接口

■ 支持高达200MHz的DDR2 SDRAM接口

■ 支持高达167 MHz的QDRII SRAM和DDR SDRAM

■ 每器件中高达8个锁相环 (PLLs)

■ 支持商业与工业温度等级

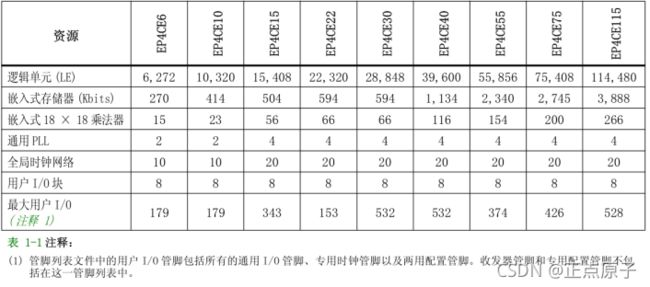

为了方便大家去选型,这里将Cyclone IV 系列器件的资源表给大家贴出来,如下图所示:

图 1.3.9 Cyclone IV器件资源表

总而言之Cyclone IV系列芯片是一款功能相对完善,成本相对较低的高性价比的FPGA芯片,并且经过了市场的长期检验,深受广大工程师的喜爱。

图 1.3.10 EP4CE10芯片

1.3.4Altera芯片的命名规则

一路看下来相信大家已经了解了什么是FPGA并且也知道了我们新起点上的芯片型号是EP4CE10F17C8N,那么大家是否知道这个命名的含义呢,这里我就以Altera的官方文档来给大家做个简单的介绍,方便大家以后自己去选型的时候可能会用得着这个小知识。

我们先来看下我从官方文档中截的图(图 1.3.10),从这张图中我们可以看到它是以Cyclone IV系列的芯片为例的:

图 1.3.10 Xilinx芯片命名规则示意图

EP4C:Cyclone IV家族;

E:逻辑资源增强型版本;

40:逻辑资源等级,数字越大逻辑资源越丰富;

F:封装类型;

29:引脚数量等级,数字越大引脚数量越多;

C:温度等级;

8:速度等级,数字越小速度越快;

N:可选的一个后缀,其中N代表无铅包装发货。

所以对照这个规则我们E10新起点上搭载的就是一块Altera(Intel)公司Cyclone IV系列的FPGA芯片,它拥有接近于10k的逻辑资源,速度等级为8,采用FBGA的封装类型,一共拥有256个IO引脚。