写在前面的话:

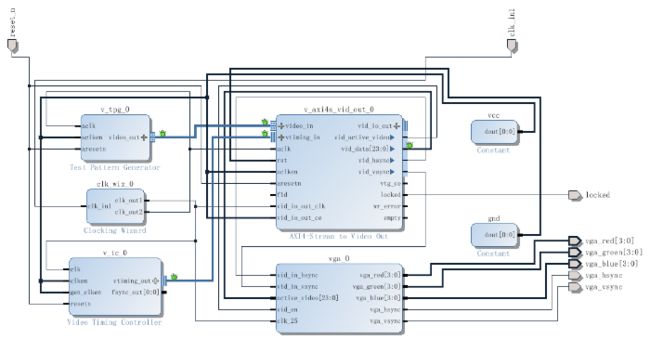

很多做视频图像的朋友在入门的时候都会有涉及到视频图像显示这块,那么在使用xilinxFPGA做显示时,除了自己写显示的驱动代码外,xilinx公司提供一个用于将AXI4stream协议转换为普通的视频时序信号axi4_to_video_out,在大部分video pipeline的处理中,我们都会用到v_tpg,

vtc,

axi4_to_video_out等,这里只是用到一个小工程,来看看这几个核最简单的用法,省去了AXI4-Lite总线的配置。该工程的配置主要是调试

axi4_to_video_out核,这个核很多人都会遇到锁不上的问题,本文就是通过阐述各个IP核的参数设置,调通了该核,给做这方面的朋友一些提示。

开发环境 :vivado 2014.2 (XP支持的最高版本)

硬件平台 :zedboard ver.d

-------------------------------------------------------@我是分割线--------------------------------------------------------------------

1.首先看一下硬件原理图

2.我是如何配置IP的?

(1)时钟

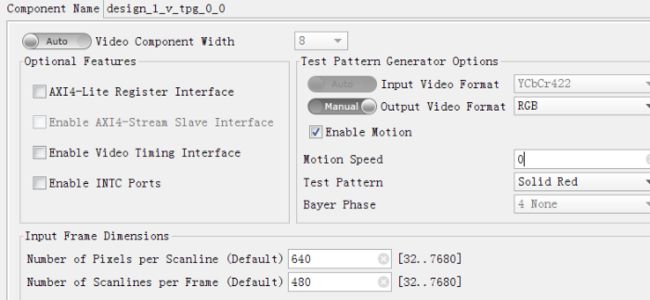

(2)Test Pattern Generator

(3)Video Timing Generator

(4)axis_stream _out

-----------------------------------------------------------------------------------------------------------------------------------

调试结果:

怎么调都不对,最后引出locked信号,发现该信号没有锁住;

-------------调试总结---------------------------

调试情况说明如下:

1.将所有的时钟的连接不管是aclk,还是clk,还是vid_in_out_clk,都设为148.5Mhz,然后把VTC设为1080p,

把TestPatternGenerator设置成为1080p,其他不变,然后可以锁住axi4_to_video_out,empty没有反应,

且fifo置为4096和8192没有影响

2.将所有的时钟的连接都连接至25Mhz,然后把VTC设置成480p把把TestPatternGenerator设置成为480p,

其他不变,然后锁不住axi4_to_video_out,但是这个时候empty是高电平输出。此时的axi4_to_video_out的fifo是4096

3.

将所有的时钟的连接都连接至25Mhz,然后把VTC设置成480p把

把TestPatternGenerator设置成为480p,

其他不变,此时的axi4_to_video_out的fifo改为32,可以axi4_to_video_out,但是empty信号还是有输出。如果

把fifo设置为4096或其他,则会出现锁不住的情况,并且empty信号也是周期性出现。

从chipscope里抓出的波形可以看到,个人觉得是“几乎空”信号,具体没有去仔细推敲。另外当时钟频率是148.5hz的时候,

怎么就没有empty=1这个信号了呢?不理解。原因大概在480p这,VTC产生的数值和TestPatternGenerator的数据不符。

4.

将所有的时钟的连接都连接至25Mhz,然后把VTC设置成480p把

把TestPatternGenerator设置成为640*480p,

其他不变,然后锁住了axi4_to_video_out,此时的axi4_to_video_out的fifo是32

5.将v_tpg和axi4_to_video_out的aclk时钟置为100Mhz,将vtc的时钟置为25Mhz,axi4_to_video_out的vid_in_out_clk置为25Mhz,

同时将模式置为480p,axi4_to_video_out锁不住,没有数据输出,具体原因不详。

6.将所有时钟置148.5Mhz,VTC,V_TPG为1080p,将fifo为32,看一下情况,empty一直没有高电平,locked一直锁住。

总结:

1.想要此核工作,要注意到时钟的一致性,尽管axi4s_to_video_out内部有异步fifo,但是我这里还是没有调通,时钟不一样就是锁不住vid_in_out_clk和aclk要保持一样,fifo设置为32即可。后来才知道只有使用master模式的时候才可以使用异步模式,这在读取axi4s_to_video_out的源码的时候是看不出来的,后来在论坛上问的时候,一位xilinx的工程师说的。

2.视频时钟比如640*480p的时钟为25Mhz@60f,按理讲480p是包含640*480的,但是在这个核里,不知道480p是多少

难道是480*16/9=854,所以这个数值也要严格对齐的。

3.应用axi4s_to_video_out为slave模式时,一定要把vtg_ce和VTC的gen_clken连上,这个通过调试就可以知道的,大家可以不用在这浪费时间le

4.下一步就要看看带VDMA,进行电路调试了。

--------------------------@分割线---------------------------------------------------------------------------------------------

最后,完成调试,成功显示,照片就不上了。很久之前的事了,才来写篇博文