0.目录

- 基本含义

- 基本概念

- 结构

- 类型

4.1 通用寄存器组

4.2 指针和变址寄存器

4.3 段寄存器

4.4 指令指针寄存器IP

4.5 标志寄存器FR

4.6 移位寄存器SR - 工作原理

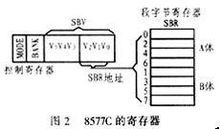

- 寄存器组织

- 寄存器寻址

1.基本含义

寄存器的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。

按照功能的不同,可将寄存器分为基本寄存器和移位寄存器两大类。基本寄存器只能并行送入数据,也只能并行输出。移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,或串行输入、并行输出,十分灵活,用途也很广。

寄存器是CPU内部用来存放数据的一些小型存储区域,用来暂时存放参与运算的数据和运算结果。其实寄存器就是一种常用的时序逻辑电路,但这种时序逻辑电路只包含存储电路。寄存器的存储电路是由锁存器或触发器构成的,因为一个锁存器或触发器能存储1位二进制数,所以由N个锁存器或触发器可以构成N位寄存器。寄存器是中央处理器内的组成部分。寄存器是有限存储容量的高速存储部件,它们可用来暂存指令、数据和位址。

在计算机领域,寄存器是CPU内部的元件,包括通用寄存器、专用寄存器和控制寄存器。寄存器拥有非常高的读写速度,所以在寄存器之间的数据传送非常快。

Cortex-M4总共有18个寄存器,相比传统ARM(如ARM7/ARM9/Cortex-A系列)的38个寄存器已减少很多,减少了内核核心面积(Die-size)。

对于编译器非常友好易用,例如:包含灵活的寄存器配置,任意寄存器之间可实现单周期乘法,任意寄存器可以作为数据、结构或数组的指针。此外,Cortex-M4还包含4个特殊功能寄存器PRIMASK、FAUI。TMASK、BASEPRI和CONTROL。

2.基本概念

寄存器最起码具备以下4种功能。

- 清除数码:将寄存器里的原有数码清除

- 接收数码:在接收脉冲作用下,将外输入数码存人寄存器中

- 存储数码:在没有新的写入脉冲来之前,寄存器能保存原有数码不变

- 输出数码:在输出脉冲作用下,才通过电路输出数码

仅具有以上功能的寄存器称为数码寄存器;有的寄存器还具有移位功能,称为移位寄存器。

寄存器有串行和并行两种数码存取方式。将n位二进制数一次存人寄存器或从寄存器中读出的方式称为并行方式。将n位二进制数以每次1位,分成n次存人寄存器并从寄存器读出,这种方式称为串行方式。并行方式只需一个时钟脉冲就可以完成数据操作,工作速度快,但需要n根输入和输出数据线。串行方式要使用几个时钟脉冲完成输入或输出操作,工作速度慢,但只需要一根输入或输出数据线,传输线少,适用于远距离传输。

3.结构

在数字电路中,用来存放二进制数据或代码的电路称为寄存器。寄存器是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,存放门位二进制代码的寄存器需用竹个触发器来构成。

对寄存器中的触发器只要求它们具有置1,置0的功能即可,因而无论是用电平触发的触发器,还是用脉冲触发或边沿触发的触发器,都可以组成寄存器。

由电平触发的动作特点可知,在CLK高电平期间,Q端的状态跟随D端状态的改变而改变;CLK变成低电平以后,Q端将保持CLK变为低电平时刻D端的状态。

74HC175则是用CMOS边沿触发器组成的4位寄存器,根据边沿触发的动作特点可知,触发器输出端的状态仅仅取决于CLK上升沿到达时刻D端的状态。可见,虽然74LS75和74HC175都是4位寄存器,但由于采用了不同结构类型的触发器,所以动作特点是不同的。

为了增加使用的灵活性,在有些寄存器电路中还附加了一些控制电路,使寄存器又增添了异步置零、输出三态控制和保持等功能。这里所说的保持,是指CLK信号到达时触发器不随D端的输入信号而改变状态,保持原来的状态不变。

上面介绍的两个寄存器电路中,接收数据时所有各位代码都是同时输入的,而且触发器中的数据是并行地出现在输出端的,因此将这种输入、输出方式称为并行输入、并行输出方式。

4.类型

4.1 通用寄存器组

通用寄存器组包括AX、BX、CX、DX4个16位寄存器,用以存放16位数据或地址。也可用作8位寄存器。用作8位寄存器时分别记为AH、AL、BH、BL、CH、CL、DH、DL。只能存放8位数据,不能存放地址。它们分别是AX、BX、CX、DX的高八位和低八位。若AX=1234H,则AH=12H,AL=34H。通用寄存器通用性强,对任何指令,它们具有相同的功能。为了缩短指令代码的长度,在8086中,某些通用寄存器用作专门用途。例如,串指令中必须用CX寄存器作为计数寄存器,存放串的长度,这样在串操作指令中不必给定CX的寄存器号,缩短了串操作指令代码的长度。下面一一介绍:

- AX(AH、AL):累加器。有些指令约定以AX(或AL)为源或目的寄存器。输入/输出指令必须通过AX或AL实现,例如:端口地址为43H的内容读入CPU的指令为INAL,43H或INAX,43H。目的操作数只能是AL/AX,而不能是其他的寄存器

- BX(BH、BL):基址寄存器。BX可用作间接寻址的地址寄存器和基地址寄存器,BH、BL可用作8位通用数据寄存器

- CX(CH、CL):计数寄存器。CX在循环和串操作中充当计数器,指令执行后CX内容自动修改,因此称为计数寄存器

- DX(DH、DL):数据寄存器。除用作通用寄存器外,在1/O指令中可用作端口地址寄存器,乘除指令中用作辅助累加器

4.2 指针和变址寄存器

- BP( Base Pointer regilter):基址指针寄存器

- SP( Stack Pointer Register):堆栈指针寄存器

- SI( Source Index register):源变址寄存器

- DI( Destination Index Register):目的变址寄存器

这组寄存器存放的内容是某一段内地址偏移量,用来形成操作数地址,主要在堆栈操作和变址运算中使用。BP和SP寄存器称为指针寄存器,与SS联用,为访问现行堆栈段提供方便。通常BP寄存器在间接寻址中使用,操作数在堆栈段中,由SS段寄存器与BP组合形成操作数地址即BP中存放现行堆栈段中一个数据区的“基址”的偏移量,所以称BP寄存器为基址指针。

SP寄存器在堆栈操作中使用,PUSH和POP指令是从SP寄存器得到现行堆栈段的段内地址偏移量,所以称SP寄存器为堆栈指针,SP始终指向栈顶。

寄存器SI和DI称为变址寄存器,通常与DS一起使用,为访问现行数据段提供段内地址偏移量。在串指令中,其中源操作数的偏移量存放在SⅠ中,目的操作数的偏移量存放在DI中,SI和DI的作用不能互换,否则传送地址相反。在串指令中,SI、DI均为隐含寻址,此时,SI和DS联用,D和ES联用。

4.3 段寄存器

8086/8088CPU可直接寻址1MB的存储器空间,直接寻址需要20位地址码,而所有内部寄存器都是16位的,只能直接寻址6KB,因此采用分段技术来解决。将1MB的存储空间分成若干逻辑段,每段最长64KB,这些逻辑段在整个存储空间中可浮动。

8086/8088CPU内部设置了4个16位段寄存器,它们分别是代码段寄存器CS、数据段寄存器DS、堆栈段寄存器SS、附加段寄存器ES、由它们给出相应逻辑段的首地址,称为“段基址”。段基址与段内偏移地址组合形成20位物理地址,段内偏移地址可以存放在寄存器中,也可以存放在存储器中。

例如:代码段寄存器CS存放当前代码段基地址,IP指令指针寄存器存放了下一条要执行指令的段内偏移地址,其中CS=2000H,IP=001AH。通过组合,形成20位存储单元的寻址地址为2001AH。

代码段内存放可执行的指令代码,数据段和附加段内存放操作的数据,通常操作数在现行数据段中,而在串指令中,目的操作数指明必须在现行附加段中。堆栈段开辟为程序执行中所要用的堆栈区,采用先进后出的方式访问它。各个段寄存器指明了一个规定的现行段,各段寄存器不可互换使用。程序较小时,代码段、数据段、堆栈段可放在一个段内,即包含在64KB之内,而当程序或数据量较大时,超过了64KB,那么可以定义多个代码段或数据段、堆栈段、附加段。现行段由段寄存器指明段地址,使用中可以修改段寄存器内容,指向其他段。有时为了明确起见,可在指令前加上段超越的前缀,以指定操作数所在段。

4.4 指令指针寄存器IP

8086/8088CPU中设置了一个16位指令指针寄存器IP,用来存放将要执行的下一条指令在现行代码段中的偏移地址。程序运行中,它由BIU自动修改,使IP始终指向下一条将要执行的指令的地址,因此它是用来控制指令序列的执行流程的,是一个重要的寄存器。8086程序不能直接访问IP,但可以通过某些指令修改IP的内容。例如,当遇到中断指令或调用子程序指令时,8086自动调整IP的内容,将IP中下一条将要执行的指令地址偏移量人栈保护,待中断程序执行完毕或子程序返回时,可将保护的内容从堆栈中弹出到IP,使主程序继续运行。在跳转指令时,则将新的跳转目标地址送入IP,改变它的内容,实现了程序的转移。

4.5 标志寄存器FR

标志寄存器FR也称程序状态字寄存器。

FR是16位寄存器,其中有9位有效位用来存放状态标志和控制标志。状态标志共6位,CF、PF、AF、ZF、SF和OF,用于寄存程序运行的状态信息,这些标志往往用作后续指令判断的依据。控制标志有3位,IF、DF和TF,用于控制CPU的操作,是人为设置的。

4.6 移位寄存器SR

在数字电路中,移位寄存器是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

移位寄存器中的数据可以在移位脉冲作用下依次逐位右移或左移,数据既可以并行输入、并行输出,也可以串行输入、串行输出,还可以并行输入、串行输出,串行输入、并行输出,十分灵活,用途也很广。

移位寄存器不仅能寄存数据,而且能在时钟信号的作用下使其中的数据依次左移或右移。

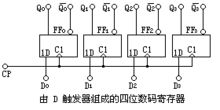

四位移位寄存器的原理图如图所示。FF0、FF1、FF2、FF3是四个边沿触发的D触发器,每个触发器的输出端Q接到右边一个触发器的输入端D。因为从时钟信号CP的上升沿加到触发器上开始到输出端新状态稳定地建立起来有一段延迟时间,所以当时钟信号同时加到四个触发器上时,每个触发器接收的都是左边一个触发器中原来的数据(FF0接收的输入数据D1)。寄存器中的数据依次右移一位。

5.工作原理

在计算机及其他计算系统中,寄存器是一种非常重要的、必不可少的数字电路苛件,它通常由触发器(D触发器)组成,主要作用是用来暂时存放数码或指令。一个触发器司以存放一位二进制代码,若要存放N位二进制数码,则需用N个触发器。

寄存器应具有接收数据、存放数据和输出数据的功能,它由触发器和门电路组成。只有得到“存人脉冲”(又称“存入指令”、“写入指令”)时,寄存器才能接收数据;在得到“读出”指令时,寄存器才将数据输出。

寄存器存放数码的方式有并行和串行两种。并行方式是数码从各对应位输入端同时输入到寄存器中;串行方式是数码从一个输入端逐位输入到寄存器中。

寄存器读出数码的方式也有并行和串行两种。在并行方式中,被读出的数码同时出现在各位的输出端上;在串行方式中,被读出的数码在一个输出端逐位出现。

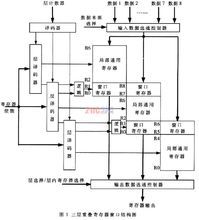

6.寄存器组织

ARM微处理器共有37个32位寄存器,其中31个为通用寄存器,6个为状态寄存器。但是这些寄存器不能被同时访问,具体哪些寄存器是可编程访问的,取决于微处理器的工作状态及具体的运行模式。但在任何时候,通用寄存器R14~R0、程序计数器PC、一个或两个状态寄存器都是可访问的。

ARM9处理器共有37个32位长的寄存器,这些寄存器包括:

- RO~R12:均为32位通用寄存器,用于数据操作。但是注意:绝大多数16位Thumb指令只能访问R0~R7,而32位Thumb -2指令可以访问所有寄存器。

- 堆栈指针:堆栈指针的最低两位永远是O,这意味着堆栈总是4字节对齐的。

- 链接寄存器:当呼叫一个子程序时,由R14存储返回地址。

- 程序计数器:指向当前的程序地址,如果修改它的值,就能改变程序的执行流。

- 6个状态寄存器(1个CPSR、5个SPSR),用以标识CPU的丁作状态及程序的运行状态,均为32位,目前只使用了其巾的一部分。

Cortex-A8处理器有40个32位长的寄存器,多了监控模式下的寄存器,如RO~R12、R15、CPSR通用,R13_ mon、R14_mon、SPSR_mon三个专用寄存器。

7.寄存器寻址

寄存器寻址就是利用寄存器中的数值作为操作数,这种寻址方式是各类微处理器经常采用的一种方式,也是一种执行效率较高的寻址方式。

寄存器寻址是指操作数存放在CPU内部的寄存器中,指令中给出操作数所在的寄存器名。寄存器操作数可以是8位寄存器AH、AL、BH、BL、CH、CL、DH、DL,也可以是16位寄存器AX、BX、CX、DX、SP、BP、SI、DI等。因为寄存器寻址不需要通过总线操作访问存储器,所以指令执行速度比较快。

寄存器寻址( Register Addressing)是以通用寄存器的内容作为操作数的寻址方式,在该寻址方式下,操作数存放在寄存器中。寄存器寻址方式的寻址对象为:A,B,DPTR,RO~R7。其中,B仅在乘除法指令中为寄存器寻址,在其他指令中为直接寻址。A可以按寄存器寻址又可以直接寻址,直接寻址时写成ACC。