DDR的原理和时序

http://www.hackhome.com/InfoView/Article_92586.html

DDR SDRAM 全称为 Double Data Rate SDRAM,中文名为“双倍数据流 SDRAM”。DDR

SDRAM 在原有的 SDRAM 的基础上改进而来。也正因为如此,DDR 能够凭借着转产成本

优势来打败昔日的对手 RDRAM,成为当今的主流。由于 SDRAM 的结构与操作在上文已有

详细阐述,所以本文只着重讲讲 DDR 的原理和 DDR SDRAM 相对于传统 SDRAM(又称

SDR SDRAM)的不同。

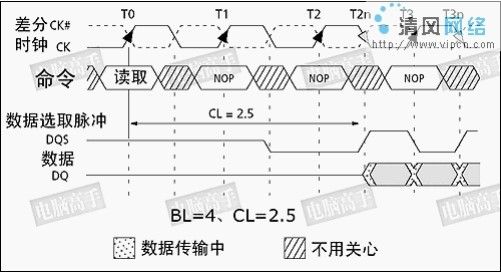

DDR SDRAM 读操作时序图

从中可以发现它多了两个信号: CLK#与 DQS,CLK#与正常 CLK 时钟相位相反,形

成差分时钟信号。而数据的传输在 CLK 与 CLK#的交叉点进行,可见在 CLK 的上升与下降

沿(此时正好是 CLK#的上升沿)都有数据被触发,从而实现 DDR。在此,我们可以说通

过差分信号达到了 DDR 的目的,甚至讲 CLK#帮助了第二个数据的触发,但这只是对表面

现象的简单描述,从严格的定义上讲并不能这么说。之所以能实现 DDR,还要从其内部的

改进说起。

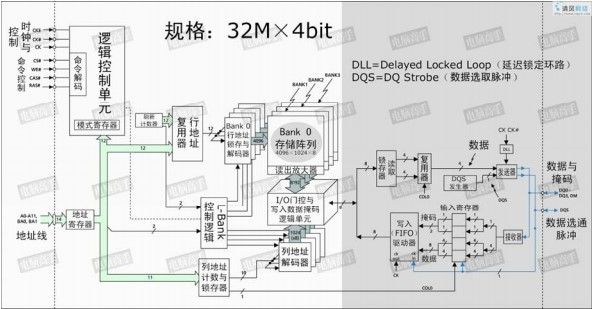

DDR 内存芯片的内部结构图,注意比较上文中 SDRAM 的结构图

这也是一颗 128Mbit 的内存芯片,标称规格也与前文的 SDRAM 一样为 32×4bit。从图

中可以看出来,白色区域内与 SDRAM 的结构基本相同,但请注意灰色区域,这是与 SDRAM

的不同之处。首先就是内部的 L-Bank 规格。SDRAM 中 L-Bank 存储单元的容量与芯片位宽

相同,但在 DDR SDRAM 中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不

能再套用讲解 SDRAM 时 “芯片位宽=存储单元容量” 的公式了。也因此,真正的行、列地

址数量也与同规格 SDRAM 不一样了。

以本芯片为例,在读取时,L-Bank 在内部时钟信号的触发下一次传送 8bit 的数据给读

取锁存器,再分成两路 4bit 数据传给复用器,由后者将它们合并为一路 4bit 数据流,然后

由发送器在 DQS 的控制下在外部时钟上升与下降沿分两次传输 4bit 的数据给北桥。这样,

如果时钟频率为 100MHz,那么在 I/O 端口处,由于是上下沿触发,那么就是传输频率就是

200MHz。

现在大家基本明白 DDR SDRAM 的工作原理了吧,这种内部存储单元容量(也可以称

为芯片内部总线位宽)=2×芯片位宽(也可称为芯片 I/O 总线位宽)的设计,就是所谓的两

位预取(2-bit Prefetch),有的公司则贴切的称之为 2-n Prefetch(n 代表芯片位宽)。

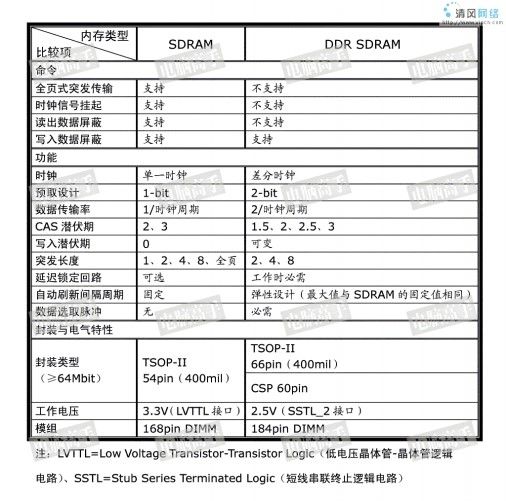

二、DDR SDRAM 与 SDRAM 的不同

DDR SDRAM 与 SDRAM 的不同主要体现在以下几个方面。

DDR SDRAM 与 SDRAM 的主要不同对比表

DDR SDRAM 与 SDRAM 一样,在开机时也要进行 MRS,不过由于操作功能的增多,

DDR SDRAM 在 MRS 之前还多了一 EMRS 阶段(Extended Mode Register Set,扩展模式寄

存器设置),这个扩展模式寄存器控制着 DLL 的有效/禁止、输出驱动强度、QFC 有效/无效

等。

由于 EMRS 与 MRS 的操作方法与 SDRAM 的 MRS 大同小异,在此就不再列出具体的

模式表了,有兴趣的话可查看相关的 DDR 内存资料。下面我们就着重说说 DDR SDRAM 的

新设计与新功能。

如日中天——DDR SDRAM(下)

1、 差分时钟

差分时钟(参见上文“DDR SDRAM 读操作时序图”)是 DDR 的一个必要设计,但 CK#

的作用,并不能理解为第二个触发时钟(你可以在讲述 DDR 原理时简单地这么比喻),而

是起到触发时钟校准的作用。由于数据是在 CK 的上下沿触发,造成传输周期缩短了一半,

因此必须要保证传输周期的稳定以确保数据的正确传输,这就要求 CK 的上下沿间距要有精

确的控制。但因为温度、电阻性能的改变等原因,CK 上下沿间距可能发生变化,此时与其

反相的 CK#就起到纠正的作用(CK 上升快下降慢,CK#则是上升慢下降快)。而由于上下

沿触发的原因,也使 CL=1.5 和 2.5 成为可能,并容易实现。

与 CK 反相的 CK#保证了触发时机的准确性

2、 数据选取脉冲(DQS)

DQS 是 DDR SDRAM 中的重要功能,它的功能主要用来在一个时钟周期内准确的区分

出每个传输周期,并便于接收方准确接收数据。每一颗芯片都有一个 DQS 信号线,它是双

向的,在写入时它用来传送由北桥发来的 DQS 信号,读取时,则由芯片生成 DQS 向北桥发

送。完全可以说,它就是数据的同步信号。

在读取时,DQS 与数据信号同时生成(也是在 CK 与 CK#的交叉点)。而 DDR 内存中

的 CL 也就是从 CAS 发出到 DQS 生成的间隔,数据真正出现在数据 I/O 总线上相对于 DQS

触发的时间间隔被称为 tAC。注意,这与 SDRAM 中的 tAC 的不同。实际上,DQS 生成时,

芯片内部的预取已经完毕了,tAC 是指上文结构图中灰色部分的数据输出时间,由于预取的

原因,实际的数据传出可能会提前于 DQS 发生(数据提前于 DQS 传出)。由于是并行传输,

DDR 内存对 tAC 也有一定的要求,对于 DDR266,tAC 的允许范围是±0.75ns,对于 DDR333,

则是±0.7ns,有关它们的时序图示见前文,其中 CL 里包含了一段 DQS 的导入期。

前文已经说了 DQS 是了保证接收放的选择数据, DQS 在读取时与数据同步传输,那

么接收时也是以 DQS 的上下沿为准吗?不,如果以 DQS 的上下沿区分数据周期的危险很大。

由于芯片有预取的操作,所以输出时的同步很难控制,只能限制在一定的时间范围内,数据

在各 I/O 端口的出现时间可能有快有慢,会与 DQS 有一定的间隔,这也就是为什么要有一

个 tAC 规定的原因。而在接收方,一切必须保证同步接收,不能有 tAC 之类的偏差。这样

在写入时,芯片不再自己生成 DQS,而以发送方传来的 DQS 为基准,并相应延后一定的时

间,在 DQS 的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开

两个传输周期。这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送

时不同步,在 DQS 上下沿时都处于保持周期中,此时数据接收触发的准确性无疑是最高的。

在写入时,以 DQS 的高/低电平期中部为数据周期分割点,而不是上/下沿,但数据的

接收触发仍为 DQS 的上/下沿

3、 写入延迟

在上面的 DQS 写入时序图中,可以发现写入延迟已经不是 0 了,在发出写入命令后,

DQS 与写入数据要等一段时间才会送达。这个周期被称为 DQS 相对于写入命令的延迟时间

(tDQSS, WRITE Command to the first corresponding rising edge of DQS),对于这个时间大

家应该很好理解了。

为什么要有这样的延迟设计呢?原因也在于同步,毕竟一个时钟周期两次传送,需要很

高的控制精度,它必须要等接收方做好充分的准备才行。tDQSS 是 DDR 内存写入操作的一

个重要参数,太短的话恐怕接受有误,太长则会造成总线空闲。tDQSS 最短不能小于 0.75

个时钟周期,最长不能超过 1.25 个时钟周期。有人可能会说,如果这样,DQS 不就与芯片

内的时钟不同步了吗?对,正常情况下,tDQSS 是一个时钟周期,但写入时接受方的时钟

只用来控制命令信号的同步,而数据的接受则完全依靠 DQS 进行同步,所以 DQS 与时钟不

同步也无所谓。不过,tDQSS 产生了一个不利影响——读后写操作延迟的增加,如果 CL=2.5,

还要在 tDQSS 基础上加入半个时钟周期,因为命令都要在 CK 的上升沿发出。

当 CL=2.5 时,读后写的延迟将为 tDQSS+0.5 个时钟周期(图中 BL=2)

另外,DDR 内存的数据真正写入由于要经过更多步骤的处理,所以写回时间(tWR)

也明显延长,一般在 3 个时钟周期左右,而在 DDR-Ⅱ规范中更是将 tWR 列为模式寄存器

的一项,可见它的重要性。

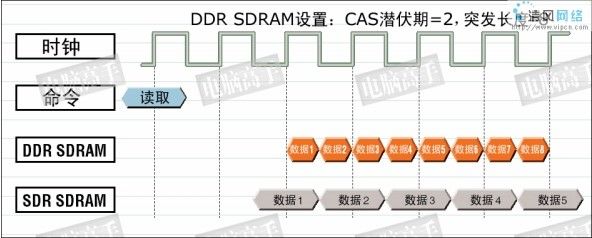

4、 突发长度与写入掩码

在 DDR SDRAM 中,突发长度只有 2、4、8 三种选择,没有了随机存取的操作(突发

长度为 1)和全页式突发。这是为什么呢?因为 L-Bank 一次就存取两倍于芯片位宽的数据,

所以芯片至少也要进行两次传输才可以,否则内部多出来的数据怎么处理?而全页式突发事

实证明在 PC 内存中是很难用得上的,所以被取消也不希奇。

但是,突发长度的定义也与 SDRAM 的不一样了(见本章节最前那幅 DDR 简示图),

它不再指所连续寻址的存储单元数量,而是指连续的传输周期数,每次是一个芯片位宽的数

据。对于突发写入,如果其中有不想存入的数据,仍可以运用 DM 信号进行屏蔽。DM 信号

和数据信号同时发出,接收方在 DQS 的上升与下降沿来判断 DM 的状态,如果 DM 为高电

平,那么之前从 DQS 中部选取的数据就被屏蔽了。有人可能会觉得,DM 是输入信号,意

味着芯片不能发出 DM 信号给北桥作为屏蔽读取数据的参考。其实,该读哪个数据也是由

北桥芯片决定的,所以芯片也无需参与北桥的工作,哪个数据是有用的就留给北桥自己去选

吧。

5、 延迟锁定回路(DLL)

DDR SDRAM 对时钟的精确性有着很高的要求,而 DDR SDRAM 有两个时钟,一个是

外部的总线时钟,一个是内部的工作时钟,在理论上 DDR SDRAM 这两个时钟应该是同步

的,但由于种种原因,如温度、电压波动而产生延迟使两者很难同步,更何况时钟频率本身

也有不稳定的情况(SDRAM 也内部时钟,不过因为它的工作/传输频率较低,所以内外同

步问题并不突出)。DDR SDRAM 的 tAC 就是因为内部时钟与外部时钟有偏差而引起的,它

很可能造成因数据不同步而产生错误的恶果。实际上,不同步就是一种正/负延迟,如果延

迟不可避免,那么若是设定一个延迟值,如一个时钟周期,那么内外时钟的上升与下降沿还

是同步的。鉴于外部时钟周期也不会绝对统一,所以需要根据外部时钟动态修正内部时钟的

延迟来实现与外部时钟的同步,这就是 DLL 的任务。

DLL 不同于主板上的 PLL,它不涉及频率与电压转换,而是生成一个延迟量给内部时

钟 。 目 前 DLL 有 两 种 实 现 方 法 , 一 个 是 时 钟 频 率 测 量 法 ( CFM , Clock Frequency

Measurement),一个是时钟比较法(CC,Clock Comparator)。CFM 是测量外部时钟的频率

周期,然后以此周期为延迟值控制内部时钟,这样内外时钟正好就相差了一个时钟周期,从

而实现同步。DLL 就这样反复测量反复控制延迟值,使内部时钟与外部时钟保持同步。

CC 的方法则是比较内外部时钟的长短,如果内部时钟周期短了,就将所少的延迟加到

下一个内部时钟周期里,然后再与外部时钟做比较,若是内部时钟周期长了,就将多出的延

迟从下一个内部时钟中刨除,如此往复,最终使内外时钟同步。

CFM 式 DLL 工作示意图

CC 式 DLL 工作示意图

CFM 与 CC 各有优缺点,CFM 的校正速度快,仅用两个时钟周期,但容易受到噪音干

扰,并且如果测量失误,则内部的延迟就永远错下去了。CC 的优点则是更稳定可靠,如果

比较失败,延迟受影响的只是一个数据(而且不会太严重),不会涉及到后面的延迟修正,

但它的修正时间要比 CFM 长。DLL 功能在 DDR SDRAM 中可以被禁止,但仅限于除错与

评估操作,正常工作状态是自动有效的。

昔日贵族——Rambus DRAM(一)

谈起 DDR SDRAM 与 Rambus DRAM(简称 RDRAM)之间的恩怨,很多人现在还是

津津乐道。的确,上一世纪末的内存大战虽胜负已分,但至今仍余波未平。在主流市场 DDR

SDRAM 成为王者,RDRAM 则沦为“高端贵族”。

Rambus 公司于 1990 年 3 月成立,之后不久就有了 Rambus 的核心专利——RSL(Rambus

Signaling Level,Rambus 发信电平技术)。Rambus 内存最早出现于 1995 年 12 月,那时它与

任天堂 64(Nintendo64)游戏机一起发售,但名声不大。从 1996 年 12 月开始,Rambus 与

Intel 合作开发,准备将 Rambus 推广到 PC 领域。到 Rambus 内存真正亮相于 PC 市场时已

经是 1999 年 11 月了。

一、RDRAM 简介

RDRAM 与 DDR SDRAM 一样,也是一种采用双沿触发技术的内存, 但它在结构、控

制体系方面相对于传统 SDRAM 有着不小的变化,首先我们来看看它与 SDRAM 之间的简

单比较。

RDRAM 与传统 SDRAM 的架构比较

从架构比较图中,可以看出 RDRAM 在工作方式上与 SDRAM 有了很大不同。SDRAM

需要多颗芯片并联组成 P-Bank 与北桥沟通,而在 RDRAM 架构中每个芯片就是一个单独工

作的读写单元,芯片的位宽就是与北桥接口的位宽,所以如果想用 ECC,就要用专门的 ECC

型芯片,也因此有了 16/18bit 的两种规格。而芯片的位宽就是一个 RDRAM 通道的位宽(本

文以 16bit 芯片为例进行介绍)。

为了达到更高的容量,在一个通道中将多颗 RDRAM 芯片串起来,形成 RIMM(Rambus

Interface Memory Module,Rambus 接口内存模组),如果主板允许,完全可以设计一个超长

的内存插槽与模组,但现实中肯定不能这么做,所以在主板上 Rambus 又把模组串起来组成

通道。由于是串联的形式,所以要求起始端与终结端形成一个完整的通路,而 RIMM 就是

这个通路的串联器,因此 Rambus 要求所有的插槽必须插满,如果没有 RIMM 则用 C-RIMM

(Continuity RIMM,RIMM 续连器)代替,以达到联通 RSL 信号并行终结器的目的。工作

时,RDRAM 每次寻址一颗芯片,所需要的数据则由通道数据总线传送到北桥,而不像

SDRAM 那样由所在模组直接通过 DIMM 接口传向北桥,也因此 RIMM 的引脚定义几乎是

左右对称的。

由于位宽的降低,为保证高带宽,RDRAM 使用了更高的时钟频率(这就意味着它不可

能与系统时钟同步,所以只能叫 RDRAM 而不是 RSDRAM),芯片的工作频率明显高于

SDRAM/DDR,这样芯片的工作热量也急剧上升,为此 Rambus 在官方规范中规定 RIMM 必

须配备散热片,从而成了现在这个样子。

32bit 位宽 PC1066 芯片标准的 RIMM,它是目前 PC 领域中性能最高的 RDRAM 产品

二、RDRAM 的结构简介

1、 RDRAM 的 L-Bank 结构

RDRAM 的内部仍主要由 L-Bank 构成,但它的设计与 SDRAM 家族有很大的不同。首

先,每个 L-Bank 有两个数据通道 A 和 B,各为 8bit 位宽(ECC 型号为 9bit,这种设计就是

Direct DRAM 较以前 RDRAM 的不同),每个端口都配有 S-AMP。根据 L-Bank 数量与 S-AMP

的分配方式不同,目前 RDRAM 共有三种内核结构,分别是 32s、16d 与 4i。

较早时,RDRAM 的设计是 16d,所谓的 d 是指 Double(双),即除了 0 与 15 号 L-Bank,

其余相邻的 L-Bank 每个数据通道(A 和 B)共用一个 S-AMP。

16d L-Bank 结构

后来分别向高端和低端领域发展了 32s 与 4i 技术。前者的 s 代表 Split,它将原来的 16d

内核分割为两个部分,各为 16d 结构,0、15、16、31 号 L-Bank 的每个数据通道各自独占

一个 S-AMP。4i 则与传统的 SDRAM 相似,i 代表 Independent(独立),只有 4 个 L-Bank,

各 L-Bank 的每个数据通道有单独的 S-AMP。

32s L-Bank 结构

4i L-Bank 结构

上文已经讲过,L-Bank 数越多,造成 L-Bank 寻址冲突的机率就越小,但理论上 L-Bank

越多,所用的 S-AMP 也就越多, RDRAM 内存核心加工与面积控制的难度就越大,因此

32s 与 16d 都采用了共享 S-AMP 的设计。但即使这样,RDRAM 的生产成本仍被限制在较

高的水平上,在早期这成为了 RDRAM 难以普及的重要原因。而 4i 就是为解决这一问题而

出现的方案,成本更低,但性能也较前两者降低了。

另外,由于共享 S-AMP 的设计,除了个别独有 S-AMP 的 L-Bank,其他的 L-Bank 每次

预充电操作也都是成双成对的。为此,在逻辑控制上,RDRAM 的操作要尽量避免相邻 L-Bank

前后进行,否则也会降低 RDRAM 的实际效率。

2、RDRAM 的主要特点

目前 RDRAM 主要有两个容量规格——128Mbit 和 256Mbit。L-Bank 中存储单元的容量

也并不等于 RDRAM 的接口位宽,而是它的 8 倍,因此可以说 RDRAM 是一种 8bit 预取设

计,这是它最主要的特点。对于 16bit 芯片,其存储单元的容量为 128bit,这些数据分别从

通道 A 和 B 传输至 L-Bank,也就是说 L-Bank 两端的 S-AMP 一次各负责 72bit 数据的传输。

由于预取为 8bit,所以 RDRAM 的突发长度也固定为 8,因为如果再高,对于 PC 应用将不

太适合。不过需要特别注意的是,一个字节的数据不是由数据通道中的 8 条数据线进行并排

传输,而是一个字节由一条数据线进行 8 次传输,这一点也与 SDRAM 不同,它意味着北

桥在进行数据读/写时,必须要等 8 个周期之后才能完成,中途不能停止。也就是说,读取

时目前的北桥(如 850)一次接收 128bit(16 字节)的数据,然后再转换为两个 64bit 数据

分两次向 CPU 传送。

由于 RDRAM 的存储单元容量很大,所以 RDRAM 的行列地址线也大为减少,以 256Mbit

的 4i 结构的 RDRAM 为例,行地址为 12bit(4096),列地址为 7bit(128)。如果是 32s 结构

的,由于 L-Bank 地址的增多,行列地址要更少(分别是 9 和 7bit)。而且 RDRAM 的行列地

址线是独立的,但是 RDRAM 的行与列地址线各自只有 3 条和 5 条,显然不够用,Rambus

又是怎么搞定的呢?这就涉及到 RDRAM 具体的操作设计了。

昔日贵族——Rambus DRAM(二)

三、 RDRAM 的具体操作与相关技术

1、 初始化与命令包

RDRAM 也有一个控制寄存器,在开机初始化过程中用来对 RDRAM 芯片进行配置,

有的信息由北桥动态写入(如芯片地址、自刷新模式等),有的则是出厂时就设置好不能更

改的(如刷新计数、生产商信息、支持的协议版本等)。在初始化之后,RDRAM 才能进入

正常的工作状态。

RDRAM 的读写操作过程与 SDRAM 基本是一样的,也要进行片选、L-Bank 定址、行/

列寻址等操作(此时的行就是指 RDRAM 内存系统中的页),但由于它的每次操作只针对一

颗芯片,所以具体操作起来有很大不同,这主要体现在“命令包”的方式上。

RDRAM 读取时序图,以 PC800 为例,400MHz 时钟频率。

在上图中,我们可以看到行寻址命令与列寻址(读)命令并没有同时发出,而且各自占

用了 10ns 的时间。我们算一算,对于 PC800,10ns 相当于 8 个传输周期。难道是传输有延

迟?从行列地址的设计,就能猜到这是一个命令包形式的操作。

所谓的命令包,就是将一组命令集合在一起,统一发出。在 RDRAM 中,行命令包与

列命令包都分为两种,一种是正常的读/写操作命令,一种是芯片操作命令(如数据掩码、

预充电、刷新、电源管理等)。现在我们就看看行与列读/写命令包都包含哪些信息。

行读/写命令包的信息组成

列读/写命令包的信息组成

至于操作命令包就不在此多说了,因为构成的形式基本就是这样,每次用 8 个传输周期

进行命令发送。而且由于 RDRAM 的命令代码很多,也比较复杂,在本专题中也不用一一

列出,关键在于让大家明白 RDRAM 的寻址是怎么一回事即可,剩下的具体代码定义,如

果有兴趣大家可以自行研究。

2、 操作时序计算

通过上面的时序图,我们可以发现 RDRAM 计算时序的方法与 SDRAM 家族不一样,

这在比较两者间时序效率时有着关键的影响。

Rambus 的时序规定与 FPE/EDO 内存时一样,在读取时延用了 tRAC、tCAC 的定义,

前者是行访问周期(RAC,RAS Access Cycle/Delay),后者是列访问周期(CAC,CAS Access

Cycle/ Delay),你可以把它等同于 SDRAM 中的 CL,但决不能在 RDRAM 中引入 CL 这个

概念。在写入时则将 tCAC 替换为 tCWD(CAS to Write Delay)。它们的单位都是时钟周期,

对于 PC800,一个时钟周期就是 2.5ns,对于 PC1066 就是 1.876ns 了。显然,时钟频率越高,

延迟周期就越短。

但是这些时序是从命令包发送完毕开始计算,SDRAM 则是在命令发送同时开始计算。

因此,在计算 RDRAM 的操作延迟时,命令包本身占用的时间也必须要考虑进来。

3、 写入延迟与掩码操作

RDRAM 为写入设置了专用的延迟 tCWD,这并不是被迫而是有意设计的。RDRAM 不

需要 DQS 之类的信号进行同步操作,数据是可以立即接受的,但出于总线利用率的考虑,

RDRAM 加入了写入延迟,它略短于 tCAC。在具体操作中,芯片上没有引脚控制写入允许/

禁止,一切的命令在命令包中进行定义,所以读命令可以在写过程中发出,经过 tCAC 后有

效。这样在写后读操作中,除了 tCAC 与 tCWD 之间的差距外(估计是留给写回的时间),

几乎没有任何停顿,而不像 SDR/DDR SDRAM 中有较大延迟。

在写入过程中,数据都是先存在写入缓冲区中,这个操作的目的在于等待掩码的控制。

RDRAM 的数据掩码只对写入有效,当收到掩码命令后,RDRAM 将指定的引脚数据从缓冲

区中删除,之后再进行真正的写入。

昔日贵族——Rambus DRAM(三)

4、多通道技术与多通道模组

PC800 的速度在当时可算是 RDRAM 的一极限,但它的 1.6GB/s 带宽并不能满足高端应

用的需要,而且 DDR 一方主推的产品是 P2100 的 DDR-266,为此 RDRAM 利用双通道技术

来弥补带宽上的不足。简单的说,它就像一个用于内存的 RAID,两个通道的数据在 RAC

一端进行分割(写)与合并(读),两个通道的 RIMM 缺一不可并要求结构完全一致,因

为寻址信号是一样的,必须适用于两个 RIMM,这也就意味着两个 RIMM 的存储轨迹也是

一样。但是,数据的寻址延迟并没有变化,只是连续传输率提高了一倍达到 3.2GB/s(两个

PC800 通道),而且总的内存容量也增加了一倍。时至今日,虽然 RDRAM 使用窄位宽设

计,但毕竟不是串行的方式,提升频率也越来越困难,最新的 PC1066 标准也只达到 2.1GB/s

的带宽,此时双通道设计几乎成为 RDRAM 的标配。可以说没有双通道技术的支持,RDRAM

是很难走到今天的。

RDRAM 双通道结构

以前,双通道技术是以两条 RIMM 来实现,在双通道已经是 RDRAM 标准设计的今天,

这种设计的弊病很明显,比如客户的购置成本、主板的布线设计等。为此,在一些内存厂商

的支持下,RDRAM 出现了多通道模组设计,其主体思路就是将每个通道的信号终结电路移

植到模组上来,在一个模组上实现多通道传输。

32bit 的 RIMM 设计,每个通道的终结器做在了模组上

目前 PC 市场上 32bit RIMM 逐渐开始流行并终将取代传统的双通道设计,对于 64bit

RIMM,由于是 4 通道设计,得需要 4 通道北桥芯片的支持,所以目前不可能在台式机领域

里普及。

不同规格的 RIMM 间比较

5、 黄石技术

黄石(Yellowstone)是 Rambus 为了适应未来带宽的需要而开发的信号与数据传输技术,

其主要的技术特点有四个:

黄石技术的物理系统结构

A、3.2GHz 传输频率,未来可高达 6.4GHz,按 16bit 位宽计算,带宽可达 6.4GB/s,双

通道应用则为 12.8GB/s。

B、极低电压的差分 RSL 信号(DRSL),降低电源消耗并保证信号质量与制造成本。

信号电压差值只有 200mV,是目前电压差最小的内存信号技术。

DRSL 发信技术与其他内存接口发信技术的比较

C、八倍数据流技术(ODR,Octal Data Rate)。目前采用黄石技术的 RDRAM,时钟频

率仍是 400MHz,但芯片内部通过专用的锁相回路(PLL)将其转换为 1.6GHz 的内部时钟,

然后在此基础上使用 DDR 技术,从而能在一个时钟周期内传输 8 次数据。数据传输频率也

因此达到了 3.2GHz。

ODR 操作示意图

D、固定相位技术(FleXPhase),使内存生产者不再费力的去调校 PCB 的设计以减少延

迟/潜伏期对数据/时钟间同步的影响。固定相位技术使信号本身就具备了数据/时钟同步与自

校准能力,从而使外围有关时序跟踪的设计与布线变得非常简单,并有助于提高同步性,提

高总线利用率。

黄石技术于 2001 年 10 月 2 日正式发布,但是虽然它有这样那样的优点,但从最近的资

料中显示,Rambus 主要将其定位于消费电子、网络、通信和图形设备市场。对于目前的桌

面 PC 市场,黄石在近期应用的可能性并不大。

Rambus 展示的用于显卡的点对点黄石 RDRAM 显存方案

昔日贵族——Rambus DRAM(四)

1、 延迟与总线利用率的比较

仍以 PC800 为例,由于 tRAC 已经包括了从行选通至数据输出的所有延迟,与是否双

通道无关,所以我们只需将它再加上命令包的占用时间即可算出 RDRAM 一次访问所需要

的时间。PC800 的 tRAC 基本都是 40ns(16 个时钟周期),加上命令包占用的 4 个时钟周期

10ns,总共耗时为 50ns。而这是在行关闭的情况下,没有计算预充电的时间 tRP,它一般为

12 个时钟周期(加上命令包时间),即 30ns,共计 80ns。显然,时钟频率越高,延迟就会越

短。下面就来比较一下读取操作时 RDRAM 与 DDR SDRAM 的延迟。

读取操作时 RDRAM 与 DDR SDRAM 的延迟比较表

从对比表中可以看出,RDRAM 相对于 DDR SDRAM 在首次寻址时的确存在较大的延

迟,即使是最新的 PC1066,在与 DDR-333 的比较中也不占优势。不过,借助于双通道的设

计,RDRAM 在高数据量传输应用中的优势还是比较明显的。另外,在总线的利用率方面

RDRAM 的设计也居领先地位,这为保证它的总体效率提供了坚实的保障。

各内存的总线效率比较

这个对比表是东芝公司经过反复实验而得出的结论,它是通过一些典型的操作(如写-

读-读),结合不同页命中情况下的时序,以及刷新对内存操作的影响等分析而得出的。由于

DDR SDRAM 在 L-Bank 数量上占劣势,所以出现 L-Bank 寻址冲突的可能性要大为提高,

而且在写后读操作中,RDRAM 的延迟也明显小于 SDRAM 家族,因此虽然 PC800 的峰值

带宽不如 DDR-266,但综合效率要更好。这可以解释为什么在一些测试中,RDRAM 明显

比 DDR 领先的原因。不过,在以零散数据为主的操作中,RDRAM 的固定传输周期以及高

延迟就成为了性能的障碍。

从前面的分析可以看出,SDRAM/DDR 在数据控制上的灵活性要比 RDRAM 高,首次

访问的延迟也更短,因此在某些操作中,即使带宽比 RDRAM 系统小,性能仍不见得落后。

比如 845D/E 在某些应用测试中,完全可以与双通道 PC1066 一较高低。而 Intel 决定在高端

服务器领域使用 DDR 芯片组,也基本是出于这个考虑,因为在服务器的操作中,零散型存

取操作所占比例很大。相反,若大规模连续存取操作占比例很大(如视频与音频工作站),

那么可能就要考虑 RDRAM 了。

2、 未来竞争展望

目前随着多通道技术在 DDR 上的普及,RDRAM 在带宽上的优势也变得不明显了。所

以,RDRAM 如果不及时提高单通道的性能,很快会被强大的 DDR 家族赶出台式机领域。

但 RDRAM 的时钟频率已经很高了,再向上提高已经很难,不少 RDRAM 厂商都表示,

800MHz 时钟频率可能将是 RDRAM 的一个巨大门槛,即使能超过,成本可能也是惊人的,

要知道目前 533/400MHz 的 RIMM 就已使用了 8 层 PCB,800MHz 时 PCB 成本将很难控制。

这也是为什么 RDRAM 急于推出 32bit 与 64bit RIMM 的原因,毕竟内存这种高带宽应用设

备,还是需要一定位宽的保证。而且高位宽的同步性也不像想象中的那么难以控制,DQS

的设计就很大程度地解决了这一问题,所以,DDR 可以借助较少的转产成本,较低的 PCB

成本(即使是 DDR-Ⅱ也是 6 层设计),成为 PC 内存的首选产品。

现在再去争论 RDRAM 与 DDR 谁胜谁败已经没有意义,RDRAM 已经很难再在主流市

场重振雄风。这主要不是它的技术限制,而是早期的市场动作与成本的压力造成的。虽然现

在 4i 芯片开始起步,但支持这种结构的芯片组还很难找到(至少 850E 不支持)。在 820 时

代,RDRAM 由于成本而没有打开市场,现在可以通过降低成本来提高竞争力,但 DDR 一

方也有了多通道技术。Rambus 也因此明智地将黄石定位于专用/定制市场。这样,在今后很

长一段时间里我们只有看 DDR 的独角戏了。

明日之星——DDR-Ⅱ与 DDR-Ⅲ(一)

作为 DDR 的接班人,DDR-Ⅱ在规范制定之初就引起了广泛的关注,进入 2002 年,三

星、Elpida、Hynix、Micron 等都相继发布了 DDR-Ⅱ芯片(最早由三星在 5 月 28 日发布),

让人觉得 DDR-Ⅱ突然和我们近了。可是,DDR-Ⅱ规范却一直没有正式公开,在 JEDEC 上

仍只有一篇 ATi 技术人员写的,在目前看来有些内容都已过时的简要介绍。

原来,DDR-Ⅱ标准到 2002 年 10 月完成度也没有达到 100%(厂商透露大约为 95%),

而上述厂商所推出的芯片也在不断的修改中,预计正式的规范将在明年第一季度推出。不过,

DDR-Ⅱ的主体设计已经完成,不会有大的改动,所以通过这些“试验性”芯片,我们仍可掌

握 DDR-Ⅱ的主要信息。

DDR-Ⅱ相对于 DDR 的主要改进如下:

DDR-Ⅱ与目前的 DDR 对比表

由于 DDR-Ⅱ相对 DDR-I 的设计变动并不大,因此很多操作就不在此详细介绍了,本文

重点阐述 DDR-Ⅱ的一些重要变化。

一、 DDR-Ⅱ内存结构

DDR-Ⅱ内存的预取设计是 4bit,通过 DDR 的讲述,大家现在应该知道是什么意思了吧。

上文已经说过,SDRAM 有两个时钟,一个是内部时钟,一个是外部时钟。在 SDRAM

与 DDR 时代,这两个时钟频率是相同的,但在 DDR-Ⅱ内存中,内部时钟变成了外部时钟

的一半。以 DDR-Ⅱ 400 为例,数据传输频率为 400MHz(对于每个数据引脚,则是

400Mbps/pin),外部时钟频率为 200MHz,内部时钟频率为 100MHz。因为内部一次传输的

数据就可供外部接口传输 4 次,虽然以 DDR 方式传输,但数据传输频率的基准——外部时

钟频率仍要是内部时钟的两倍才行。就如 RDRAM PC800 一样,其内部时钟频率也为

100MHz,是传输频率的 1/8。

DDR-Ⅱ、DDR 与 SDRAM 的操作时钟比较

所以,当预取容量超过接口一次 DDR 的传输量时,内部时钟必须降低(除非数据传输

不是 DDR 方式,而是一个时钟周期 4 次)。如果内部时钟也达到 200MHz,那外部时钟也要

达到 400MHz,这会使成本有大幅度提高。因此,DDR-Ⅱ虽然实现了 4-bit 预取,但在实际

效能上,与 DDR 是一样的。在上面那幅比较图中,可以看出厂商们的一种误导,它虽然表

示出在相同的核心频率下,DDR-Ⅱ达到了两倍于 DDR 的的带宽,但前提是 DDR-Ⅱ的外部

时钟频率也是 DDR 和 SDRAM 的两倍。在 DDR 的时钟频率已经达到 166/200MHz 的今天,

再用 100MHz 去比较,显然意义不大。这点也请大家们注意识别,上图更多的是说明 DDR-

Ⅱ内外时钟的差异。毕竟内部时钟由外部决定,所以外部时钟才是比较的根本基准。

总之,现在大家要明确认识,在外部时钟频率相同的情况下,DDR-Ⅱ与 DDR 的带宽

一样。

二、 DDR-Ⅱ的新操作与新时序设计

1、片外驱动调校(OCD,Off-Chip Driver)

DDR-Ⅱ内存在开机时也会有初始化过程,同时在 EMRS 中加入了新设置选项,由于大

同小异,在此就不多说了。在 EMRS 阶段,DDR-Ⅱ加入了可选的 OCD 功能。OCD 的主要

用意在于调整 I/O 接口端的电压,来补偿上拉与下拉电阻值。目的是让 DQS 与 DQ 数据信

号之间的偏差降低到最小。调校期间,分别测试 DQS 高电平/DQ 高电平,与 DQS 低电平/DQ

高电平时的同步情况,如果不满足要求,则通过设定突发长度的地址线来传送上拉/下拉电

阻等级(加一档或减一档),直到测试合格才退出 OCD 操作。

OCD 的作用在于调整 DQS 与 DQ 之间的同步,以确保信号的完整与可靠性

不过,据一些厂商的技术人员介绍,一般情况下有 DQS#(差分 DQS 时)就基本可以

保证同步的准确性,而且 OCD 的调整对其他操作也有一定影响,因此在普通台式机上不需

要用 OCD 功能,它一般只会出现在高端产品中,如对数据完整性非常敏感的服务器等。

2、片内终结(ODT,On-Die Termination)

所谓的终结,就是让信号被电路的终端被吸收掉,而不会在电路上形成反射,造成对后

面信号的影响。在 DDR 时代,控制与数据信号的终结在主板上完成,每块 DDR 主板在 DIMM

槽的旁边都会有一个终结电压岛的设计,它主要由一排终结电阻构成。长期以来,这个电压

岛一直是 DDR 主板设计上的一个难点。而 ODT 的出现,则将这个难点消灭了。

顾名思义,ODT 就是将终结电阻移植到了芯片内部,主板上不在有终结电路。ODT 的

功能与禁止由北桥芯片控制,ODT 所终结的信号包括 DQS、RDQS(为 8bit 位宽芯片增设

的专用 DQS 读取信号,主要用来简化一个模组中同时使用 4 与 8bit 位宽芯片时的控制设计)、

DQ、DM 等。需要不需要该芯片进行终结由北桥控制。

那么具体的终结操作如果实现呢?首先要确定系统中有几条模组,并因此来决定终结的

等效电阻值,有 150 和 75Ω 两档,这一切由北桥在开机进行 EMRS 时进行设置。

在向内存写入时,如果只有一条 DIMM,那么这条 DIMM 就自己进行终结,终结电阻

等效为 150Ω。如果为两条 DIMM,一条工作时,另一条负责终结,但等效电阻为 75Ω

在从内存读出时,终结操作也将在北桥内进行,如果有两条 DIMM,不工作的那一条

将会终结信号在另一方向的余波,等效电阻也因 DIMM 的数量而有两种设置

两个 DIMM 在交错工作中的 ODT 情况,第一个模组工作时,第二个模组进行终结操作,

等第二个模组工作时,第一个模组进行终结操作

现在我们应该基本了解了 ODT 的功能,它在很大程度上减少了内存芯片在读取时的 I/O

功率消耗,并简化了主板的设计,降低了主板成本。而且 ODT 也要比主板终结更及时有效,

从而也成为了提高信号质量的重要功能,这有助于降低日后 DDR-Ⅱ进一步提速的难度。但

是,由于为了确保信号的有效终结,终结操作期将会比数据传输期稍长,从而多占用一个时

钟周期的时间而造成总线空闲。不过,有些厂商的技术人员称,通过精确设置 tDQSS,可

以避免出现总线空闲。

3、前置 CAS、附加潜伏期与写入潜伏期

前置 CAS(Posted CAS)是为了解决 DDR 内存中指令冲突而设计的功能。它允许 CAS

信号紧随 RAS 发送,相对于以往的 DDR 等于将 CAS 前置了。这样,地址线可以立刻空出

来,便于后面的行有效命令发出,避免造成命令冲突而被迫延后的情况发生,但读/写操作

并没有因此而提前,仍有要保证有足够的延迟/潜伏期,为此,DDR-Ⅱ引入了附加潜伏期的

概念(AL,Additive Latency),与 CL 一样,单位为时钟周期数。AL+CL 被定义为读取潜伏

期(RL,Read Latency),相应的,DDR-Ⅱ还对写入潜伏期(WL,Write Latency)制定了标

准,WL 是指从写入命令发出到第一笔数据输入的潜伏期,不要将它和 tDQSS 弄混了,后

者是指 DQS 而不是数据。按规定,WL=RL-1,即 AL+CL-1。

在没有前置 CAS 功能时,对其他 L-Bank 的寻址操作可能会因当前行的 CAS 命令占用

地址线而延后,并使数据 I/O 总线出现空闲,当使用前置 CAS 后,消除了命令冲突并使数

据 I/O 总线的利率提高

设置 Posted-CAS 后,必须附加潜伏期以保证应有延迟,此时读取潜伏期(RL)就等于

AL+CL,从中可以看出 AL 的值为 CL+tRCD-1

DDR-Ⅱ中 CL 最低值为 3,最高为 5,并且不再有 x.5 的设计,而 AL 值则为 0-4。当 AL 设

为 0 时,前置 CAS 无效,即为传统 DDR 模式的操作。不过前置 CAS 在解决命令冲突的时

间也带来了新的问题——在背靠背式读取时,仍将经过 AL+CL 的潜伏期才能读取数据,比

传统的只有 CL 相比,读取的延迟反而增加了。因此,AL=0 是默认设置,只有在那些读写

命令非常频繁的操作场合,才建议启动前置 CAS 功能(如服务器等),对于台式机用户,前

置 CAS 的优点不足以抵消其带来的不利影响。

由于有了 AL,在同一行中进行再读取时,在 CL 的基础上仍将增加 AL 造成的延迟,

从而影响了性能

三、 DDR-Ⅱ未来发展与 DDR-Ⅲ

1、 DDR-Ⅱ 的发展计划

虽然目前多家厂商都推出了 DDR-Ⅱ内存芯片,但从 DDR 官方组织 JEDEC 方面得到的

信息表明,距离 DDR-Ⅱ内存大规模上市还很遥远,2004 年才会是 DDR-Ⅱ普通的阶段。而

由于三星、南亚与 Micron 公司的大力推广,这期间 JEDEC 很可能会接受 DDR-400 标准,

目前的争执主要在于能否在 DDR-I 的体系下保证 DDR-400 的可靠性。对此(成为 JEDEC

正式标准),三星与南亚公司都表示了很强的信心。

笔者认为,DDR-400 应该会获得认可,毕竟市场上是有需要的,而让市场去等一年的

时间迎接 DDR-Ⅱ 400 似乎并不现实。不过,多通道技术在 DDR 领域里的普及,可能也会

改变 JEDEC 对认证 DDR-400 的想法,但关键要看多通道的性价比能不能填补这一空档,否

则 DDR-400 就是一个最佳的选择(在完整/进阶版完稿之后又传来了 Intel 准备支持 DDR-400

的消息,可见 DDR-400 的前途)。

三星公司展示的 DDR-333(下)与 DDR-400(上)内存模组

三星是 DDR-400 的主推厂商,但请注意 DDR-400 的电压变化,它可能是引起兼容性问

题的根源之一

也由于多通道的出现,市场上对 DDR-Ⅱ的渴望也并不大,毕竟它与同频的 DDR-I 内存

的带宽一样。而从上文可以看出,DDR-Ⅱ相对于 DDR-I 的不同设计很多都集中在了如何在

更高的工作(时钟)频率下保证数据的可靠。只有当 DDR-Ⅱ依靠自身的特有功能与设计来

获得更高的时钟频率时,再配合多通道,才会真正拉开与 DDR-I 的距离,那时也就是 DDR-

Ⅱ普及的开始。但笔者预测 DDR-Ⅱ 400 将像 DDR-200 一样,注定是一个一出生就过时的

标准,DDR-Ⅱ至少要从 533 开始流行。不过在目前情况下,我们还不必太在意 DDR-Ⅱ的

进展情况,说句实话,它离我们还很远。今天的介绍只是让大家对其有一个大概的了解。

2、DDR-Ⅱ时代的封装技术

可以肯定的是 TSOP-II 将在 DDR-Ⅱ时代彻底退出内存封装市场。并且将会出现改良型

的 CSP——WLP(Wafer Level Packaging,晶圆级封装),它是比 CSP 更为贴近芯片尺寸的

封装方法,由于在晶圆上就做好了封装布线,因此在可靠性方面达到了更高的水平。不过,

外在的模样仍与现在的 CSP 封装差不多,WLP 更多的改进是在其内部。

另 外 值 得 一 提 的 是 为 了 应 付 更 高 容 量 的 需 求 而 采 用 的 SiP 封 装 技 术 , 它 是

System-in-a-Package 的缩写,有时又称之为 Stacked Pakage,可以看作是一种集成封装技术。

它将多枚内存芯片核心堆叠在一起,然后统一封装成一颗芯片,在有限的面积内通过充分利

用空间达到容量倍增的目的。SiP 并不是内存中专用的封装技术,原来是用于多种不同功能

的芯片统一封装(如一颗嵌入式 CPU+DRAM 芯片)。

目前的 SiP 技术可以在 CSP 的基础上最多堆叠 4 枚内存芯片

3、DDR-Ⅲ简介

DDR-Ⅲ的设计始于 2001 年 5 月,目前只有一个大概的规格。按照 JEDEC 的计划,DDR-

Ⅲ将在 2007 年正式出台,数据传输率至少从 667MHz 开始,预取数据容量大于 4bit(很可

能采用 RDRAM 那样的 8bit 设计),而且工作电压比 1.8V 更低,寄生干扰也将进一步减少。

显然,它离我们更是遥远,还不到谈论它还的时候,要知道半导体技术日新月异, DDR-

Ⅲ完全有可能因此而中途改变设计。在此,我们就当个小花边新闻吧。

内存模组是内存在 PC 系统中的最终体现形式,所以在本专题的最后,我们来简要谈谈

内存模的类型和未来的发展情况。不过,本章节只介绍 DIMM,而不涉及 RIMM(其实两

者的很多概念是相通的)。目前经常见到的模组主要有五种:

1、 Unbuffered DIMM:无缓冲型模组,这是我们平时所用到的标准 DIMM,分有 ECC

和无 ECC 两种,简称 Unb-DIMM。

2、 Regustered DIMM:寄存型模组,这是高端服务器所使用的 DIMM,分有 ECC 和

无 ECC 两种,但市场上几乎都是 ECC 的,简称 Reg-DIMM。

3、 SO-DIMM:Small Outline DIMM,小外型 DIMM,笔记本电脑中所使用的 DIMM,

分 ECC 和无 ECC 两种,DDR-Ⅱ时代仅有无 ECC 的型号。

4、 Micro-DIMM:微型 DIMM,供小型笔记本电脑或手持式设备使用的 DIMM。

5、 Mini-DIMM:DDR-Ⅱ时代新出现的模组类型,它是 Regustered DIMM 的缩小版本,

用于刀片式服务器等对体积要求苛刻的高端领域。

各类型内存 DIMM 对比表

三星公司 DDR-333 标准的 SO-DIMM,容量高达 512MB

本文将重点讲一下 Unb 与 Reg-DIMM,和未来模组技术的发展

一、Unb 与 Reg-DIMM 的区别

Unb 与 Reg-DIMM 的最大区别在于模组上有无寄存器。在高容量模组上,内存芯片数

量很多,而且在需要大容量内存的工作场合,内存模组的安插数量也是很多的,这使命令与

寻址信号的稳定性受到了严峻考验。很多芯片组的资料中都说明只有使用 Reg-DIMM 才能

达到标称的最高内存容量,从这点就能猜到寄存器的作用——稳定命令/地址信号,隔离外

部干扰。

Reg-DIMM 工作示意图,命令与地址信号通过寄存器中继传输至内存芯片

在工作时,命令地址信号会先送入寄存器进行“净化”并进入锁存状态,然后再发送至内

存芯片,芯片中的数据则不经过寄存器而直接传向北桥。由于要经过中继传输,所以内存操

作的时序也会因此而增加一个时钟周期,这是它所带来的一个弊端,但在高端应用中,内存

系统的稳定可靠的重要性远在性能之上,所以 Reg-DIMM 一般只用于高端市场,并且需要

芯片组的支持才行(主要是 Reg 所引起的时序变化)。而在高端设备中,ECC 基本都是必须

的,因此市场上的 Reg-DIMM 也都无一例外的是 ECC 型模组,虽然也有无 ECC 的 Reg-DIMM

设计标准。

另外,为了保证内存工作时钟的稳定,Reg-DIMM 上还要有一颗 PLL 对时钟信号对主

板发来的时钟信号进行跟踪/锁定。在 SDRAM 时代,这并不是必须的设计,但到了 DDR 时

代,由于对时钟的敏感性,PLL 成为了必备元件。

DDR 内存模组的结构图,寄存器与 PLL 是它相对于 Unb-DIMM 的最大不同

现在再回头看看 Unb-DIMM,就很明白了。它关键就少了寄存器,但为什么不称之为

Unregistered-DIMM 呢?其实,Buffered 与 Registered 是 Reg-DIMM 的两种工作模式,前者

在 Reg-DIMM 上并不常用,它是以时钟异步方式工作的,输出信号的再驱动不与时钟同步,

Registered 模式下输入信号的再驱动则与时钟同步。显然,Buffered 模式下的性能要更低一

些。不过,从原理上讲 Registered 模式也是一种缓冲操作,只是与时钟同步而已。在 SDRAM

的 Reg-DIMM 上 , Buffered 与 Registered 模 式 通 过 REGE 信 号 控 制 , 但 到 了 DDR

SDRAM-DIMM 时代,可能由于性能的原因 Buffered 模式被取消了。

在 Unb-DIMM 上,没有寄存器也就没了这个 Buffer,但它仍可具备 ECC 功能。这里需

要强调的是,ECC 与 Registered 是两码事,前者是在逻辑上保证数据的安全,后者是在物理

上保证内存系统的稳定工作。

德国 Infineon 公司推出的容量高达 2GB 的 PC2100 Reg-DIMM

没有我不行——内存模组(下)

二、DIMM 引脚的基本设计

讲完 Unb-DIMM 与 Reg-DIMM 的不同之后,现在我们来看看 DIMM 引脚上的不同。其

实,从内存芯片的引脚上就能推断出一些 DIMM 的引脚,因为芯片最终要通过 DIMM 来与

主板打交道的。

首先,DIMM 肯定要有 64 个引脚用来数据的传输,而且要有 Ax 地址线、L-Bank 地址

线、片选、数据掩码、电源、RAS、CAS……等信号,另外,ECC 型与 Reg 型 DIMM 要有

额外的标定引脚,下面我就以 SDRAM 和 DDR SDRAM 为例,分 Unb-DIMM 和 Reg-DIMM

来介绍一下 DIMM 都包含有哪些的引脚。

从上面的引脚信号列表中,大家应该能了解到 DIMM 的大体情况了。其中很多信号定

义是不是非常熟悉?从中可以看到,在 DDR SDRAM 时代已经为 8 个 L-Bank 做好了准备,

但业界显然没有利用到它,不光是内存厂商,DDR 芯片组中似乎没有支持 8 个 L-Bank 的设

计。还有就是 CS 信号,从 SDRAM 到 DDR,都有 4 个 CS 的设计,但目前的 DIMM 还都

是双 P-Bank 的设计,不同的是,SDRAM-DIMM 上,4 个 CS 是必须的,两个 CS 对应一个

P-Bank 芯片集,但到了 DDR 时代,可能是技术与工艺的进步,一个 CS 就控制了一个 P-Bank。

总之,当我们了解了芯片的引脚设计后,对 DIMM 的引脚组成也就不再陌生。有兴趣的读

者,可以自行深入研究。

三、QBM 型 DIMM

之所以在前文没有介绍四倍带宽内存(QBM,Quad Band Memory),就是因为不是针对

芯片的技术,而针对 DIMM 的技术。它诞生于 DDR 时代,是 Kentron 公司为了解决 DDR

带宽提供困难而提出的设计方案。主要的思路就是让 DIMM 上的两个 P-Bank 交错工作,而

交错的时钟周期为原始时钟的 1/4,即相位相差 90 度。

QBM 的工作时序图,第二个 P-Bank 的工作时钟与第一个 P-Bank 相差 90 度(1/4 周期),

这样在第一个 P-Bank 时钟的高/低电平中部就是第二个 P-Bank 的触发点,两者都是 DDR 传

输,从而在一个时钟周期内完成 4 次数据触发,实现四倍带宽

为了控制两个 P-Bank 中同一位置的芯片交错工作,模组上要为每组芯片(在 QBM 模

组上,一个 P-Bank 位于一侧,两个 P-Bank 中位置相对的芯片为一组)设置一个开关,以控

制不同 P-Bank 间的通断。并且还要为延迟 1/4 周期的 P-Bank 提供一个 PLL 以保证相位差

的准确性。

QBM 的设计是非常巧妙的,经过对现有的 DDR 模组的改装,配合新的芯片组即可将带宽

提高一倍,有点类似于 32bit RIMM,在一个模组上实现了双通道的功能,只是 QBM 不是

双通道并发,而是双通道交错,通过更高的传输频率实现高带宽。但是新增加的开关与 PLL

元件将增加一定的成本,不过与其所能提供的带宽相比,还是比较划算的。

Kentron 公司给出的 QBM 与其他内存方案的成本比较表,从中可以看出 QBM 有较高的性

价比

但是,开关元件的同步性对于 QBM 是个考验,时钟频率越高,对开关的控制精度就越

高。目前,有不少大牌的模组厂商(如 Infineon)都在论证 QBM 的可行性与可靠性,据部

分厂商透露,在使用 DDR-333 或之前标准时,QBM 的表现良好,但到了 DDR-400,QBM

的可靠性就会降低,如果克服这一个问题,那么延迟又会大幅提高。所以,QBM 目前的可

行标准是 QBM533(DDR-266)和 QBM667(DDR-333)。VIA 在 P4X800 中将要支持的标

准也是 QBM533,虽然不能使用 DDR-400,但它的 5.4GB/s 带宽(QBM667)在目前仍是无

敌的。

不过,由于 QBM 是针对模组的技术,所以理论上 QBM 可适用于任何 DIMM,包括

SDRAM 和 DDR-Ⅱ的 DIMM,Kentron 也有此计划研制 QBM 型 DDR-Ⅱ DIMM,以保持

QBM 的生命力。另外,Kentron 已将 QBM 标准上报 JEDEC 审批,目前还不知能否通过。

很多模组厂商也都在观望,毕竟 QBM 转产是很容易的,就看市场情况了。所以,QBM 虽

然设计巧妙,但得到的支持并不强劲,以 Kentron 及 QBM 联盟的生产能力,显然不足以完

成普及任务,一切就看 P4X800 的市场效果了。

三、模组的堆叠装配

当内存芯片容量无法迅速提高的时候,高容量模组如何设计就体现了厂商间的真正实

力,由于高容量模组针对的是高端应用市场,所以谁能在容量上有所突破就意味着滚滚商机。

就模组而言,芯片基本是固定的,所以芯片堆叠装配(Stack Assembly)技术就是增加容量

的首选。

这方面除了 Elpida、Kentron、Kingston 等公司较早以前提出的 TCP、FEMMA、EPOC

等堆叠形式外(已有多篇文章介绍过,在此不再重复),著名的封装技术开发商 Tessera 公司

(它在 1990 年因研制出 CSP 封装而闻名于世)近期宣布了他们的 4 枚芯片堆叠装配的模组

技术(TCP 与 EPOC 都是两芯片堆叠)——μZ Package,当然,芯片本身的封装也要有相应

的调整。而 Infineon 公司也推出了普通 TSOP-II 技术的双芯片堆叠装配技术。显然,模组厂

商都想利用有限的空间(毕竟在主板上插槽之间的距离是有限的)尽量提高装配容量,若再

配合 SiP 封装形式的内存芯片,DIMM 的扩容就如虎添翼了。

Infineon 的采用 TSOP-II 堆叠封装的模组,容量高达 2GB

Tessera 公司为高容量模组开发的 4 枚芯片堆叠装配技术 μZ Package