基于FPGA 的PLC 梯形图/IEC61499 功能块硬件实现

许多PLC是采用通用MCU 实现,PLC 内部运行时是通过软件实现的。应用程序执行的方法有两种,一种是将IEC61131-3的梯形图,ST,IL转换成为一种中间语言,由PLC 运行时解释执行,另一种方法是将IEC61131-3 的应用直接通过编译器翻译成为PLC 内部MCU 的二进制执行代码,下载到PLC 内部存储器中直接执行。无论是哪一种方式,它们都是软件为主实现的。不同厂商的PLC 会采用不同的方式来提高运行时的执行效率,比如采取更高速率的MCU,RTOS和高速内部总线(例如PCIe总线),也有一些PLC 内部包含了FPGA 芯片,通过硬件来实现某些需要高速响应的控制和算法。例如高速脉冲计数,PWM 信号,高速模拟量采集和预处理,运动控制算法,电机同步解码等等。

硬件实现IO外围电路和算法无疑提高了PLC 的实时性,但是也降低了编程的灵活性和运行时的复杂性。

PLC中的FPGA 主要是提供了某些功能的协同操作,PLC 梯形图的周期执行仍然是由软件在RTOS 的支持下执行的。用户编写的梯形图的执行仍然受到软件执行速度的限制。国外研究人员也尝试使用FPGA 的verilog 语言来编写PLC 梯形图周期执行的算法。实现了ladder to verilog 转换的研究工作。

同样地,对于IEC61499 标准中的功能块,目前大多数是通过软件来实现的,有些IEC61499 的运行时使用java 来实现功能块,有些则采用ST语言来实现功能块,通过开发工具(IDE)将ST语言转换成为C/C++ 语言,再进一步转换成为PLC 内部MCU 的目标程序。也就是说,IEC61499 功能块和运行时是基于软件实现的。面对实时性要求高的应用场景,例如运动控制环,高速数据采样,高速PID 等。IEC61499 功能块网络的实时性如何保证?是至关重要的。

能否使用FPGA 来实现部分IEC61499功能块的“硬件化”?提高IEC61499 的执行效率。理论上是完全可能的,但是还没有发现有人尝试这样做,没有找到这方面的文章。

基于FPGA的梯形图

梯形图

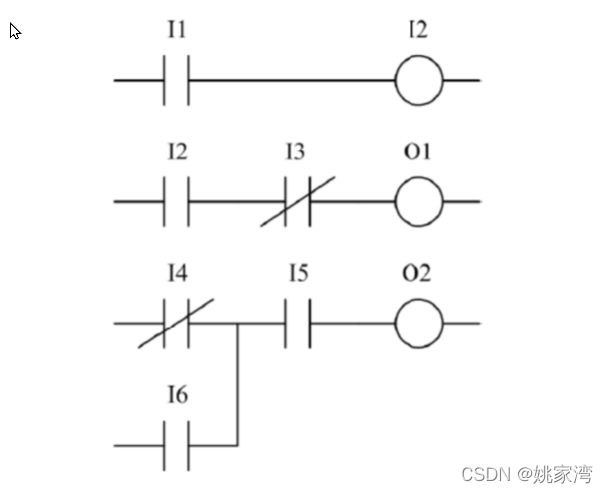

梯形图(Ladder Diagram)是编写PLC 控制逻辑最常用的方法,这种方法被IEC61131-3 标准化。每个梯形图由横杠rungs 构成,每一个横杠都是一个逻辑表达式,表达式中的输入是系统的输入和内部状态,同样地,表达式的输出是系统的输出或者内部变量。下面是一个典型的梯形图:

在这个例中中,内部变量I2 赋值为输入I1,输出O1 赋值为I2 AND NOT I3 ,而O2 赋值为((NOT I4)OR I6)AND I5.

P LC 的梯形图是周期性执行的,在每个执行周期,从上至下,从左到右地执行,只有在梯形图执行完成后,才更新输出值。

为什么需要使用FPGA来实现梯形图

在现代工业控制器中使用的处理器通常是普通的通用微处理器。现代微处理器设计的数据管道和缓存器等技术都是用来改善平均的性能(average performance),而不是极限情况性能(worst case performance)。在一个实时系统中,极限情况下性能需要保证的。通常采用超指标的(over-specified)处理器来满足时间的需求。这样做增加了系统的成本。

FPGA 中的可配置逻辑(Reconfiguration logic)是为特定的应用量身定制的,能建立高性能的系统。由此看来,FPGA 中的逻辑适合控制器的二进制操作。

安全敏感的系统需要多重处理通道,这些处理通道可能是各不同的,也可能是冗余的。通常需要单处理器计算许多次,也可能是多处理器并行处理。FPGA 允许在一个芯片上多个计算核并行操作。从而使单一或者冗余计算在一个设备上完成。

国外学者比较了梯形图执行的各种方法表明,硬件FPGA 的梯形图执行要比其它方式提升20~600倍。

这是一个令人激动的结果。

基于FPGA 的IEC61499 功能块和功能块网络的实现

对于IEC61499 而言,目前没有找到国外学者的研究报告,笔者认为完全可以使用FPGA 的逻辑在提升IEC61499 功能块以及功能块网络的执行性能。将 IEC 61499 模型部署到 FPGA 可以利用 FPGA 的并行执行能力,从而能够处理同时发生的事件和并行执行算法

相比IEC61131-3 梯形图。IEC61499 功能块的FPGA 实现可以有如下几种方式:

- 将需要大量算力的功能块有FPGA来实现,例如数字信号处理,滤波,FFT等算法由FPGA 来完成。

- 将对实时性要求高的执行程序构建成为符合功能块,而复合功能块内部的简单功能块编译成为verilog 语言,通过fpga 的开发工具编译成为FPGA 的bitstream 下载到FPGA 中运行。这种功能块可以是PID 控制环。如此一来,PID 的控制环完全是硬件执行的,没有任何软件的参与。控制环的实时性得到保证。

在IEC61499 功能块中嵌入PLC 梯形图运行时

受到基于FPGA 的IEC61499 功能块 的启发,完全可以将FPGA PLC 梯形图的运行时封装到IEC61499 功能块中,我们不妨称其为PLC 功能块。如此一来,能够在一台设备中并行地运行多个PLC 梯形图!

实现的思考

FPGA 中的逻辑通常使用verilog、HDL 硬件逻辑设计语言来实现。完全由能力来设计梯形图和IEC61499 功能块的内部算法和状态图。

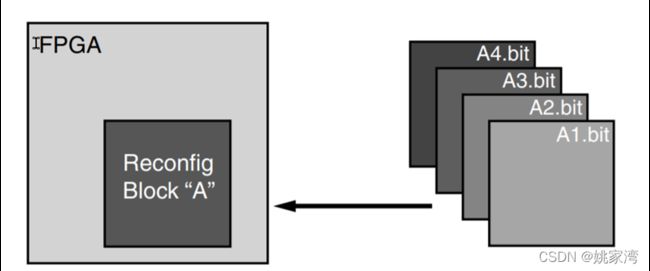

为了能够动态地实现不同梯形图和功能块的执行,需要利用现代FPGA 的部分动态配置功能。所谓局部从配置FPGA 功能是指,在FPGA 中预留一部分区域,通过FPGA与处理器之间的接口,动态地下载不同的控制逻辑的bitstream。

如此一来,PLC运行时将实现梯形图的bitstream 下载到某一个Reconfig Block 中,就可以实现梯形图的执行的。不同的控制算法使用不同的bitstream 文件。IEC61499 功能块也是如此,将功能块或者复合功能块的bitstream 装载到某一个ReconfigBlock 中运行。

结论

为了满足某些对实时性要求比较高的应用,完全可以利用FPGA 提高PLC 运行时的性能。利用现代FPGA的动态局部再配置的功能,能够实现梯形图和IEC61499 功能块的硬件执行。其性能能够大幅度的提高。

事实上,美国NI 公司的labview 中FPGA 采取了类似的方式,它采用了图形化设计功能实现FPGA 的控制逻辑,下载到背板FPGA 中运行。而IEC61499 同样是基于图形的设计方法,完全能够替代labview 的图形设计方法。这是非常有趣的研究方向。

(本文在不断完善中)