数字逻辑学习总结-MOOC数字逻辑设计

目录

-

- ·指令周期

- 一.数字逻辑基础

-

- 1.十进制与原码、反码、补码之间的转换

- 2.移位

- 3.操作符

-

- 按位与运算

- 按位或运算

- 按位异或运算

- 另外: x|=y; x&=~y

- 二.逻辑门和逻辑代数

-

- 1.逻辑门

- 2.逻辑函数

-

- 逻辑代数基本运算定律

- 卡诺图化简法.

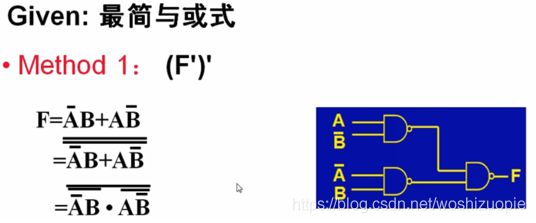

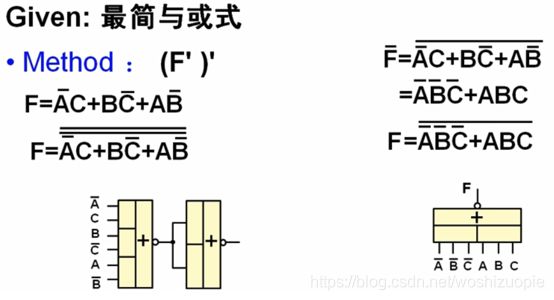

- 3.利用单一逻辑门设计两级门电路

- 三

-

- 译码器

- 锁存器和触发器

-

- 双稳态触发器

- 基本RS锁存器(或非门)

- 基本RS锁存器(与非门)

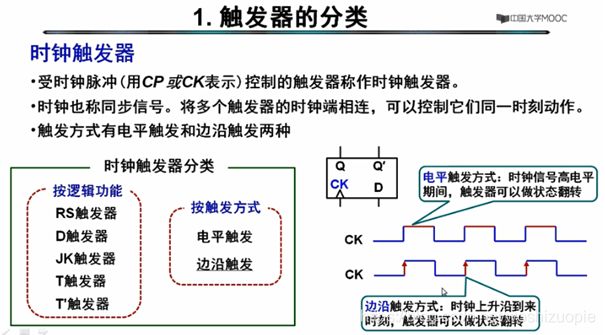

- 触发器

-

- D触发器

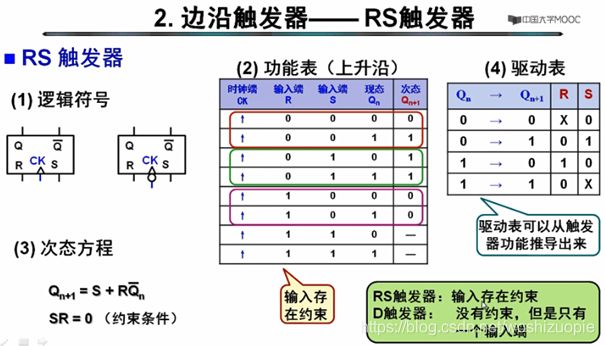

- RS触发器

- JK触发器

- 实际应用电路-I/O电路

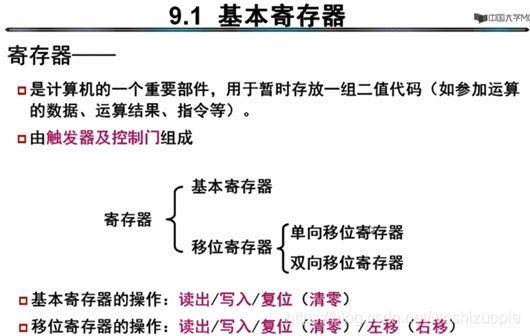

- 时钟逻辑部件-寄存器

-

- 基本寄存器的应用:利用三态总线进行数据传送

- 移位寄存器

-

- 串入/并出(Serial in/Parallel out)

- 双向移位寄存器

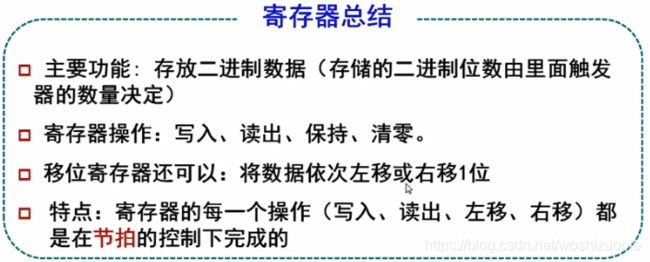

- 寄存器总结:

- 时钟逻辑部件-计数器

-

- 异步计数器

-

- eg:

- 异步计数器总结:

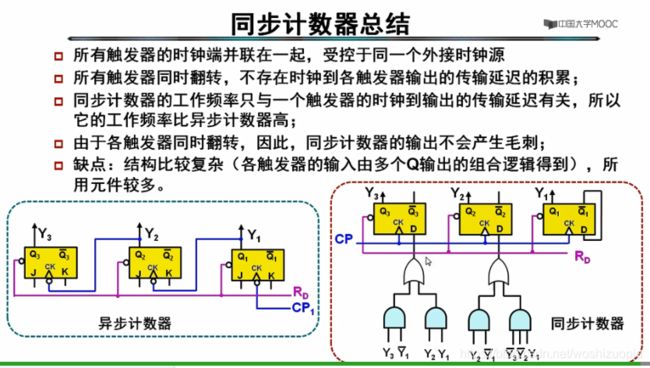

- 同步计数器

-

- eg:

- 同步计数器总结:

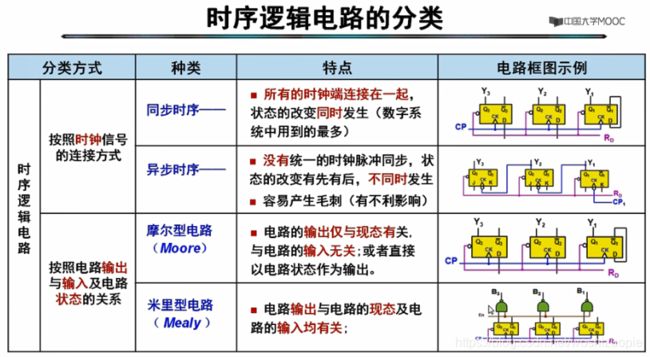

- 时序逻辑电路的分析方法:

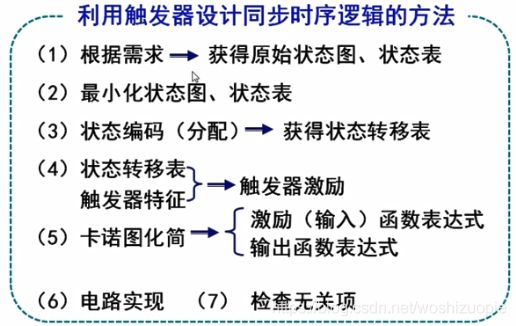

- 利用触发器设计同步时序逻辑

参考:

1. 数字逻辑知识点复习.

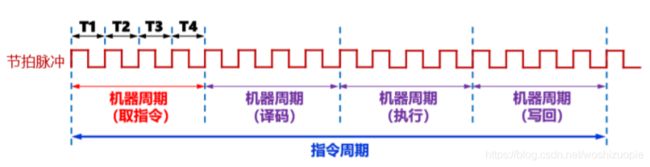

·指令周期

指令周期:CPU从内存取出一条指令并执行的时间。

机器周期:又叫CPU周期,CPU从内存取出一条指令的最短时间。

时钟周期:又叫节拍脉冲、震荡周期。

指令周期包含多个机器周期,机器周期包含多个时钟周期。

一.数字逻辑基础

1.十进制与原码、反码、补码之间的转换

1.正数的反码、补码和原码相同。

2.负数:

······在计算机中,负数以原码的补码形式表达。

书上原文:

①原码:用符号位和数值表示带符号数,正数的符号位用0表示,负数的符号位用1表示;数值部分用二进制形式表示。

②反码:正数的反码与原码相同,负数的反码为对该数的原码除符号位外各位取反。

③补码:正数的补码与原码相同,负数的补码为对该数的原码除符号位外各位取反,然后在最后一位加1。

eg:

假设有一个int型的数,值为5,那么它在计算机中表示为:

00000000 00000000 00000000 00000101

因为int类型的数占用4个字节(32位)。

那么-5呢?

-5的原码:10000000 00000000 00000000 00000101

-5的反码:11111111 11111111 11111111 11111010

-5的补码:11111111 11111111 11111111 11111011

所以-5在计算机中表达为11111111 11111111 11111111 11111011,转换为十六进制为0xFFFFFFFB。

又eg:

-1的原码:1000 0001

-1的反码:1111 1110

-1的补码:1111 1111

-10的原码:1000 1010

-10的反码:1111 0101

-10的补码:1111 0110

2.移位

3写成二进制数是0000 0011;-3写成二进制数是(补码)1111 1101。

程序执行的时候,操作的是数值的编码表示,也就是数值在内存中的二进制表示。比如说,程序取-3的时候,就去取1111 1101。

(1)对无符号数3来说,x<<1往左移一位,最左边的位移掉了,最右边的移进来的位补零。变成0000 0110,所以结果是6;x>>1往右边移一位,由于是无符号数,所以逻辑右移,最右边一位移掉,最左边移进来的位补零,变成0000 0001,所以结果是1。

(2)对于有符号数3来说,x<<1往左移一位,最左边的位移掉了,最右边的移进来的位补零。变成0000 0110,所以结果是6;x>>1往右边移一位,由于是有符号数,可能发生逻辑右移,也可能发生算术右移,这一点,C标准并没有明确地指定是使用逻辑右移还是算术右移。但大多数的机器都使用算术右移,变成0000 0001,所以结果还是1。

(3)对于有符号数-3来说,x<<1往左移一位,最左边的位移掉了,最右边的移进来的位补零。变成1111 1010,结果是-6。往右移一位,由于是有符号数,可能发生逻辑右移,也可能发生算术右移。大多数机器使用算术右移,变成1111 1110,结果是-2。

总结:左移时总是移位和补零。右移时无符号数是移位和补零,此时称为逻辑右移;而有符号数大多数情况下是移位和补最左边的位(也就是补最高有效位),移几位就补几位,此时称为算术右移。

3.操作符

按位与运算

参与运算的数以补码方式出现。

例如:9&5可写算式如下: 00001001 (9的二进制补码)&00000101 (5的二进制补码)=00000001 (1的二进制补码),可见9&5=1。

按位与运算通常用来对某些位清0或保留某些位。例如把a 的高八位清 0 , 保留低八位, 可作 a&255 运算 ( 255 的二进制数为0000000011111111)。

按位或运算

参与运算的两个数均以补码出现。

例如:9|5可写算式如下: 00001001|00000101=00001101 (十进制为13),可见9|5=13。

按位异或运算

参与运算数仍以补码出现,例如 9 ^ 5可写成算式如下: 00001001^00000101=00001100 (十进制为12)。

另外: x|=y; x&=~y

x|=y; 等价于x=x|y,为位运算里面的或;

x&=~y 等价于 x=x&(~y); 先对y取反,再和x做与运算。

二.逻辑门和逻辑代数

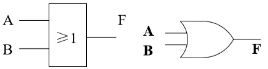

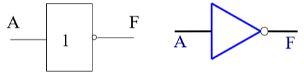

1.逻辑门

与门:F = A · B = AB

或门:F = A + B

非门:![]()

复合逻辑门:

2.逻辑函数

逻辑代数基本运算定律

卡诺图化简法.

3.利用单一逻辑门设计两级门电路

三

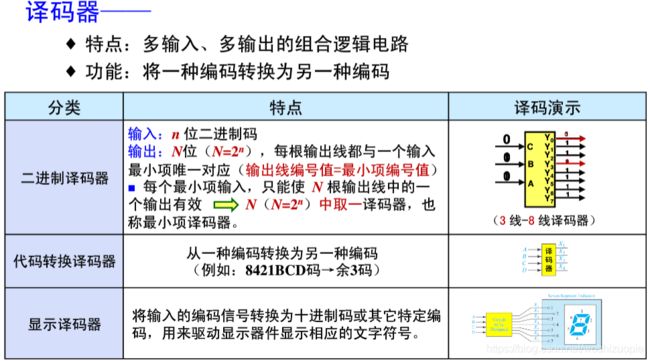

译码器

计算机在处理各种文字符号或数码时,必须把这些信息进行二进制编码,在编码时所使用的第一种二进制代码状态都赋予了特定的含义,即表示一个确定的信号或者对象,实现这种功能的电路叫编码器,如用于键盘的BCD码,ASCII码编码器等。

译码是编码的逆过程,在编码时,每一种二进制代码,都赋予了特定的含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义“翻译”出来的过程叫做译码,实现译码操作的电路称为译码器。或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

经常用到的74318就是一个三线-八线译码器。

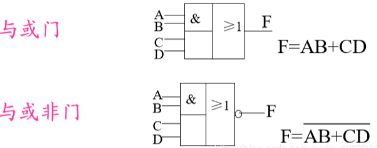

锁存器和触发器

组合逻辑电路的特点:

是一种无记忆电路—输入信号消失,则输出信号也会立即消失;

电路输出端的状态完全由输入端的状态决定;

有时需要将参与运算的数据和运算结果保存起来,即在组合逻辑电路的输出端添加具有记忆功能的部件,也就是存储电路。锁存器和触发器就是构成存储电路的基本电路单元。

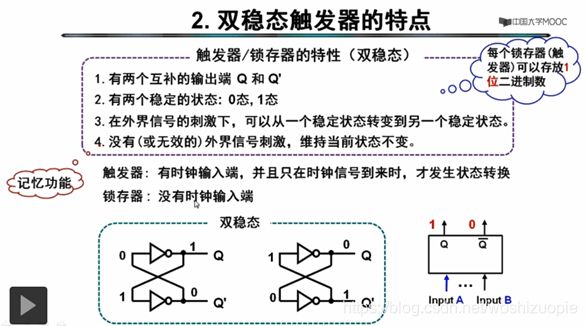

双稳态触发器

(1)是0态还是1态,看Q端的输出结果;

(2)每个锁存器(触发器)可以存放1位二进制数,因此如果要存在n位二进制数,就需要n个锁存器/触发器;

(3)所谓的稳定状态,是指当前的输出端维持不变。

(4)图示框中的双稳态例子,是由两个反相器经过交叉耦合构成的一个逻辑电路:如果Q端当前稳定在1态,经过反相器的反馈之后,Q’端就会是0态,这个0态又会通过上边的反相器加强1态的输出。

·

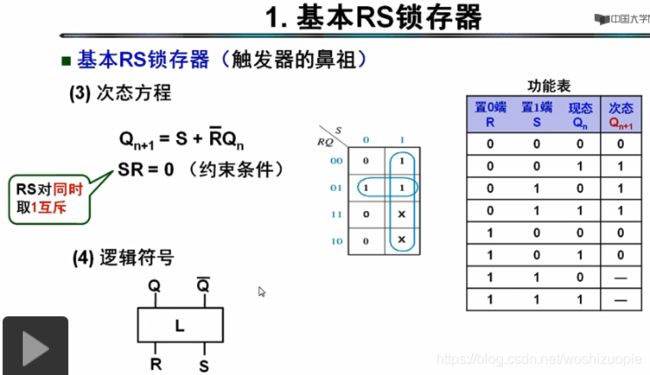

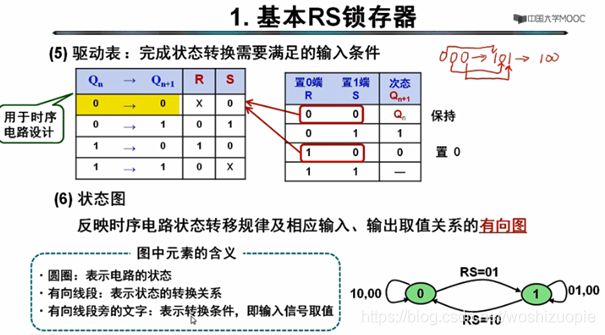

基本RS锁存器(或非门)

(1)或非门:对输入信号高电平敏感,也就是说,有n个输入端的或非门,随便给其中任何一个输入端一个高电平1,这个或非门的输出就是低电平0。

(2)功能表中体现的就是两个关注点,也就是说,当前电路的现态是什么,在输入信号R和S的作用下,它的次态会是什么?

(3)对于表中所示两个输入端给0,相当于输入了两个无效的刺激信号,所以次态不会发生改变,即保持功能;

······当R端输入高电平1,S端输入低电平0,根据或非门的特点(对高电平敏感),图中的1号或非门的输出端Q会变成低电平0,这个0反馈回来和S=0同时作用于2号或非门,使其输出端为高电平1,也就是说这个逻辑电路的次态会变成0态。所以说,当R=0,S=1,无论现态是0还是1,它的次态都是0,即置0功能;置1功能同理;

······R和S如果都是高电平1的话,Q和Q’端都是0,违背了双稳态触发器的特点(Q和Q’互补),所以RS对同时取1是互斥的。

·

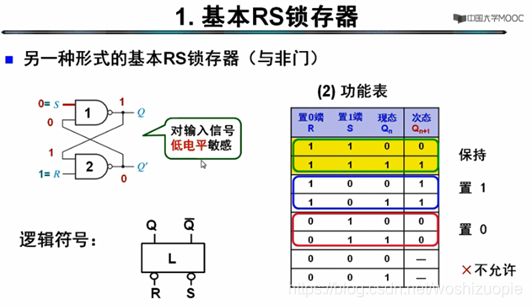

基本RS锁存器(与非门)

触发器

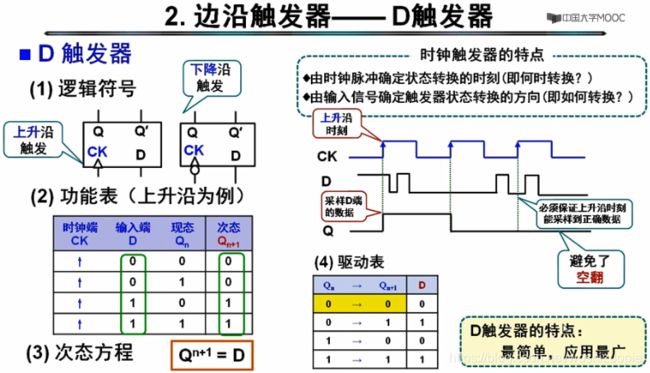

采用电平触发方式时,当时钟信号是高电平,如果D端存在干扰,Q端会输出错误的波形,即发生空翻现象。

边沿触发方式可以避免空翻现象。

·

D触发器

(1)逻辑符号中,没小圆圈代表上升沿触发,有代表下降沿触发;

(2)在第一个上升沿时刻到来时采样D端的数据,维持到下一个上升沿到来后再次采样。

·

RS触发器

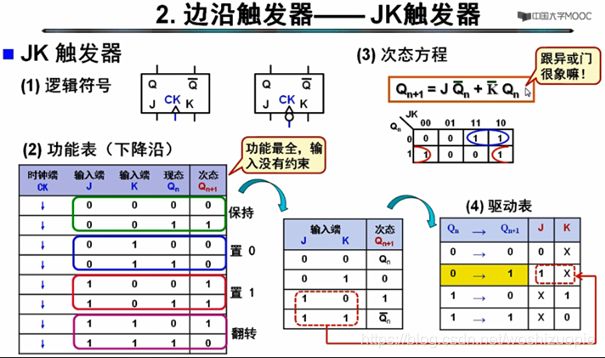

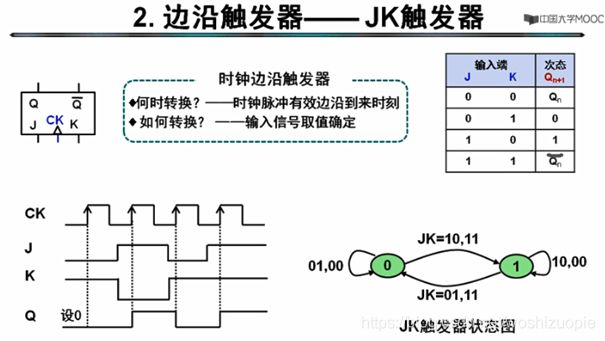

JK触发器

JK触发器有两个输入端,且之间没有约束。

两个输入端:J和K;

两种触发方式:上升沿或下降沿;

驱动表:是从功能表推出来的。在驱动表中主要关注:触发器从现态到次态完成对应的转换,J端和K端应该给什么样的信号。

·

第一个上升沿到来的时候,J和K的取值是0,1,根据功能表得到,此时是置零功能,次态为0;这个0保持到第二个时钟上升沿到来,J和K取值为1,0,是置一功能,决定了触发器的状态转变为1…

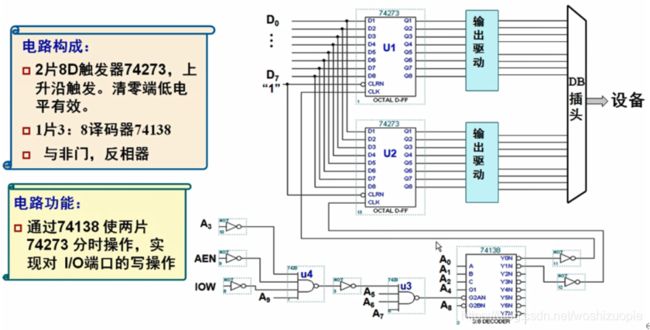

实际应用电路-I/O电路

1.两个74273的清零端“CLRN”连在一起,有小圆圈代表低电平清零,图中送的是高电平1,说明在后续操作中不执行清零操作。

2.两个芯片中集成的D1-D8共8个D触发器,分别连接在D0-D7这8条数据总线上;两个芯片的时钟端分别连接在74138芯片的输出端Y0和Y1;下边的A0-A9是地址总线。

3.对于38译码器这个芯片,它的功能是:如果该芯片不工作在译码状态下,它的所有输出端Y0-Y7均为高电平1,反向后,两个74273芯片的CLK初始为低电平0。

4.假如需要译码器处于译码状态下,首先需要它的三个使能端G1,G2A,G2B处于1,0,0。可得如下表:

如果想让Y0被译中,则译码器的三个地址输入端C,B,A对应连接的地址总线A2,A1,A0为0,0,0。如果想让Y1被译中,则译码器的三个地址输入端C,B,A对应连接的地址总线A2,A1,A0为0,0,1。(个人理解000-Y0,001-Y1,…,111-Y7)

5.Y0被译中后,Y0输出为0,U1的CLK端输入为1,U1获得一个上升沿,使得连接到U1上的D0-D7的数据被送往外围设备,也就是将执行对I/O端口(2F0H)进行写操作。

即该电路的功能就是通过74138使U1、U2进行分时操作。

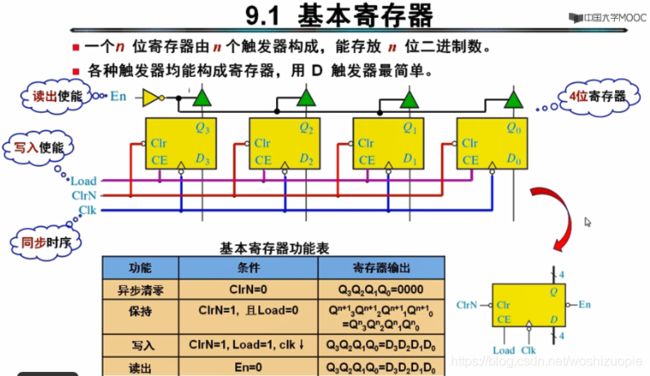

时钟逻辑部件-寄存器

四个时钟端连在一起,受控于同一个外界时钟源,这种连接方式称为同步时序,也就是说这四个D触发器会在同一时刻进行状态改变。

异步清零功能:下图中,四个清零端连在一起,用ClrN表示,清零是低电平有效,所以给ClrN赋0,它的四个输出全是0。这种清零不需要等待时钟信号的到来,所以是异步清零。

·

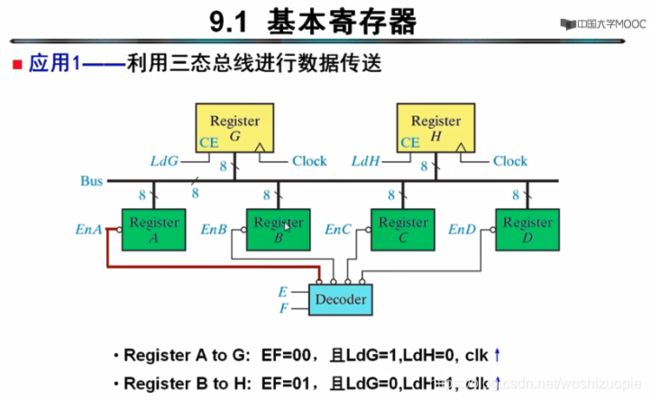

基本寄存器的应用:利用三态总线进行数据传送

首先,译码器的输入端E、F送0,0,译码器的输出使寄存器A的使能端有效,也就是说寄存器A被选中;同时寄存器G的使能端信号LdG=1,寄存器H的使能端信号LdH=0。在时钟上升沿的时刻,寄存器A中的数据经由总线送到寄存器G中。同理,译码器的输入端E、F送0,1,寄存器B被选中。

·

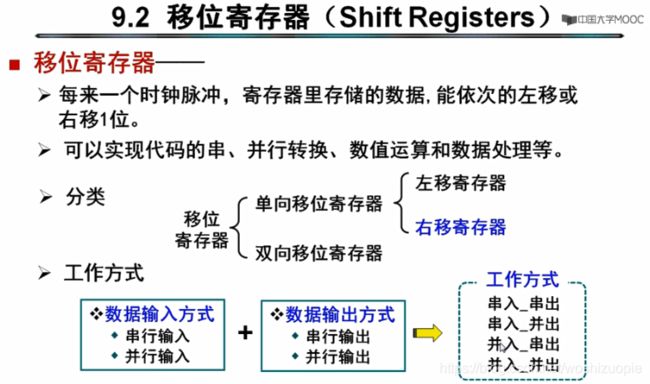

移位寄存器

·

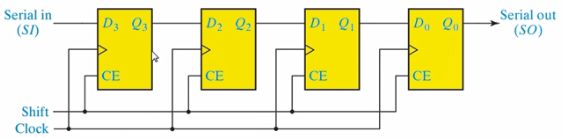

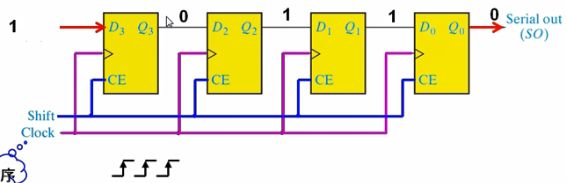

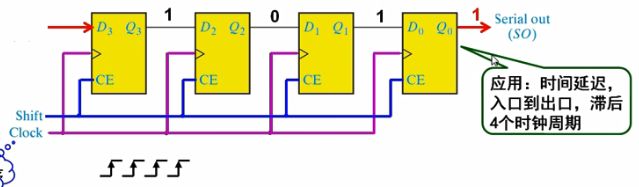

以右移寄存器为例:串行输入、串行输出的单向右移寄存器

逻辑图如下,由四个D触发器组成:前面触发器的Q输出作为后边触发器的D输入;所有触发器的时钟端连接在一起,受控于同一个外界时钟源Clock,称为同步时序;这个电路中有一个输入端Serial in(SI)称为串行输入,移位路径上最后一个触发器的输出Serial out(SO)作为整个电路的输出。

·

下面分析一下这个电路的功能:

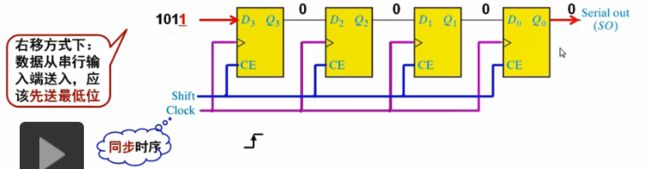

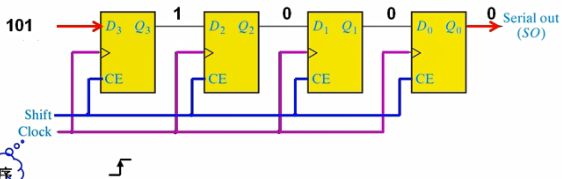

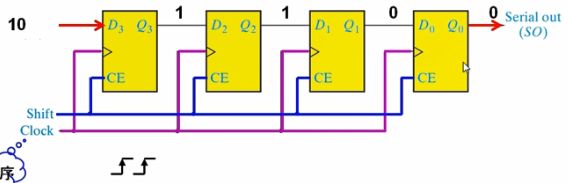

假设当前所有触发器的Q端都是0状态,现在要把一个四位二进制数1011写入到移位寄存器中。

右移方式下,数据从串行输入端送入,应该先送最低位。

首先先让使能端送有效的高电平;当第一个时钟上升沿到来后,D3端的1会出现在Q3端。

第一个时钟沿过后,

第二个时钟沿过后,

第三个时钟沿过后,

第四个时钟沿过后,

·

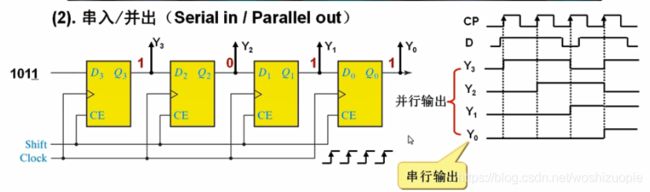

串入/并出(Serial in/Parallel out)

Y0、Y1、Y2、Y3为并行输出,若是单独只取其中一个,则为串行输出。

·

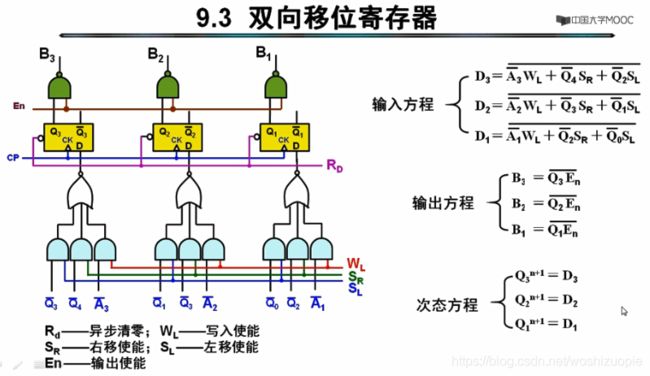

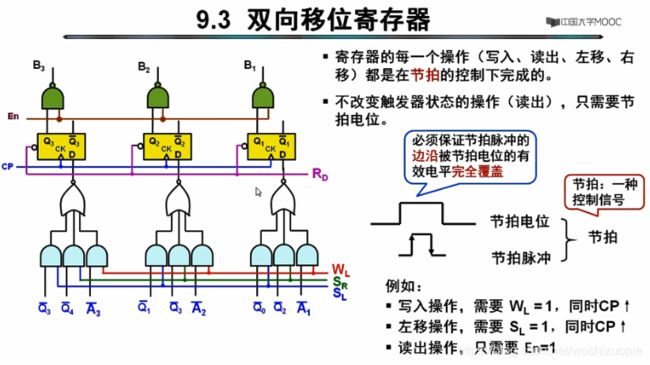

双向移位寄存器

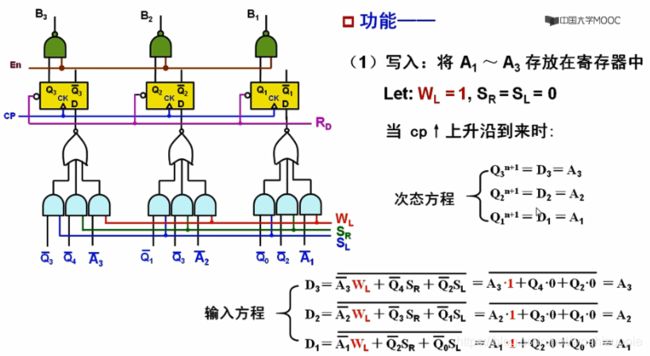

组成:3个D触发器,同步时序,每个触发器的D输入端都是由与门和或非门形成的组合逻辑,输出端是由3个与非门形成的控制逻辑。Rd代表异步清零信号,它送低电平0的话,三个D触发器的Q端都是0状态。

功能:

(1)执行写入操作,就不能再同时执行左移和右移操作;

根据输入方程,可知此时输入数据A1,A2,A3已经等待在D触发器的门口;

把数据送到寄存器当中的条件:在写入使能信号为高电平时,还需要时钟信号为上升沿。

在时钟上升沿到来的时候,触发器做状态改变,数据会被存放到触发器(或寄存器)中。

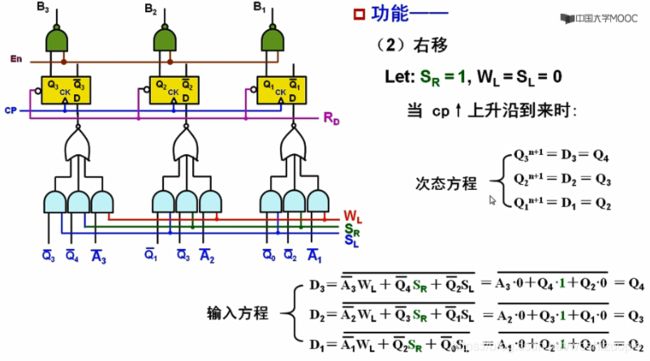

(2)右移

右移使能信号为高电平,左移和写入使能为低电平;

从输入方程可以看出,它把高位触发器的输出送给低位触发器做输入,即右移功能;

在时钟上升沿到来的时刻,触发器做状态的改变,执行右移功能。

(3)左移:

(4)读出:

·

·

寄存器总结:

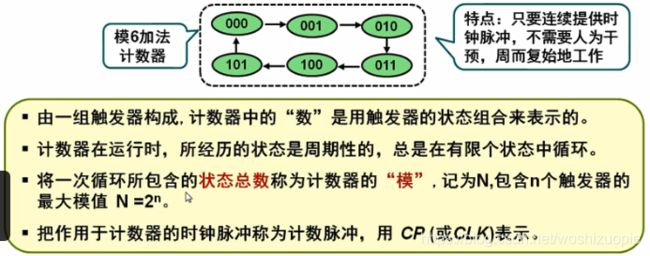

时钟逻辑部件-计数器

一种能在输入信号作用下依次通过预定状态的时序逻辑电路,是数字系统和计算机广泛使用的逻辑器件,可用于计数、分频、定时、控制、产生节拍脉冲(顺序脉冲)和序列脉冲等。

比如下图所示是某个计数器的状态图,其中的每一个状态都代表计数器的一个数,这个数是由三个触发器的状态组合表示的。

计数器的种类:

(1)按时钟方式分为:同步、异步;

(2)按功能分为:加法、减法、可逆;

(3)按计数方式分为:二进制、十进制、M进制。

异步计数器

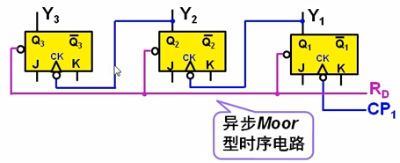

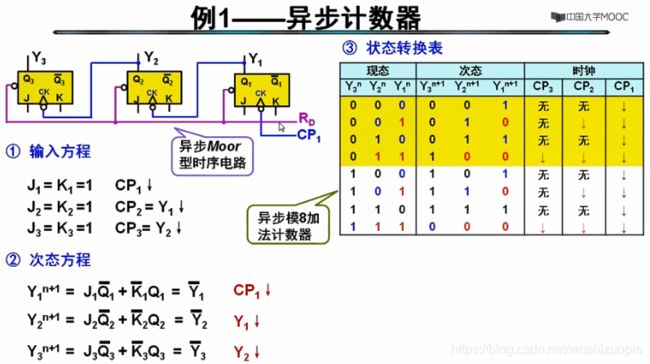

给定一个时序逻辑电路,首先需要关注它的时钟连接方式。如下图所示,有三个JK触发器(下降沿触发),它们的时钟端没有连接在一起,所以是异步时序;该逻辑电路的输出直接以触发器的状态作为输出,所以它是异步Moor型时序电路。

分析:

首先,三个JK触发器的J、K端都是悬空,对于TTL电路,悬空相当于接入高电平;第一个触发器的时钟端来源于外接时钟源,所以它是在CP1的下降沿触发;第二个触发器的时钟端连接的是第一个触发器的Q1输出端,所以它是在Y1的下降沿触发。

接着,列写输入方程,即要确定每一个J端和K端的连接方式;接着,列写次态方程:把J和K的值代入,它们都是反转的功能,每个反转功能分别是在CP1、Y1、Y2的下降沿实现;接着是状态转换表,其体现出的信息是:现态(时序电路当前时刻的状态)是什么;在输入信号的作用下,次态是什么。

eg:

假设触发器的当前状态为全0状态。

首先要给CP1这个外接时钟源提供一个下降沿,当下降沿到来时,Y1可以做状态的反转,即从0变为1,这是一个上升沿,但是对于Y2来讲,它需要的是Y1的下降沿才可以做状态的转变,所以第二个触发器保持,第三个触发器也是保持。所以000的次态是001, 001又变成新的现态,如果需要状态转变仍然需要提供CP1时钟的下降沿,CP1下降沿到来后,Y1从1变为0,是下降沿,第二个触发器有了它需要的时钟下降沿,可以实现状态反转(即由0变为1),以此类推。

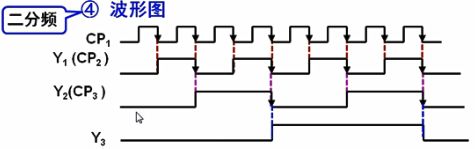

JK触发器的J、K端接高电平1,相当于是一个T’ 触发器,T’ 触发器具有二分频功能。

Y1是第一个T’ 触发器的输出,它对自己的时钟CP1是二分频功能,二分频功能的实现是在CP1的每一个下降沿。

以此类推。得到波形图,和状态表一样。

异步计数器总结:

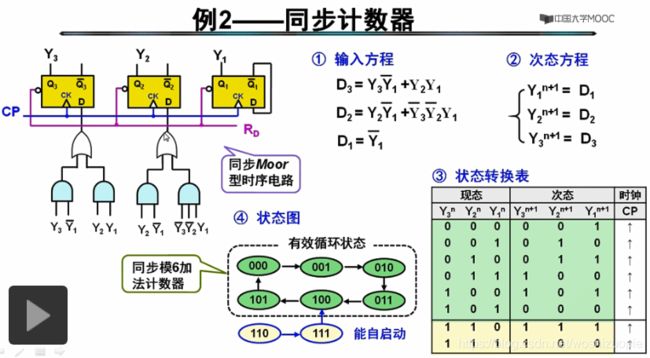

同步计数器

所有的时钟端连在一起;电路以触发器的Q输出作为整个电路的输出;第一个触发器的D输入端来源于Q1非的反馈,第二、三个触发器的D输入端来源于与门和或门组成的组合逻辑。

对于同步计数器,它们的时钟端连在一起,所以所有的触发器同时进行动作。

eg:

触发器当前的所有现态是0,把它代入输入方程,再代入次态方程,计算得出次态。次态的实现需要时钟的上升沿来。

从状态图中可以看出,这个时序电路可以自启动(即不需要人为干涉,可以从任意初始状态开始,经过任意时钟边沿后,一定能够进入到有效循环状态下)。

同步计数器总结:

时序逻辑电路的分析方法:

确定系统变量(输入变量、输出变量、状态变量)

①列驱动方程(控制函数)

②列输出方程(输出函数)

③列状态方程(次态方程)

④列写状态转换表

⑤画出状态图

⑥画出波形图(如必要)

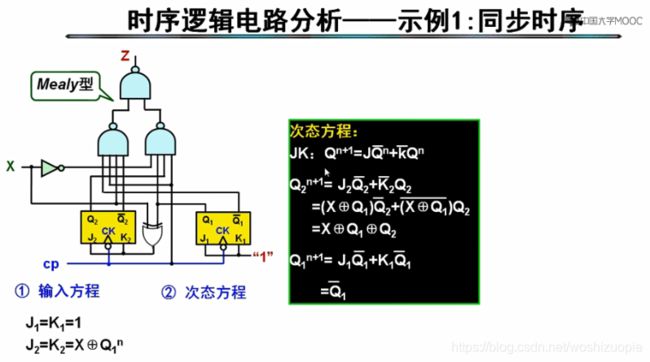

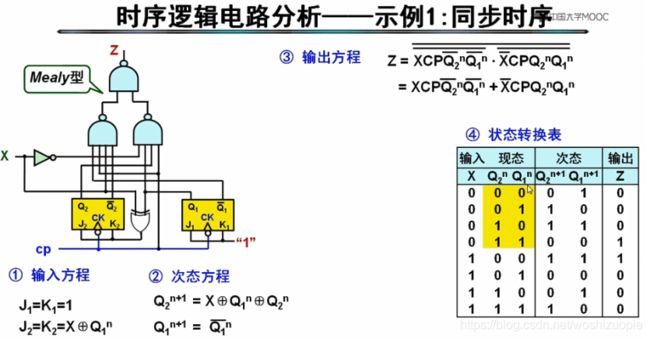

eg:同步时序,X为外接输入,Z为输出;输出不仅与输入、时钟有关,还与触发器的状态有关,所以是一个Mealy型的电路。

首先确定输入方程,J1和K1都是连接高电平1,J2和K2是一个异或门的输入;

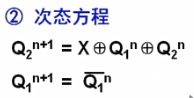

然后确定次态方程,把J1K1J2K2分别代入到JK触发器的次态方程中,得到:

然后确定输出方程,再推出状态转换表:X作为外界取值,有“0”和“1”两种;两个触发器有四种输入组合,所以总共有8种取值情况。

利用触发器设计同步时序逻辑

暂到此处,后边还有设计同步时序的例程等,用到再学。