[转帖]DDR3的学习

invoke调用,scheme机制,

1250ps--800MHZ, 1875ps--533.33MHZ

作者非常的幽默,关于DDR3共有下面几篇介绍。

来源:http://blog.chinaaet.com/detail/35142Xilinx/Avnet Spartan-6 LX16开发平台研究之路之屡败屡战

——By CrazyBingo,——20140228此作者也很幽默。

SPARTAN 6的MCB最快能跑到400MHz. 如果跟DDR3一起用的話, 能達到800MB/s的帶宽.

来源:spartan6_MCB使用详解,努力设置一个DDR3,希望可以在Spartan6平台上跑起来。加油!

xilinx平台DDR3设计教程之仿真篇_中文版教程,来源如下:

http://wenku.baidu.com/view/ac32c8bcf705cc1754270923.html

xilinx平台DDR3设计教程之综合篇_中文版教程,来源如下:

http://wenku.baidu.com/view/2ffa1334783e0912a3162a26.html?from_page=view&from_mod=download

xilinx平台DDR3设计教程之设计篇_中文版教程3,来源如下:

http://wenku.baidu.com/view/e42b2ac8f90f76c660371a3c.html

xilinx平台DDR3设计教程之高富帅篇_中文版教程,来源如下:

DDR3时序分析与设计,来源如下:

DDR3 SRAM存储器目标速率已达到1600Mbps,大大提高了传输带宽和传输效率。颗粒指bank,内存bank之间DQS与clk信号的时延偏差。

片上端接电阻ODT

基于FPGA的DDR3SDRAM控制器设计及实现,来源如下:

===================================================================

来源:http://wenku.baidu.com/view/e42b2ac8f90f76c660371a3c.html

地址的算法,记得每个地址可以存64bit数据,若按字节运算还要除以8。

2^(rank+bank+row+column)。其中rank是DIMM的排列方式,可以单面排列也可以双面排列。

来源:http://blog.163.com/fpga_ip/blog/static/20444302420129161139165/

造成随机存取效率较低的原因主要有:1.同Bank行切换;2.同时打开的Bank数只能是4个;3.读写切换。

八.解决办法

1.将Xilinx的DDR3控制器的同时能打开的bank数改为8;

2.调整DDR3访问(读或写)的顺序,避免同Bank行切换以及读写切换。

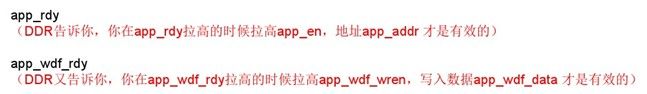

是的,当app_wdf_rdy为高时表示能够写入数据,反压信号的意思是当后面的逻辑处理不过来写入的数据时,通过一个信号告诉前面的逻辑,这个反压信号为1时,表示后面逻辑已经busy了,前面逻辑就要停止发送读写命令了。

DIMM全称是Dual-Inline-Memory-Modules,即双列直插式存储模块。这是在奔腾CPU推出后出现的新型内存条,DIMM提供了64位的数据通道。就是通常所说的内存条。

如果用的是Xilinx的FPGA与DIMM对接,他们的MIG生成的DDR控制器中同时只能打开4个bank。如果需要打开第五个bank,控制器就会把前4个先关掉,这个过程也是比较浪费DIMM带宽的。而DDR控制器同时打开的bank数是可以通过参数修改的,建议通过改参数将同时打开bank数调整为8。

来源:http://bbs.eetop.cn/thread-378689-1-1.html

ISE14.x的MIG做DDR3控制器的讨论:

我记得ise的ip向导生成ddr3的ip核时,会让你选地址bank,数据bank,时钟bank,你先看看画原理图的人把地址引脚、数据引脚、时钟引脚分别给你放在了哪个bank里,生成的时候直接改进去。

你是手动 gvim example.ucf文件,并自己手动填写的吧;DDR3的引脚是有专用的高速逻辑区域的,你要在

生成过程中添加约束的时候,选择下面的那个选项;然后自己填写相应引脚名称就可以了。这样你会发现和你自己手动打开再去写,文件内容是不一样的。

指定了DDR3的 BANK 就固定了DDR3的相关引脚。 PCB要连对了才行。

来源:http://www.altera.com.cn/support/kdb/solutions/rd01112011_972.html

http://www.doc88.com/p-91390067599.html 采用外部存储器解决方案提高系统性能。

http://wenku.baidu.com/view/d5e126f69e31433239689395.html终极内存技术指南

http://wenku.baidu.com/view/acfdfed733d4b14e8524687f.html高手进阶,终极内存技术指南——完整 写得非常好。

Physical layer interface (PHY)物理层接口,AFI = Altera PHY interface,intellectual property (IP)[专利] 知识产权。

Bandwidth and speed 带宽和速度,Cost成本,Data storage size and capacity数据存储大小和容量,Latency延迟,Power consumption功耗。

DRAM动态随机存取存储器(Dynamic Random Access Memory)是一种低带宽和低速度,低成本,高数据存储大小和高容量,高延迟,高功耗的存储器。

SRAM静态随机存储器(Static Random Access Memory)是一种高带宽和高速度,高成本,低数据存储大小和低容量,低延迟,低功耗的存储器。是一种常用的存储器,因为速度比容量更重要。

SDRAM同步动态随机存储器Synchronous Dynamic Random Access Memory。同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。

DDR3 SDRAM中DQS, DQSn, and DQ ports是双向的。读写操作共享地址端口。1.5V电压,深度从512MB到8GB,内部8块,允许块交叉访问,预取值是8,速度从300到1066MHZ。

ODT终端电阻,DQ DQS DQSn DM信号线。CAS latency, Burst length触发长度,Posted CAS:前置CAS

物理Bank 也叫行(Rank),物理块(P-Bank)定义:内存总线的数据位宽与CPU数据总线的位宽相等,因此P-Bank的位宽是固定的。

芯片组是由物理块组成的,其中物理块=芯片位宽*芯片数量。

物理块(P-Bank)-->逻辑块L-Bank(存储阵列)类似表格-->存储单元Word(用行、列进行寻址) 类似单元格。位宽的变化会引起存储单元的变化。

若内存芯片的容量为128Mbit(M*W,其中M为芯片中存储单元总数,W为存储单元的容量即芯片的位宽),当DIMM采用2个P-Bank+16bit芯片设计,则只能容纳8颗芯片。此时,DIMM的容量是8*128Mbit=128MB。如果DIMM用2个P-Bank+4bit,则只能容纳32颗芯片。此时,DIMM的容量是32*128Mbit=512MB。(1个P-Bank的固定位宽为64bit,则2个P-Bank的固定位宽为128bit。当芯片位宽为16bit时,芯片数量为8颗,当芯片位宽为4bit时,芯片数量为32颗),因此在芯片容量相同时,DIMM的容量肯定比不上采用低位宽芯片的模组,因为后者在一个P-Bank中可以容纳更多的芯片。

SDRAM 的引脚包含电源和时钟引脚。针对2个P-Bank要有1个片选信号,确定物理块。针对SDRAM最多有4个L-Bank,因此要有2个地址信号用于L-Bank寻址,确定芯片。行/列寻址确定存储单元,在相同容量下,行数不变,只有列数会根据位宽的而变化,位宽越大,列数越少,因为所需的存储单元减少了。相同位宽数据总线引脚。

128Mbit = 2M*4Banks*16bit。(8M*16)

128Mbit = 4M*4Banks*8bit。(16M*8)

128Mbit = 8M*4Banks*4bit。(32M*4)

The 1Gb chip is organized as 16Mbit x 8 I/Os x 8 banks or 8Mbit x 16 I/Os x 8 bank devices

- DDR3 SDRAM x32

- Micron MT41J64M16LA-15E DDR3 SDRAM 8MX16X8 两片DDR3就是32位 256MB

- Two devices: 2 x16 width = x32

- BTS DDR3 SDRAM GUI using Uniphy and high performance (HP) controller II

其中n取0,1,2,...

SDRAM 的内部基本操作与工作时序

1、芯片初始化:模式寄存器(MR,Mode Register)的设置,简称MRS(MR Set)(操作模式,CAS潜伏期CL,BT突发传输方式,突发长度BL)第10/68页。

2、行有效(L-Bank 有效):在CS#、L-Bank 定址的同时,RAS(Row Address Strobe,行地址选通脉冲)也处于有效状态。此时An 地址线则发送具体的行地址。第11/68页。

3、列读写:WE#无效时是读取命令 ,有效时是写入命令。列寻址信号与读写命令是同时发出的。

时钟频率、tRCD、数据传输频率、CL间的关系是倍数。

4、 数据输出(读)

tRCD是行选通周期即RAS to CAS Delay(RAS 至CAS 延迟)。

CAS 潜伏期(CAS Latency)即CL:从CAS 与读取命令发出到第一笔数据输出的一段时间。只在读取时出现,也叫RL读取潜伏期。CL 的单位与tRCD 一样,为时钟周

期数,具体耗时由时钟频率决定。

tAC(AccessTime from CLK,时钟触发后的访问时间)。tAC 的单位是ns,对于不同的频率各有不同的明确规定,但必须要小于一个时钟周期,否则会因访问时过长而使效

率降低。

5、数据输入(写):数据写入的操作也是在tRCD 之后进行,但此时没有了CL(记住,CL 只出现在读取操作中)。

写入/校正时间(tWR,Write Recovery Time),也称为写回(Write Back)。tWR 至少占用一个时钟周期或再多一点(时钟频率越高,tWR 占用周期越多)。

6、突发长BL

突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(Burst Lengths,简称BL)。

只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。这样,除了第一笔数据的传输需要若干个周

期(主要是之前的延迟,一般的是tRCD+CL)外,其后每个数据只需一个周期即可获得。

4QWORD是指BL=4,QWORD=64bit。P-Bank-->L-Bank-->Row

突发读/突发写,表示读与写操作都是突发传输的,每次读/写操作持续BL 所设定的长度,这也是常规的设定。

突发读/单一写,表示读操作是突发传输,写操作则只是一个个单独进行。

突发传输模式代表着突发周期内所涉及到的存储单元的传输顺序。

顺序传输是指从起始单元开始顺序读取。假如BL=4,起始单元编号是n,顺序就是n、n+1、n+2、n+3。

交错传输就是打乱正常的顺序进行数据传输(比如第一个进行传输的单元是n,而第二个进行传输的单元是n+2 而不是n+1)。

7、预充电

由于SDRAM 的寻址具有独占性,所以在进行完读写操作后,如果要对同一L-Bank 的另一行进行寻址,就要将原来有效(工作)的行关闭,重新发送行/列

地址。L-Bank 关闭现有工作行,准备打开新行的操作就是预充电(Precharge)。

在发出预充电命令之后,要经过一段时间才能允许发送RAS 行有效命令打开新的工作行,这个间隔被称为tRP(Precharge command Period,预充电有效周期)。和tRCD、CL 一样,tRP 的单位也是时钟周期数,具体值视时钟频率而定。

以内存最主要的操作——读取为例。tRCD 决定了行寻址(有效)至列寻址(读/写命令)之间的间隔,CL 决定了列寻址到数据进行真正被读取所花费的时间,tRP 则决定了相同L-Bank 中不同工作行转换的速度。

在单独的预充电命令中,A10 则控制着是对指定的L-Bank 还是所有的L-Bank(当有多个L-Bank 处于有效/活动状态时)进行预充电,前者需要提供L-Bank 的地址,后者只需将A10 信号置于高电平。

预充电可以通过命令控制,也可以通过辅助设定让芯片在每次读写操作之后自动进行预充电。

8、刷新:SDRAM需不断地进行刷新(Refresh)才能保留住数据。

刷新操作与预充电中重写的操作一样,都是用S-AMP 先读再写。由于预充电是对一个或所有L-Bank 中的工作行操作,并且是不定期的,而刷新则是有固定的周期,依次对所有行进行操作,以保留那些久久没经历重写的存储体中的数据。但与所有L-Bank 预充电不同的是,这里的行是指所有L-Bank 中地址相同的行,而预充电中各L-Bank 中的工作行地址并不是一定是相同的。

刷新操作分为两种:自动刷新(Auto Refresh,简称AR)与自刷新(SelfRefresh,简称SR)。由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者说CAS 在RAS 之前有效。所以,AR 又称CBR(CAS Before RAS,列提前于行定位)式刷新。SR 则主要用于休眠模式低功耗状态下的数据保存。在SR 期间除了CKE 之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使CKE 有效才能退出自刷新模式并进入正常操作状态。

9、数据掩码

在讲述读/写操作时,我们谈到了突发长度。如果BL=4,那么也就是说一次就传送4×64bit 的数据。但是,如果其中的第二笔数据是不需要的,怎么办?还都传输吗?为了屏蔽不需要的数据,人们采用了数据掩码(Data I/O Mask,简称DQM)技术。通过DQM,内存可以控制I/O 端口取消哪些输出或输入的数据。这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

SDRAM 官方规定,在读取时DQM 发出两个时钟周期后生效,而在写入时,DQM与写入命令一样是立即成效。

DDR SDRAM双倍数据流SDRAM(Double Data Rate SDRAM)

DLL=Delayed Locked Loop(延迟锁定环路)。DQS= DQ Strobe(数据选取脉冲)。

SDRAM 中L-Bank 存储单元的容量与芯片位宽相同,而DDR SDRAM 中L-Bank 存储单元的容量是芯片位宽的一倍。即芯片内部总线位宽=2*芯片I/O总线位宽,也叫2位预取(2-bit Prefetch)。

DDR SDRAM 在MRS 之前还多了一EMRS 阶段(Extended Mode Register Set,扩展模式寄存器设置),这个扩展模式寄存器控制着DLL 的有效/禁止、输出驱动强度、QFC 有效/无效等。

1、 差分时钟:它是DDR 的一个必要设计,起到触发时钟校准的作用,用CK#去校准CK。

2、 数据选取脉冲(DQS):它是DDR SDRAM 中的重要功能,它的功能主要用来在一个时钟周期内准确的区分出每个传输周期,并便于接收方准确接收数据。

DQS是双向的,在写入时它用来传送由北桥发来的DQS 信号,读取时,则由芯片生成DQS 向北桥发送。完全可以说,它就是数据的同步信号。在读取时,DQS 与数据信号同时生成。在写入时,芯片不再自己生成DQS,而以发送方传来的DQS 为基准,并相应延后一定的时间,在DQS 的中部为数据周期的选取分割点(在读取时分割点就是上下沿),从这里分隔开两个传输周期。这样做的好处是,由于各数据信号都会有一个逻辑电平保持周期,即使发送时不同步,在DQS 上下沿时都处于保持周期中,此时数据接收触发的准确性

无疑是最高的。

3、 写入延迟

在上面的DQS 写入时序图中,可以发现写入延迟已经不是0 了,在发出写入命令后,DQS 与写入数据要等一段时间才会送达。这个周期被称为DQS 相对于写入命令的延迟时间(tDQSS, WRITE Command to the first corresponding rising edge of DQS)。

当CL=2.5 时,读后写的延迟将为tDQSS+0.5 个时钟周期(图中BL=2)

4、突发长度与写入掩码

在DDR SDRAM 中,突发长度只有2、4、8 三种选择,没有了随机存取的操作(突发长度为1)和全页式突发。

5、 延迟锁定回路(DLL):它的作用是使内部时钟与外部时钟保持同步。有两种方法:时钟频率测量法(CFM)和时钟比较法(CC)

DLL 不同于主板上的PLL,它不涉及频率与电压转换,而是生成一个延迟量给内部时钟。

第51/68页介绍:

第64/68页介绍:

![[转帖]DDR3的学习_第1张图片](http://img.e-com-net.com/image/product/f226198784f84c3ab7fd3745a0a6de0c.jpg)

![[转帖]DDR3的学习_第2张图片](http://img.e-com-net.com/image/product/55be1976af9b490da6437fcc357fdb31.jpg)

![[转帖]DDR3的学习_第3张图片](http://img.e-com-net.com/image/product/f8033f016ccb4dc6a1eef31a96d0c0ff.jpg)

![[转帖]DDR3的学习_第4张图片](http://img.e-com-net.com/image/product/a2969142300c4a05ac0f58961f301a2e.jpg)

![[转帖]DDR3的学习_第5张图片](http://img.e-com-net.com/image/product/d12f75c65b5a48b793ab44961dff4cb2.jpg)

![[转帖]DDR3的学习_第6张图片](http://img.e-com-net.com/image/product/4d226517cca94b22ae4620f70a3eff6f.jpg)

![[转帖]DDR3的学习_第7张图片](http://img.e-com-net.com/image/product/6f3ee89cebe943d4bdf7bf0b01262310.jpg)

![[转帖]DDR3的学习_第8张图片](http://img.e-com-net.com/image/product/ac3563904b90486e87b448d85627efe2.jpg)

![[转帖]DDR3的学习_第9张图片](http://img.e-com-net.com/image/product/150b0c4d5ee7442b9d8c7be834adc612.jpg)