FPGA 交通灯

设计要求

实现开发板上东西南北 4 个方向,每个方向上的 3 个 LED 灯按照“绿灯--黄灯--红灯--绿灯- -黄灯......”依次循环变化。变化的速度不同,东面的间隔时间为 1 秒;西面的间隔时间为 2 秒;南 面的间隔时间为 3 秒;北面的间隔时间为 4 秒。 具体要求: 1、每个方向的灯分开独立设计。 2、首先设计东向的灯:设计一个计时 1 秒的计数器,用来计算灯的状态变化的时间间隔。 3、如果计时 1 秒到了,把黄灯点亮;再过 1 秒把红灯点亮;再过 1 秒,把绿灯点亮...... 依次循环。 4、设计西方向的灯:设计一个计时 2 秒的计数器,其他的类似。

2

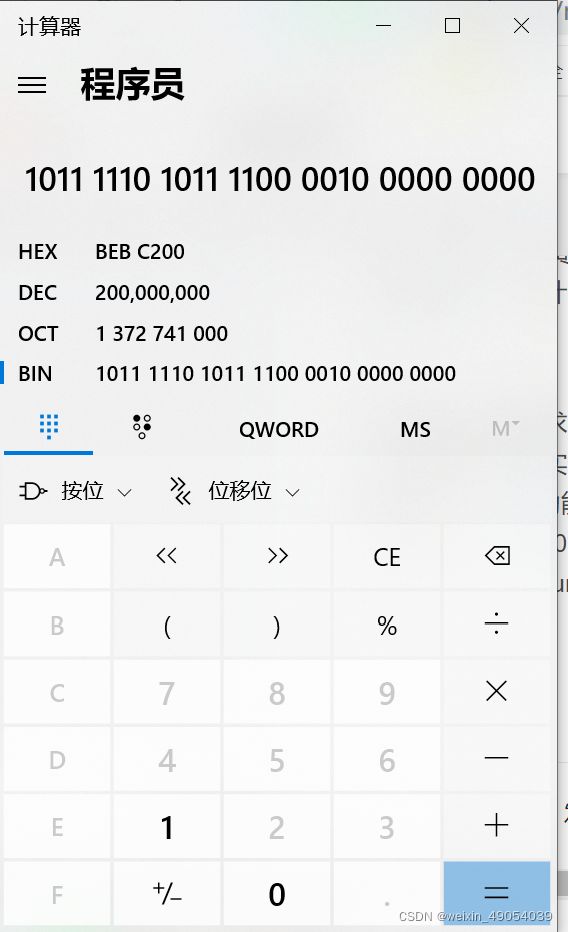

根据题目功能要求,东西南北四个方向 LED 灯颜色变换的速度都不同。因为在数字电路中的延 时都是通过计数器实现的,计数器*时钟周期=延时时间。本模块中,由于输入时钟是 50MHz,时钟周 期为 20ns,功能要求每 1 秒变化一次。我们通过 counter 来表示延时,当其值为 1s/20ns=5000_00 00 时,表示 1 秒时间到。 本工程架构由四个计数器组成:e_counter w_counter n_counter s_counter。

可以看到 50000000*4 位宽为28位 所以所有计数器位宽都为[27:0].

parameter COUNT_1S = 26'd5000_0000;

always @(posedge clk or negedge rst_n) begin

if (rst_n==0) begin

e_counter <= 0;

end

else if(add_e_counter) begin

if(end_e_counter)

e_counter <= 0;

else e_counter <= e_counter+1 ;

end

end

assign add_e_counter = 1;

assign end_e_counter = add_e_counter && e_counter == COUNT_1S-1 ;

LED 灯信号的变化,根据功能要求,东面的间隔时间为 1 秒;西面的间隔时间为 2 秒;南面 2 的间隔时间为 3 秒;北面的间隔时间为 4 秒。计数时间到时变化;时间没到,则不变化。每一时 刻每个方向只有一个灯亮,并且亮灯的颜色顺序按照“绿灯--黄灯--红灯--绿灯--黄灯.....”依次循环变 化。 东西南北四个方向的各有三盏不同颜色的 LED 灯,每个方向的三个 LED 灯都由 3 比特信号控 制,最高位为红灯,最低位为绿灯,并且低电平时 LED 灯亮。led_east 表示东面三个 LED 灯,led_ west 表示西面三个 LED 灯,led_south 表示南面三个 LED 灯,led_north 表示北面三个 LED 灯。 三色 LED 灯的循环变换控制可以通过拼接的方法使数据循环左移来实现。

接下来就是灯的控制信号 这里采用移位拼接的方法;led_east<={{(LED_LEN-1){1'b1}},1'b0};

led_east<={{(LED_LEN-1){1'b1}},1'b0};

代码如下:采用一个时序逻辑来控制。

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

led_east<={{(LED_LEN-1){1'b1}},1'b0};

end

else if(end_e_counter)begin

led_east<={led_east[LED_LEN-2:0],led_east[LED_LEN-1]};

end

else begin

led_east<=led_east;

end

end

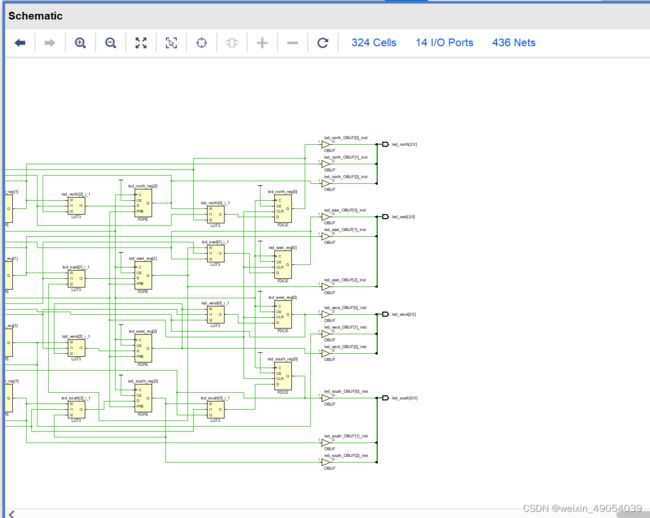

最后输出端口output如下

总体代码如下

module jiaotongden

(

input wire clk,

input wire rst_n,

output reg [2:0] led_east,

output reg [2:0] led_south,

output reg [2:0] led_west,

output reg [2:0] led_north

);

reg [27:0] e_counter;

reg [27:0] w_counter;

reg [27:0] n_counter;

reg [27:0] s_counter;

parameter COUNT_1S = 26'd5000_0000;

parameter LED_LEN = 3;

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

e_counter<= 0;

end

else if(add_e_counter)begin

if(end_e_counter)

e_counter <= 0;

else

e_counter <=e_counter + 1;

end

end

assign add_e_counter = 1;

assign end_e_counter = add_e_counter && e_counter==COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin

if (rst_n==0) begin

w_counter <= 0;

end

else if(add_w_counter) begin

if(end_w_counter)

w_counter <= 0;

else

w_counter <= w_counter+1 ;

end

end

assign add_w_counter = 1;

assign end_w_counter = add_w_counter && w_counter == 2*COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin

if (rst_n==0) begin

s_counter <= 0;

end

else if(add_s_counter) begin

if(end_s_counter)

s_counter <= 0;

else

s_counter <= s_counter+1 ;

end

end

assign add_s_counter = 1;

assign end_s_counter = add_s_counter && s_counter == 3*COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin

if (rst_n==0) begin

n_counter <= 0;

end

else if(add_n_counter) begin

if(end_n_counter)

n_counter <= 0;

else

n_counter <= n_counter+1 ;

end

end

assign add_n_counter = 1;

assign end_n_counter = add_n_counter && n_counter == 4*COUNT_1S-1 ;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

led_east<={{(LED_LEN-1){1'b1}},1'b0};

end

else if(end_e_counter)begin

led_east<={led_east[LED_LEN-2:0],led_east[LED_LEN-1]};

end

else begin

led_east<=led_east;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

led_west<={{(LED_LEN-1){1'b1}},1'b0};

end

else if(end_w_counter)begin

led_west<={led_west[LED_LEN-2:0],led_west[LED_LEN-1]};

end

else begin

led_west<=led_west;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

led_south<={{(LED_LEN-1){1'b1}},1'b0};

end

else if(end_s_counter)begin

led_south<={led_south[LED_LEN-2:0],led_south[LED_LEN-1]};

end

else begin

led_south<=led_south;

end

end

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

led_north<={{(LED_LEN-1){1'b1}},1'b0};

end

else if(end_n_counter)begin

led_north<={led_north[LED_LEN-2:0],led_north[LED_LEN-1]};

end

else begin

led_north<=led_north;

end

end

endmodule