AD9834的使用

注:以下内容来自官方datasheet。

产品特性

窄带SFDR > 72 dB

2.3 V至5.5 V电源供电

输出频率高达37.5 MHz

正弦波输出/三角波输出

片上集成比较器

三线式SPI®接口

扩展温度范围: -40℃至+105℃

省电选项

功耗: 20 mW(3 V时)

20引脚TSSOP

应用

频率激励/波形发生

频率相位调谐和调制

低功耗RF/通信系统

液体和气流测量

传感器应用:接近度、运动和缺陷检测

测试与医疗设备

概述

AD9834是一款75 MHz、低功耗DDS器件,能够产生高性能正弦波和三角波输出。其片内还集成一个比较器,支持产生方波以用于时钟发生。当供电电压为3 V时,其功耗仅为20 mW,非常适合对功耗要求严格的应用。

AD9834提供相位调制和频率调制功能。频率寄存器为28位;时钟速率为75 MHz,可以实现0.28 Hz的分辨率。同样,时钟速率为1 MHz时, AD9834可以实现0.004 Hz的分辨率。影响频率和相位调制的方法是通过串行接口加载寄存器,然后通过软件或FSELECT/PSELECT引脚切换寄存器。

AD9834通过一个三线式串行接口写入数据。该串行接口能够以最高40 MHz的时钟速率工作,并且与DSP和微控制器标准兼容。

该器件采用2.3 V至5.5 V电源供电。模拟和数字部分彼此独立,可以采用不同的电源供电;例如, AVDD可以是5 V,而DVDD可以是3 V。

AD9834具有控制休眠的引脚(SLEEP),支持从外部控制断电模式。器件中不用的部分可以断电,以将功耗降至最低。例如,在产生时钟输出时,可以关断DAC。

该器件采用20引脚TSSOP封装。

引脚

| 引脚编号 | 引脚名称 | 描述 |

|---|---|---|

| 1 | FS ADJUST | 满量程调整控制。此引脚和AGND之间连接一个电阻(RSET),从而决定满量程DAC电流的幅度。 RSET与满量程电流之间的关系如下: IOUTFULL SCALE = 18 × FSADJUST/RSET FSADJUST = 1.15 V(标称值), RSET = 6.8 kΩ(典型值)。 |

| 2 | REFOUT | 基准电压输出。 AD9834通过此引脚提供1.20 V内部基准电压源。 |

| 3 | COMP | DAC偏置引脚。此引脚用于对DAC偏置电压进行去耦。 |

| 17 | VIN | 比较器输入。可利用比较器从正弦DAC输出产生方波。 DAC输出应经过适当滤波,然后再施加于比较器,以改善抖动性能。当控制寄存器中的Bit OPBITEN和Bit SIGN/PIB置1时,比较器输入端连接到VIN。 |

| 19, 20 | IOUT,IOUTB | 电流输出。这是高阻抗电流源。应在IOUT和AGND之间连接一个标称值为200 Ω的负载电阻。 IOUTB最好应通过一个大小为200 Ω的外部负载电阻连接到AGND,但也可直接与AGND相连。此外还建议通过一个20 pF电容连接到AGND,以防止出现时钟馈通。 |

电源:

| 引脚编号 | 引脚名称 | 描述 |

|---|---|---|

| 4 | AVDD | 模拟部分的正电源。 AVDD的值范围为2.3 V至5.5 V。应在AVDD和AGND之间连接一个0.1 μF去耦电容。 |

| 5 | DVDD | 数字部分的正电源。 DVDD的值范围为2.3 V至5.5 V。应在DVDD和DGND之间连接一个0.1 μF去耦电容。 |

| 6 | CAP/2.5V | 数字电路采用2.5 V电源供电。当DVDD超过2.7 V时,此2.5 V利用片内调节器从DVDD产生。该调节器需要在CAP/2.5 V至DGND之间连接一个典型值为100 nF的去耦电容。如果DVDD小于或等于2.7 V,则CAP/2.5 V应与DVDD直接相连。 |

| 7 | DGND | 数字地。 |

| 18 | AGND | 模拟地。 |

数字接口和控制

| 引脚编号 | 引脚名称 | 描述 |

|---|---|---|

| 8 | MCLK | 数字时钟输入。 DDS输出频率是MCLK频率的一个分数,分数的分子是二进制数。输出频率精度和相位噪声均由此时钟决定。 |

| 9 | FSELECT | 频率选择输入。 FSELECT控制相位累加器中使用的具体频率寄存器(FREQ0或FREQ1)。可使用引脚FSELECT或Bit FSEL来选择要使用的频率寄存器。使用Bit FSEL来选择频率寄存器时, FSELECT引脚应与CMOS高电平或低电平相连。 |

| 10 | PSELECT | 相位选择输入。 PSELECT控制将增加到相位累加器输出的具体相位寄存器(PHASE0或PHASE1)。可使用引脚PSELECT或Bit PSEL来选择要使用的相位寄存器。当相位寄存器由Bit PSEL控制时, PSELECT引脚应与CMOS高电平或低电平相连。 |

| 11 | RESET | 高电平有效数字输入。 RESET可使相应的内部寄存器复位至0,以提供中间电平的模拟输出。 RESET不影响任何可寻址寄存器。 |

| 12 | SLEEP | 高电平有效数字输入。当此引脚处于高电平时, DAC关断。此引脚功能与控制位SLEEP12相同。 |

| 13 | SDATA | 串行数据输入。 16位串行数据字施加于此输入。 |

| 14 | SCLK | 串行时钟输入。数据在每个SCLK下降沿逐个输入AD9834。 |

| 15 | FSYNC | 低电平有效控制输入。这是输入数据的帧同步信号。当FSYNC变为低电平时,即告知内部逻辑,正在向器件中载入新数据字。 |

| 16 | SIGN BIT OUT |

逻辑输出。比较器输出通过此引脚提供,或者可通过此引脚输出NCO的MSB。通过将控制寄存器中的Bit OPBITEN置1,可使能此输出引脚。 Bit SIGN/PIB确定通过该引脚输出的是比较器输出还是NCO的MSB。 |

工作原理

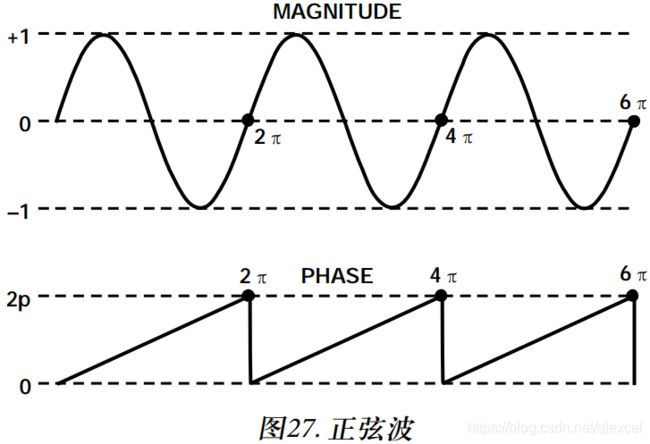

正弦波通常用其幅度来表示: a(t) = sin(ωt)。不过,这类正弦波是非线性曲线,因此除非通过分段构建,否则不易生成。另一方面,角度信息本质上是线性的。也就是说,每个单位时间内,相位角度会旋转固定角度。角速率取决于信号频率,也即ω = 2πf。

已知正弦波的相位是线性的,如果给定参考时间间隔(时钟周期),则可以确定该周期内的相位旋转情况。

∆Phase = ω∆t

求出ω,

ω = ∆Phase/∆t = 2πf

求出f并用参考时钟频率替换参考周期(1/fMCLK = Δt)

f = ∆Phase × fMCLK/2π

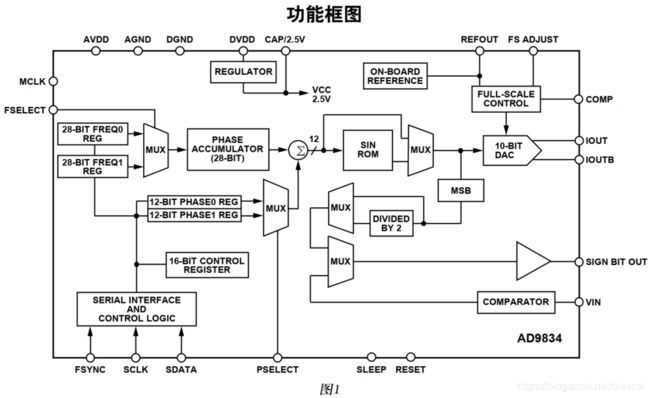

AD9834根据这个简单公式来构建输出。一个简单的DDS芯片便可利用以下三大主要子电路来实现此公式:数控振荡器和相位调制器、 SIN ROM以及数模转换器(DAC)。 “电路描述”部分将逐个介绍各个子电路。

电路描述

AD9834是一个完全集成的直接数字频率合成(DDS)芯片。该芯片需要一个参考时钟、一个精密低电阻和八个去耦电容,以用数字方式产生高达37.5 MHz的正弦波。除产生这个RF信号之外,该芯片还完全能支持各种简单和复杂的调制方案。这些调制方案完全在数字域内实现,使得可以使用DSP技术精确而轻松地实现复杂的调制算法。

AD9834的内部电路包含以下主要部分:数控振荡器(NCO)、频率和相位调制器、 SIN ROM、 DAC、比较器以及稳压器。

数控振荡器和相位调制器

该子电路由两个频率选择寄存器、一个相位累加器、两个相位偏移寄存器和一个相位偏移加法器组成。 NCO的主要元件是一个28位相位累加器。连续时间信号的相位范围为0 π至2 π。在此数值范围之外,正弦函数以周期方式不断重复。数字实现并无差别。累加器只是将相位数值范围扩大至多位数字字。 AD9834中的相位累加器利用28位来实现。因此,在AD9834中, 2π = 228。同样, ΔPhase项也会扩大至此数值范围:

0 < ∆Phase < 228 − 1

将这些带入前面的公式可得:

f = ∆Phase × fMCLK/228

其中, 0 < ∆Phase < 228 − 1.

相位累加器的输入可以从FREQ0寄存器或FREQ1寄存器进行选择并由FSELECT引脚或FSEL bit控制。 NCO本身会产生连续相位信号,因此在频率之间切换时应避免出现任何输出不连续。

在NCO之后,可以使用12位相位寄存器添加一个相位偏移来执行相位调制。这些相位寄存器之一的内容会增加到NCO的MSB。 AD9834具有两个相位寄存器,且这两个寄存器的分辨率均为2π/4096。

SIN ROM

要使用NCO的输出,必须先将其从相位信息转换成正弦数值。相位信息可以直接映射至幅度,因此SIN ROM可以将

数字相位信息用作查找表的地址并将相位信息转换成幅度。

虽然NCO包含28位相位累加器,但NCO的输出会被截断至12位。使用相位累加器的全分辨率不仅不切实际,也根本不必要,因为这要求查找表具有228个条目。只需具有足够的相位分辨率,使得因截断而产生的误差小于10位DAC的分辨率。这就要求SIN ROM的相位分辨率比10位DAC高出两位。

可使用控制寄存器中的OPBITEN和MODE bits来使能SIN ROM。此功能详见表18。

数模转换器(DAC)

AD9834包含一个高阻抗、电流源10位DAC,能够驱动各种负载。可使用一个外部电阻(RSET)来调节满量程输出电

流,以实现最佳电源和外部负载要求。

DAC可配置为单端工作模式或差分工作模式。 IOUT和IOUTB可通过大小相等的外部电阻连接到AGND,以产生互补的输出电压。只要负载电阻上产生的满量程电压不超过顺从电压范围,该电阻便可以是所需的任意值。由于满量程电流由RSET控制,因此通过调节RSET可以平衡对负载电阻做出的更改。

比较器

AD9834可用于产生合成频率数字时钟信号,其实现方式是利用片内自偏置比较器将DAC的正弦波信号转换成方波。 DAC的输出先在外部经过滤波,然后再施加于比较器输入端。比较器基准电压是施加于VIN的信号的时间平均值。比较器可以接受大约100 mV p-p至1 V p-p范围内的信号。由于比较器输入端交流耦合,因此要作为零交越检波器正常工作,输入频率最小值通常应为3 MHz。比较器输出为方波,幅度范围为0 V至DVDD。

AD9834的输出是根据奈奎斯特采样原理进行采样的信号。具体而言,其输出频谱包含基波和混叠信号(镜像),且镜像频率为参考时钟频率和所选输出频率的倍数。采样频谱(含混叠镜像)的图形表示如图28所示。

混叠镜像的突出程度取决于fOUT与MCLK的比值。如果该比值很小,混叠镜像将非常突出且能量水平相对较高,具体由量化DAC输出的sin(x)/x滚降决定。事实上,根据fOUT与参考时钟的关系,第一个混叠镜像约低于基波−3 dB。

DAC的输出端和比较器的输入端之间通常会放置一个低通滤波器,以进一步抑制混叠镜像效应。显然,必须考虑所选输出频率和参考时钟频率之间的关系,以免产生不良(和异常)的输出异常。要将AD9834用作时钟发生器,应将所选输出频率限制为小于参考时钟频率的33%,从而避免产生位于或接近目标输出频段(通常为直流选择输出频率)的混叠信号。此做法可以简化时钟发生器应用所需外部滤波器的复杂度(并降低相关成本)。更多详情参见“AN-837应用笔记”。

要使能比较器,控制器中的Bit SIGN/PIB和Bit OPBITEN应置1,具体参见表17。

稳压器

AD9834的模拟部分和数字部分各自具有单独的电源。AVDD提供模拟部分所需的电源, DVDD则提供数字部分所需的电源。这两个电源的值范围均为2.3 V至5.5 V,并且彼此独立。例如,模拟部分可采用5 V工作,数字部分则可采用3 V工作,反之亦然。

AD9834的内部数字部分采用2.5 V工作。片内稳压器会将施加于DVDD的电压下调至2.5 V。 AD9834的数字接口(串行端口)也采用DVDD供电。这些数字信号会在AD9834内部进行电平转换,以便与2.5 V兼容。

当器件DVDD引脚处施加的电压等于或小于2.7 V时,应将CAP/2.5V引脚和DVDD引脚相连,从而旁路片内稳压器。

输出顺从电压

AD9834的最大电流密度为4 mA,由RSET设置。 AD9834的最大输出电压为VDD − 1.5 V。这是为了确保内部开关的输出阻抗不会发生变化,从而不会影响器件的频谱性能。对于2.3 V的最小电源电压,最大输出电压为0.8 V。当RSET为6.8 kΩ且RLOAD为200 Ω时,保证达到表1中的额定性能。

功能描述

串行接口

AD9834具有一个标准三线式串行接口,并且与SPI、QSPI™、 MICROWIRE™、 DSP接口标准兼容。

数据在串行时钟输入(SCLK)的控制下作为16位字载入器件。图5给出了这种操作的时序图。

欲了解对AD9833和AD9834器件进行编程的详细示例,请参阅“AN-1070应用笔记”。

FSYNC输入是电平触发输入,用作帧同步和芯片使能。仅当FSYNC处于低电平时,才可将数据传输至器件。要开始串行数据传输,应将FSYNC拉低,并注意FSYNC至SCLK下降沿建立时间(t7)的最小值。 FSYNC变为低电平后,串行数据即会在16个时钟脉冲的SCLK下降沿移入器件的输入移位寄存器。可在SCLK的第16个下降沿后将FSYNC拉高,并注意SCLK下降沿至FSYNC上升沿时间(t8)的最小值。或者, FSYNC可以在16倍数个SCLK脉冲期间保持低电平,然后在数据传输结束时变为高电平。这样,在FSYNC保持低电平期间,可以连续流形式载入16位字;FSYNC仅在载入最后一个字的第16个SCLK下降沿之后变为高电平。

SCLK可以是连续的,也可以在写操作期间置于高电平或低电平空闲状态,但当FSYNC变为低电平(t12)时必须处于

高电平状态。

AD9834上电

图31中的流程图显示AD9834的运行程序。 AD9834上电时,器件应复位。这样可使相应的内部寄存器复位至0,以提供中间电平的模拟输出。为了避免AD9834初始化时产生杂散DAC输出, RESET bit/引脚应置1,直至器件准备好开始产生输出。 RESET不会使相位、频率或控制寄存器复位。这些寄存器包含无效数据,因此应由用户将其设为已知值。然后, RESET bit/引脚应置0,以开始产生输出。在RESET置0后的8个MCLK周期内, DAC输出端会出现数据。

延迟

每个操作均会造成延迟。当引脚FSELECT和引脚PSELECT更改数值时,向所选寄存器传输控制信息之前会存在流水线延迟。满足t11和t11A时序规格(见图4)时, FSELECT和PSELECT具有8个MCLK周期的延迟。不满足t11和t11A时序规格时,延迟会增加一个MCLK周期。

同样,每个异步写操作也会造成延迟。如果所选频率或相位寄存器中载入新数据字,那么模拟输出改变之前会存在8到9个MCLK周期的延迟。还有一个MCLK周期不确定,因为这取决于向目标寄存器载入数据时MCLK上升沿所在的位置。

RESET和SLEEP功能的负向转换在MCLK的内部下降沿处采样。因此,也会造成延迟。

控制寄存器

AD9834包含一个16位控制寄存器,用户可利用该寄存器来设置AD9834的工作模式。除MODE以外的所有控制位均在MCLK的内部负边沿上采样。表6介绍了控制寄存器的各个位。有关AD9834中不同功能和各种输出选项的详细说明,请参见“频率和相位寄存器”部分。

要告知AD9834控制寄存器的内容将改变, DB15和DB14必须置0,如表5所示。

待续。。