Verilog实现---AHB_APB通讯架构

目录

- 1.实现目标

- 2.文件说明

- 3.工作流程与原理

- 4.端口说明

- 5.测试流程

- 6.代码及文件获取

1.实现目标

利用Verilog实现如下图的系统功能并完成仿真

如上图,主设备Master0利用AHB-Lite总线协议通过APB Bridge访问四个APB从设备Slave0、Slave、Slave2和Slave3.

每个从设备的地址空间如下:

Slave0: 0x0000_0000 ~ 0x0000_00ff;

Slave1: 0x0000_0100 ~ 0x0000_01ff;

Slave2: 0x0000_0200 ~ 0x0000_02ff;

Slave3: 0x0000_0300 ~ 0x0000_03ff;

令从设备地址空间的下边界为其地址的基址,假设每个从设备中有可访问APB寄存器16个,位宽均为32比特,16个寄存器的访问地址计算方式为 基址 + 寄存器编号左移2位(byte 偏移)

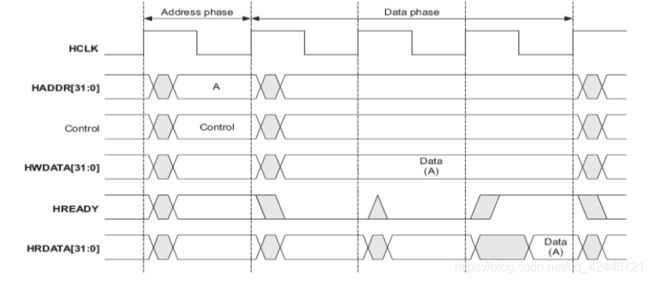

主设备接口的数据读写采用AHB-Lite总线协议,并遵循如下时序规范:

从设备读写遵循APB时序规范:

APB桥的作用是将主设备的访问信号转化成APB总线信号访问从设备,假定PCLK是HCLK的2分频时钟。

要求:

1.利用verilog代码完成蓝色部分系统搭建;

2.搭建testbench进行仿真验证,主设备可以同时正确的对任意一个从设备寄存器进行读写。

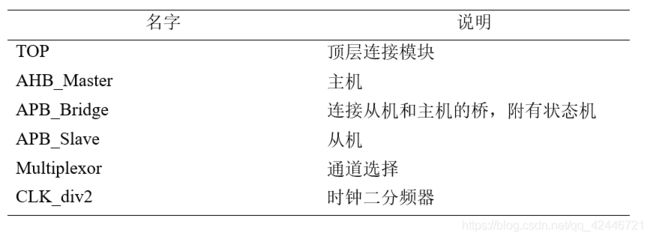

2.文件说明

3.工作流程与原理

参考文章: https://blog.csdn.net/qq_36829655/article/details/110360148

4.端口说明

5.测试流程

一、 复位

二、 写第二个从机5号寄存器

三、 读第二步写的数据

6.代码及文件获取

由于代码过多,这里仅展示TOP文件的代码,其他完整代码附在文章最后,有需要的可以参考

//**

//Author: Luk.wj

//Create: 2020.12.14

//Revise: 2020.12.15

//Fuction: 顶层连接文件

//**

module TOP(HCLK,Tstart,Twrite,Taddr,Twdata,Rst,Trdata);

input HCLK;

input Tstart;

input Twrite;

input[31:0] Taddr;

input[31:0] Twdata;

input Rst;

output[31:0] Trdata;

/* AHB_Master */

wire Hready;

wire[31:0] Hrdata;

/* APB_Bridge */

wire[31:0] Haddr;

wire[31:0] Hwdata;

wire Hwrite;

wire Hen;

wire[31:0] Prdata_m;

/* APB_Slave */

wire[31:0] Paddr;

wire PSEL0,PSEL1,PSEL2,PSEL3;

wire Pen;

wire Pwrite;

wire[31:0] Pwdata;

wire PCLK;

/* Multiplexor */

wire[31:0] Hrdata_0,Hrdata_1,Hrdata_2,Hrdata_3;

/* Define Relationship */

AHB_Master Master(

//Test

.Twrite (Twrite),

.Taddr (Taddr),

.Twdata (Twdata),

.Tstart (Tstart),

.Trdata (Trdata),

//Input

.Hrdata (Hrdata),

.HCLK (HCLK),

.Hrst (Rst),

.Hready (Hready),

//Output

.Haddr (Haddr),

.Hwdata (Hwdata),

.Hwrite (Hwrite),

.Hen (Hen)

);

CLK_div2 div2(

.HCLK (HCLK),

.PCLK (PCLK)

);

APB_Bridge Bridge(

//Input

.Haddr (Haddr),

.Hwdata (Hwdata),

.Hwrite (Hwrite),

.Hen (Hen),

.Prdata_m (Prdata_m),

.PCLK (PCLK),

.Prst (Rst),

//Output

.Paddr (Paddr),

.PSEL0 (PSEL0),

.PSEL1 (PSEL1),

.PSEL2 (PSEL2),

.PSEL3 (PSEL3),

.Pen (Pen),

.Pwrite (Pwrite),

.Pwdata (Pwdata) ,

.Hready (Hready),

.Hrdata (Hrdata)

);

APB_Slave Slave0(

//Input

.Paddr (Paddr),

.PSELx (PSEL0),

.Pen (Pen),

.Pwrite (Pwrite),

.Pwdata (Pwdata) ,

.Prst (Rst),

.PCLK (PCLK),

//Output

.Prdata (Hrdata_0)

);

APB_Slave Slave1(

//Input

.Paddr (Paddr),

.PSELx (PSEL1),

.Pen (Pen),

.Pwrite (Pwrite),

.Pwdata (Pwdata) ,

.Prst (Rst),

.PCLK (PCLK),

//Output

.Prdata (Hrdata_1)

);

APB_Slave Slave2(

//Input

.Paddr (Paddr),

.PSELx (PSEL2),

.Pen (Pen),

.Pwrite (Pwrite),

.Pwdata (Pwdata) ,

.Prst (Rst),

.PCLK (PCLK),

//Output

.Prdata (Hrdata_2)

);

APB_Slave Slave3(

//Input

.Paddr (Paddr),

.PSELx (PSEL0),

.Pen (Pen),

.Pwrite (Pwrite),

.Pwdata (Pwdata) ,

.Prst (Rst),

.PCLK (PCLK),

//Output

.Prdata (Hrdata_3)

);

Multiplexor Mul(

//Input

.Hrdata_0 (Hrdata_0),

.Hrdata_1 (Hrdata_1),

.Hrdata_2 (Hrdata_2),

.Hrdata_3 (Hrdata_3),

.master_m (Paddr),

//Output

.Prdata_m (Prdata_m)

);

endmodule

完整文件获取:

链接:https://pan.baidu.com/s/1cRyYGw_8OUj1fqqQRzQijw

提取码:xg5u