Quartus II调用modelsim无缝仿真

本篇文章为转载,写的不错,最近在学modelsim仿真,网上的教程很乱,把自己认为不错的整理贴出来,后面有机会会写个详细点的。

Quartus 中调用modelsim的流程

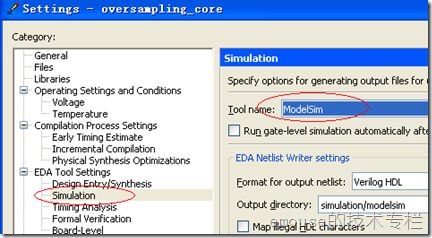

1. 设定仿真工具

assignmentèsettingèEDA tool settingèsimulation 选择你需要的工具。

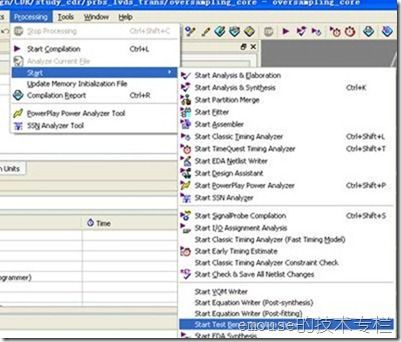

2. 自动产生测试激励文件模板:

processingèstartèStart test bench template writer

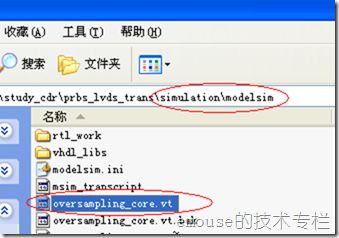

我们点击之后系统会自动在目录:当前文件夹è simulation è modelsim (这个文件夹名字跟你选的仿真工具有关) 中产生一个测试激励文件 xxx.vt(Verilog test bench) 或者 xxx.vht(VHDL test bench), 文件名跟你工程中的Top module 的名字一样, 后缀为.vt或者.vht。

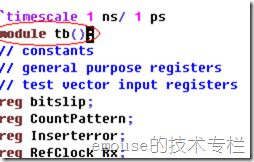

3. 编辑走动生成的test bench文件

我们加入自己需要的激励以及初始化语句,这里我们还要修改test bench的模块名字为tb(我们会看到这个名字和后面的设定有联系)。

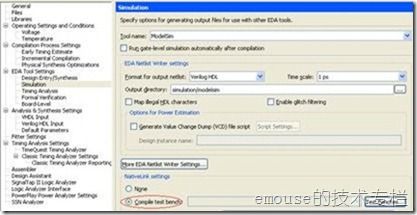

4. 连接test bench,我们需要从Quartus中自动调用仿真工具,所以需要设定Native Link选项。

a) 还是在simulation的设置页面里,设定 Native Link对话框中的设定。我们这里因为需要工具自动调用激励所以选中

b) 点击右边的Test Benches, 我们需要在这里设定一个相关联的test bench.

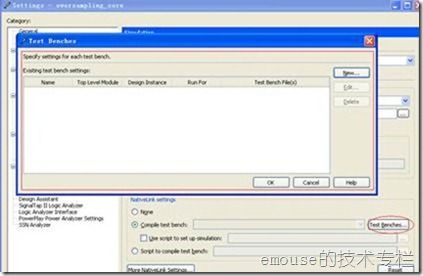

这里会弹出一个让你指定test bench的对话框,因为我们之前没有指定任何的test bench,所以这里是空白的。

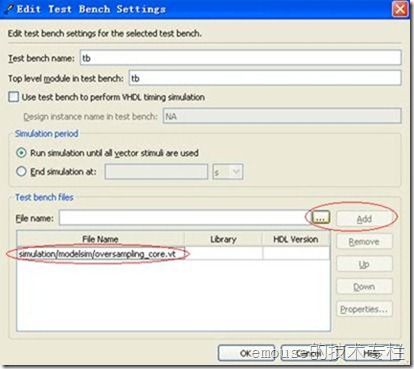

c) 指定test bench

因为我们是第一次产生test bench,点击new.

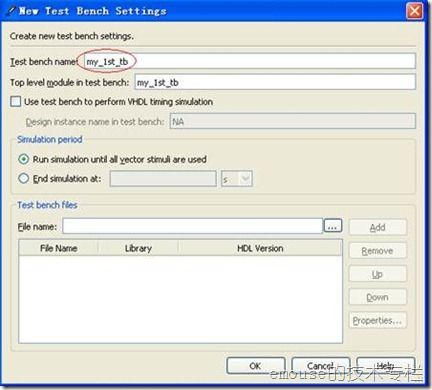

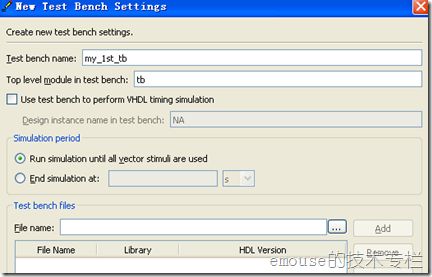

点击New之后会产生一个New Test bench setting的对话框,在这里你将test bench和你的相应的test bench file进行绑定。

我们这里在Test bench name的对话框中输入一个名字”my_1st_tb”, 我们将看到,在下面的Top level module in test bench对话框中也自动显示”my_1st_tb”. 注意这个名字应该和你的test bench 中的module name一直,我们之前在第3步的时候将test bench的module name已经改成了tb,所以我们这里应该把对话框中的名字改成tb。

5. 进行仿真

当这些设定都完成了之后, 选择菜单

toolèRun EDA Simulation toolèEDA RTL simulation

就可以直接调用modelsim进行仿真。

6. 小技巧:

我们这样调用仿真,如果是Modelsim AE每次不会编译lib文件,但如果我们使用的是Modelsim SE版本,每次调用都需要重新编译库,非常不爽,在这里我们建议自己修改脚本文件,进行仿真.

a) 当我们按照之前的描述,运行完仿真之后,停留在Modelsim的界面。

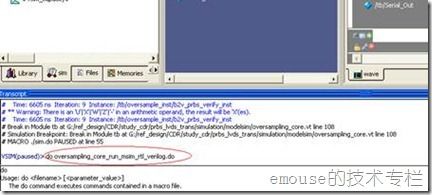

b) 在Modelsim界面的命令行上,我们点向上的方向键,就会出现我们上一条指令, 我们可以看到是

do xxxx.do 这说明工具执行的上一个命令式 xxxx.do这个脚本文件,我们这里的例子是

do oversampling_core_run_msim_rtl_verilog.do

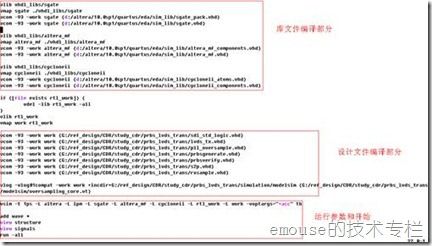

i. 我们知道了工具执行的脚本,我们就可以按照自己的想法去改变这个脚本了。使用

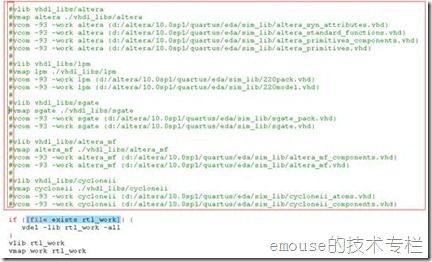

edit oversampling_core_run_msim_rtl_verilog.do命令,可以看到这个脚本的内容(当然我们也可以使用Ultra Edit或者VIM等文本编辑软件去打开这个脚本文件)。这个脚本通常分成3部分 库文件编译部分,设计文件编译,运行参数设定和开始执行部分

ii. 通常来说库文件只在第一次编译的时候,需要编译,后面我们只需要在仿真的时候指定库文件的位置就好了,不需要每次都编译。因此我们可以注释掉“库文件编译部分”。下面图中红色框中的部分就是被注释掉的库编译部分,这样会节省我们的仿真时间,注意在脚本语言中#是注释符。

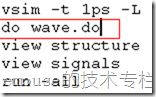

iii. 我们将编辑过的脚本文件另存为sim.do, 在以后的仿真中我们可以在Modelsim命令行中,直接在脚本中运行do sim.do(当然是先需要将Modelsim的工作目录改到 工程所在文件夹/simulation/modelsim/)。

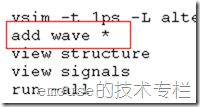

c) 另外脚本生成的波形文件通常是将test bench的顶层加入到图形画面中我们可以看到在脚本的第3部分(运行参数和开始执行)部分,默认命令式

add wave *, 这条命令就是讲 test bench顶层的所有信好加入到wave窗口中。

对我们来说,在调试阶段,有很多底层信号都是想观测的,所以需要再手动修改一下命令

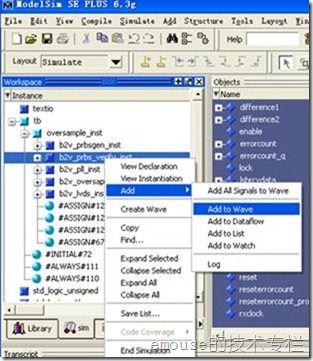

i. 在modelsim的窗口中,选中自己想要关心的模块,右键可以将自己关心的信号加入wave波形中

ii. 此时我们在wave 窗口中可以将这个波形的格式存下来,在wave窗口中点菜单fileèsave… 选择文件名为wave.do.

iii. 在我们执行的脚本中将add wave *,这个命令替换成do wave .do, 就可以在每次执行仿真的时候自动添加想要观测的波形了。 ![clip_image024[1] clip_image024[1]](http://img.e-com-net.com/image/product/63ebd001302e4ffe9318377d23429666.jpg)

7. 接下来最后一个问题,怎样才能一次性的编译好库文件,让软件不再每次编译。其实altera已经为客户准备了相应的选项,只不过藏得比较深,不好找。

a) 一次性编译库:

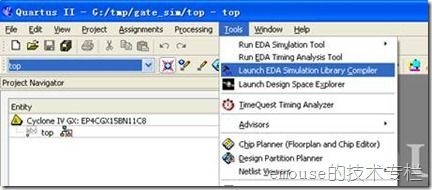

i. 点击toolè launch EDA simulation Library Compiler

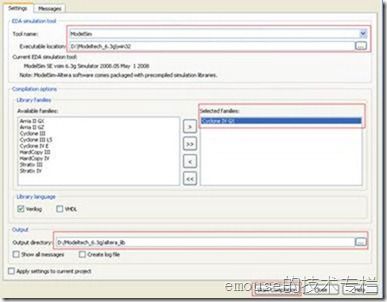

ii. 我们会看到一个让我们选择器件的页面。根据你的实际情况选择下面的设定。点击start compile,软件会自动帮你完成编译,然后关掉就好,至此你应该已经完成了库的编译。

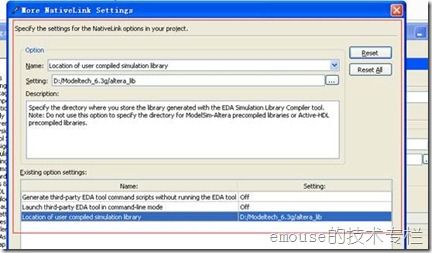

iii. 接下来我们需要在QII的仿真设定页面做一些修改。

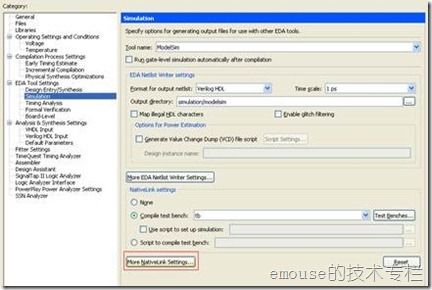

我们需要回到设定界面

Assignmentèsettingèsimulationèmore Nativelink setting

好了,重新run仿真,就发现不会再编译我们的库文件了。