VHDL之FSM

1 Intro

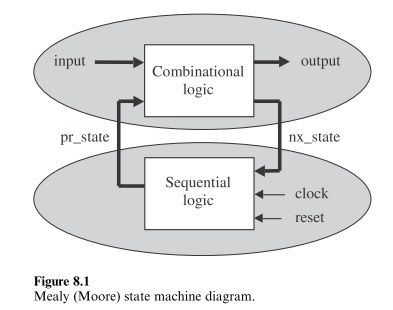

The figure shows the block diagram of a single-phase state machine. The lower section contains sequential logic (flip-flops), while the upper section contains combinational logic.

The combinational section has two inputs, pr_state (present state) and external input. It has also two outputs, nx_state (next state) and external output. The sequential section has three inputs (clock, reset, and nx_state), and one output (pr_state). Since all flip-flops are in this part of the system, clock and reset must be connected to it.

If the output of the machine depends not only on the present state but also on the current input, then it is called a Mealy machine. Otherwise, if it depends only on the current state, it is called a Moore machine. Examples of both will be shown later.

2 Design style (recommended)

1) Sequential

1 process (reset, clock) 2 begin 3 if (reset = '1') then 4 pr_state <= state0; 5 elsif (clock'event and clock = '1') then 6 pr_state <= nx_state; 7 end if; 8 end process;

It consists of an asynchronous reset, which determines the initial state of the system (state0), followed by the synchronous storage of nx_state (at the positive transition of clock), which will produce pr_state at the lower section’s output (figure 8.1).

One good thing is that the design of the lower section is basically standard. Another advantage is that the number of registers is minimum.

2) Combinational

1 process (input, pr_state) 2 begin 3 case pr_state is 4 when state0 => 5 if (input = ...) then 6 output <= <value>; 7 nx_state <= state1; 8 else ... 9 end if; 10 when state1 => 11 if (input = ...) then 12 output <= <value>; 13 nx_state <= state2; 14 else ... 15 end if; 16 when state2 => 17 if (input = ...) then 18 output <= <value>; 19 nx_state <= state2; 20 else ... 21 end if; 22 ... 23 end case; 24 end process;

As can be seen, this code is also very simple, and does two things:

(a) assign the output value

(b) establish the next state.

3 VHDL template

1 library ieee; 2 use ieee.std_logic_1164.all; 3 ----------------------------------------------------- 4 entity <entity_name> is 5 port( input : in <data_type>; 6 reset, clock : in std_logic; 7 output : out <data_type>); 8 end <entity_name>; 9 ----------------------------------------------------- 10 architecture <arch_name> of <entity_name> is 11 type state is (state0, state1, state2, state3, ...); 12 signal pr_state, nx_state: state; 13 14 begin 15 ---------- Sequential ------------------------ 16 process (reset, clock) 17 begin 18 if (reset='1') then 19 pr_state <= state0; 20 elsif (clock'event and clock='1') then 21 pr_state <= nx_state; 22 end if; 23 end process; 24 ---------- Combinational ------------------------ 25 process (input, pr_state) 26 begin 27 case pr_state is 28 when state0 => 29 if (input = ...) then 30 output <= <value>; 31 nx_state <= state1; 32 else ... 33 end if; 34 when state1 => 35 if (input = ...) then 36 output <= <value>; 37 nx_state <= state2; 38 else ... 39 end if; 40 when state2 => 41 if (input = ...) then 42 output <= <value>; 43 nx_state <= state3; 44 else ... 45 end if; 46 ... 47 end case; 48 end process; 49 50 end <arch_name>;