基于FPGA的数字信号发生器开发

目录

一、理论基础

二、FPGA程序

三、测试结果

一、理论基础

能够产生常规的波形,包括正弦波、方波和锯齿波;

用键盘输入编辑生成上述波形(同周期)的线性组合波形,以及由基波及其谐波(5次以下)线性组合波形;

具有波形存储功能;

输出波形频率范围为100Hz-200KHz,频率步进间隔<=100Hz;

输出波形幅度范围0-5V(峰-峰值),调整步距为0.1V;

能够显示输出波形的类型、频率和幅度;

这里,DDS的基本原理,就是将原始的信号保存到ROM中,然后通过频率控制字读取内部的信号,通过修改频率控制字的值,获得对应的频率值。

关于幅度,则通过将输入信号的幅度乘以一个固定的数,获得不同大小的频率。

输出波形频率范围为100Hz-200KHz,频率步进间隔<=100Hz;

输出波形幅度范围0-5V(峰-峰值),调整步距为0.1V;

假设晶振是40M,那么如果要输出100Hz到200K之间的频率范围。以正弦波为例子。

那么通过计算频率控制字,即如果以40M作为时钟频率,最小100Hz,最大200KHz,然后频率控制字为24bit宽度。

那么100hz对应的频率控制值为:

A:42(100/40000000*2^24)

B: 83886 (200000/40000000*2^24)

通过修改频率控制值,产生对应的不同的频率。

方波和锯齿波做同样的处理。

然后对于幅度,0~5.布局为0.1,那么其分辨率为0.1V。那么整个调整区间为50,那么对应的幅度,我们设置的位宽为12位(位数越高,其精度越高)

然后我们通过外部的按键,选择信号类型,信号频率,信号幅度。

然后再介绍一下那个线性组合的问题。

对于基波,我们直接通过加减法就可以实现。

对于谐波,因为谐波是指频率是基波频率整数倍的信号,那么在这里,我加入了频率为2~10倍这几种范围的谐波,具体只要选择对应频率的谐波即可。然后对将谐波加入到原始信号中即可。

二、FPGA程序

通过设置如下的接口,我们可以分别获得不同的信号组合,具体操作如下所示:

| input i_clk; |

系统时钟,默认时钟为40M |

| input i_rst; |

系统复位,输入1,系统清零复位,输入0,系统正常工作 |

| input[3:0] i_sel; |

信号类型选择按键,具体如下: //signal sel |

| input i_amp_add; |

幅度变大 |

| input i_amp_sub; |

幅度变小 |

| input i_fre_add; |

频率变大 |

| input i_fre_sub; |

频率变小 |

| input[3:0] i_fre_time; |

产生几倍频率谐波,2~15 |

| output[11:0]o_signal; |

输出信号 |

| output[31:0]o_fre; |

输出当前频率 |

| output[11:0]o_amp; |

输出当前幅度 |

| output[3:0] o_signal_type; |

输出信号类型 |

顶层程序如下:

`timescale 1ps / 1ps

module tops(

i_clk,

i_rst,

i_sel,

i_amp_add,

i_amp_sub,

i_fre_add,

i_fre_sub,

i_fre_time,

o_signal,

o_fre,

o_amp,

o_signal_type

);

input i_clk;

input i_rst;

input[3:0] i_sel; //signal sel

//0:sin

//1:square

//2:sawtooth

//3:k*sin

//4:k*square

//5:k*sawtooth

//6:sin+square

//7:sin+sawtooth

//8:sawtooth+square

//9:sin+sawtooth+square

//10:sin+ksin

//11:sawtooth+k*sawtooth

//12:square+k*square

input i_amp_add;

input i_amp_sub;

input i_fre_add;

input i_fre_sub;

input[3:0] i_fre_time;

output[11:0]o_signal;

output[23:0]o_fre;

output[6:0] o_amp;

output[3:0] o_signal_type;

reg[23:0]o_fre;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

o_fre <= 24'd83886;

end

else begin

//frequency adjust

//frequency adjust

if(i_fre_add == 1'b1)

o_fre <= o_fre + 24'd1;

if(i_fre_sub == 1'b1)

o_fre <= o_fre - 24'd1;

if(o_fre <= 24'd42)

o_fre <= 24'd42;

if(o_fre >= 24'd83886)

o_fre <= 24'd83886;

end

end

reg[5:0]amps;

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

amps <= 7'b0111_111;

end

else begin

//frequency adjust

//frequency adjust

if(i_amp_add == 1'b1)

amps <= amps + 7'd1;

if(i_amp_sub == 1'b1)

amps <= amps - 7'd1;

if(amps <= 7'b0000_001)

amps <= 7'b0000_001;

if(amps >= 7'b0111_111)

amps <= 7'b0111_111;

end

end

assign o_amp = amps;

assign o_signal_type = i_sel;

reg signed[18:0]tmps;

wire signed[11:0]sin1;

wire signed[11:0]cube1;

wire signed[11:0]saw1;

DDS base(

.i_clk (i_clk),

.i_rst (i_rst),

.i_k (4'd1),

.i_fre (o_fre),

.o_sin (sin1),

.o_cube (cube1),

.o_saw (saw1),

.o_fre (),

.o_test1(),

.o_test2()

);

wire signed[11:0]sink;

wire signed[11:0]cubek;

wire signed[11:0]sawk;

DDS h(

.i_clk (i_clk),

.i_rst (i_rst),

.i_k (i_fre_time),

.i_fre (o_fre),

.o_sin (sink),

.o_cube (cubek),

.o_saw (sawk),

.o_fre (),

.o_test1(),

.o_test2()

);

always @(posedge i_clk or posedge i_rst)

begin

if(i_rst)

begin

tmps <= 19'd0;

end

else begin

case(i_sel)

0:tmps <= amps*sin1;

1:tmps <= amps*cube1;

2:tmps <= amps*saw1;

3:tmps <= amps*sink;

4:tmps <= amps*cubek;

5:tmps <= amps*sawk;

6:tmps <= amps*sin1[11:1] + amps*cube1[11:1];

7:tmps <= amps*sin1[11:1] + amps*saw1[11:1];

8:tmps <= amps*saw1[11:1] + amps*cube1[11:1];

9:tmps <= amps*sin1[11:2] + amps*cube1[11:2] + amps*saw1[11:2];

10:tmps <= amps*sin1[11:1] + amps*sink[11:1];

11:tmps <= amps*cube1[11:1] + amps*cubek[11:1];

12:tmps <= amps*saw1[11:1] + amps*sawk[11:1];

default:tmps <= amps*sin1;

endcase

end

end

assign o_signal=tmps[18:7];

//0:sin

//1:square

//2:sawtooth

//3:k*sin

//4:k*square

//5:k*sawtooth

//6:sin+square

//7:sin+sawtooth

//8:sawtooth+square

//9:sin+sawtooth+square

//10:sin+ksin

//11:sawtooth+k*sawtooth

//12:square+k*square

endmodule 三、测试结果

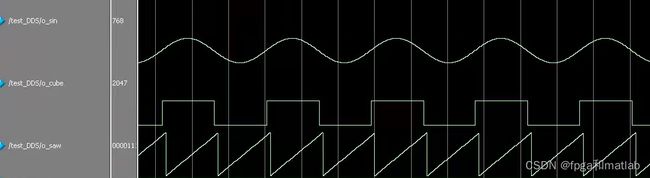

通过仿真,我们得到如下的几组信号:

A35-15