VGA显示的FPGA实现

1,VGA简介

VGA(Video Graphics Array),视频图形阵列,是一种使用模拟信号进行视频传输的标准协议。VGA接口中以针式引出信号线的称为公头,以孔式引出信号线的称为母头。VGA接口中,三基色的引脚传输的是模拟信号。

2,VGA显示原理

VGA显示器显示图像,是采用扫描的方式,将构成图像的像素点,在行、场同步信号的作用下,从上到下,由左到右的顺序扫描到显示器上。VGA的扫描规律如下:

(1)在行、场同步信号的同步作用下,扫描信号定位到左上角第一个像素点坐标;

(2)自左上角第一行第一个像素点坐标,逐个像素点向右扫描;

(3)扫描到第一行最后一个数据,一行图像扫描完成,进行图像消隐,扫描坐标自第一行行尾转移到第二行行首;

(4)重复若干次扫描至最后一行行尾,一帧图像扫面完成,进行图像消隐,扫描坐标跳转回左上角第一行行首,开始下一帧图像扫描。

(5)在扫描过程中回对每一个像素点单独赋值,使每个像素点显示对应色彩信息。

3,VGA时序标准

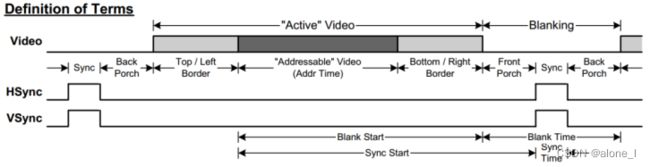

(1)VGA时序标准图

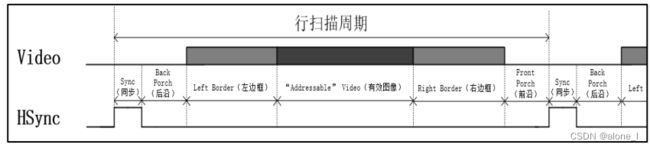

(2)行同步时序

一个完整的行扫描周期包含6个部分:sync(同步)、back potch(后沿)、left border(左边框)、addressable video(有效图像)、right border(右边框)、front(前沿)。在一个图像扫描周期中,图像在行同步信号下同步完成一行图像的扫描显示,图像信息只在“有效图像”阶段有效。行同步信号仅在同步阶段拉高,其余时间均为低。

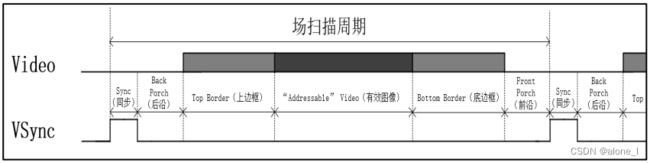

(3)场同步时序

一个完整的场扫描周期包含6个部分:sync(同步)、back porch(后沿)、top border(上边框)、video(有效图像)、bottom border(底边框)、front porch(前沿)

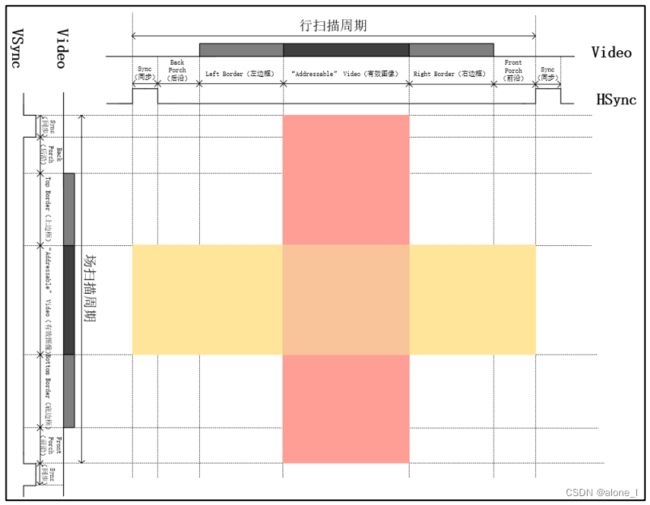

(4)VGA时序图

图中红色区域表示行扫描周期中图像有效区域;黄色区域表示场扫描周期中图像有效区域;两者相交的部分是图像的最终显示区域。

4,VGA显示模式及相关参数

行、场同步时序的6个阶段的参数是有严格定义的,参数配置不正确,VGA不能正常显示。对于不同的分辨率,所对应的各个阶段的分辨率是不同的,常用分辨率时序参数如下:

说明:以640x480@60为例。640指示每行的有效显示图像的像素点,480是指每一帧图像有480行,60是指刷新频率为60hz。vga显示驱动频率的计算:

行扫描周期 * 场扫描周期 * 刷新频率 = 时钟频率

*5,实例说明:在显示模式为640x480@60的显示器上显示十色等宽彩条。

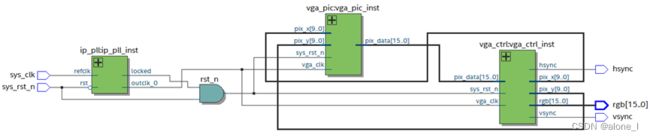

(1)整体设计的RTL图

该设计主要包括三个部分:vga时钟产生模块、vga显示控制模块、图像数据生成模块。

(2)时钟产生模块

时钟产生模块是利用IP核产生vga工作所需要的时钟,其中rst复位信号是高电平有效,所以在应用时需将其取反。时钟锁定信号locked是用来指示输出时钟的状态,在时钟震荡过程中locked保持低电平;在时钟稳定后,locked信号赋值高电平,表示输出时钟稳定且可被其他模块使用。

(3)vga时序控制模块

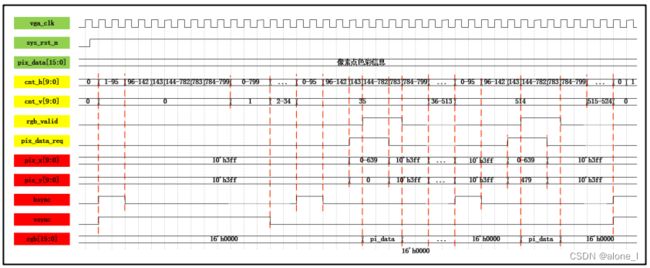

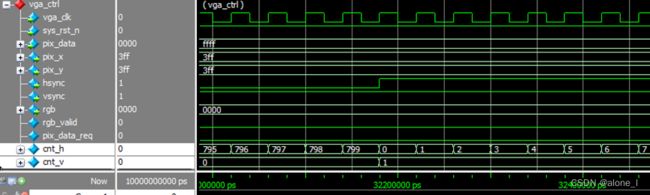

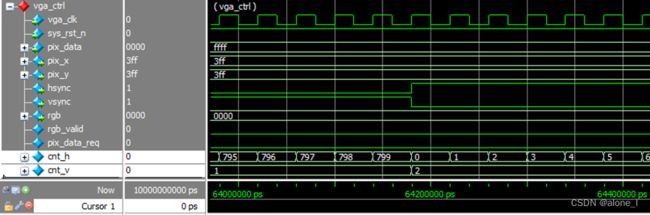

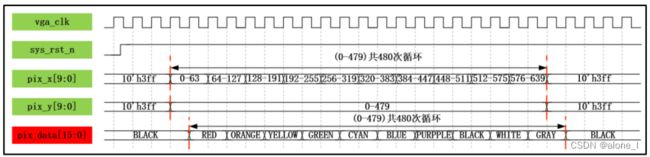

vga时序控制模块接收来自图像数据生成模块生成的彩条图像色彩信息,在模块内部使用使能信号滤除掉非图像显示有效区域的图像数据,产生RGB色彩信息,在行、场同步信号的同步作用下,将RGB色彩信息扫描显示到VGA显示器,显示出彩条图像。其参考波形图如下:

首先定义中间变量cnt_h、cnt_v用来对行扫描和场扫描进行计数;rgb_valid为图像显示有效信号;为了提高模块的复用性,所以将图像数据产生模块单独划分,因为数据生成模块需要坐标(pix_x,pix_y)为约束条件对pix_data信号进行赋值,只能次啊用时序逻辑的方式赋值,所以pix_data的赋值时刻会滞后条件满足时刻一个时钟周期,所以声明中间变量pix_data_req作为新的图像数据请求信号,该信号超前图像显示有效信号rgb_valid一个时钟周期,以抵消pix_data时序逻辑赋值带来的问题。

当cnt_h或cnt_v计数到图像有效区域时,对pix_或pix_y赋值,其值为当前cnt_h或cnt_v的值减去前面无效区域的值。行、场同步信号hsync,vsync在同步阶段拉高,其余时间保持低电平。最后在图像有效区域将色彩信息rgb输出即可。

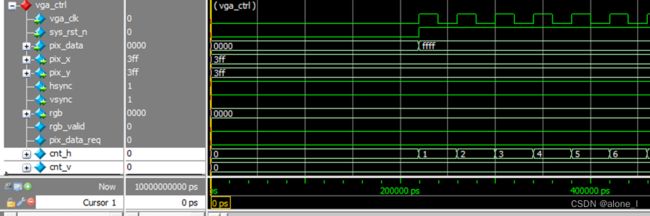

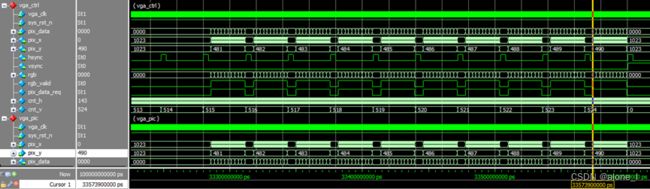

该模块的仿真

a,显示开始

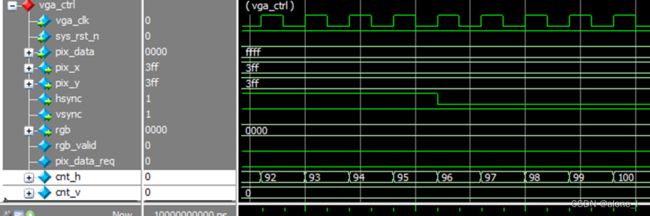

b,行计数器计数到95时将行同步信号拉低

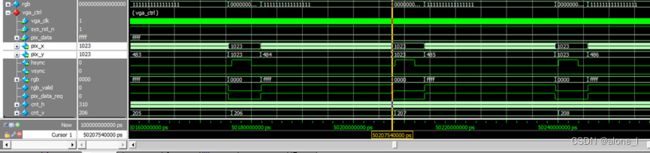

c,行计数器计数到799时清零,下一行开始,场计数器加一

d,场同步信号拉低

e,整体仿真

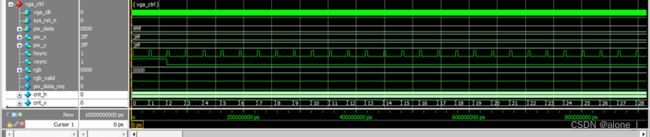

(4)图像数据生成模块

该模块以VGA时序控制模块传入的像素点坐标(pix_x,pix_y)为约束条件,生成待显示彩条图像的色彩信息。模块的波形图如下:

(5)整个工程的仿真结果

从仿真结果来看,基本能够实现彩条显示的功能。

![]()

6,参考内容:

野火 FPGA Verilog 开发实战指南 VGA显示驱动设计与验证。

7,完整工程

https://download.csdn.net/download/alone_l/85459183