m基于FPGA的数字下变频verilog设计(含FPGA,详细文档及操作录像)

目录

1.源码获取方式

2.算法描述

3.部分程序

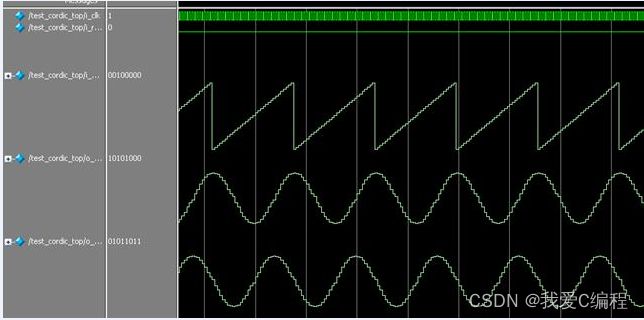

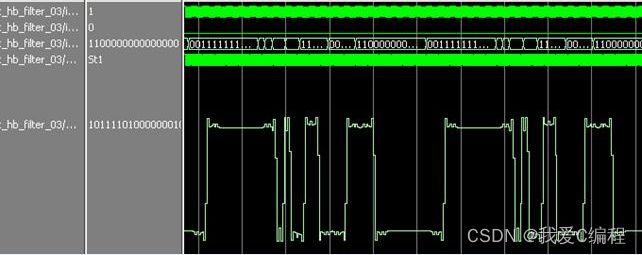

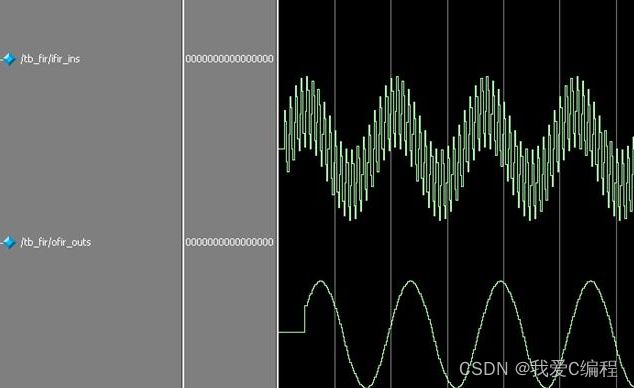

4.部分仿真图预览

1.源码获取方式

使用版本

quartusii10.0,ModelSim-Altera 6.6d Starter Edition

获取方式1:

点击下载链接(解压密码C+123456):

m基于FPGA的数字下变频verilog设计

获取方式2:

如果下载链接失效,加博主微信联系,或私信联系。

2.算法描述

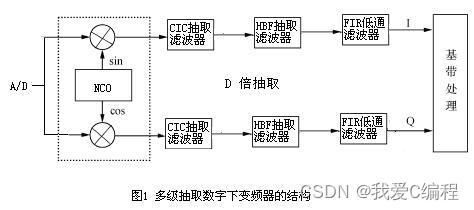

整个数字下变频的基本结构如下所示

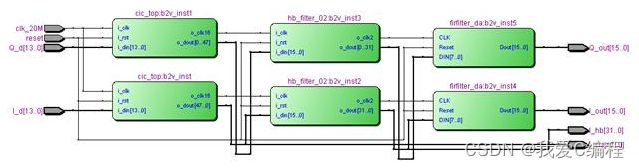

NCO使用CORDIC算法,CIC采用h结构的CIC滤波器,HBF采用复用结构的半带滤波器,而FIR则采用DA算法结构。

这里,我们首先假设不考虑中频信号输入的载波频偏问题,即发送的中频频率和本地的载波频率是一致的。

为了验证系统的正确性,我们首先需要设计一个发送源,由于你要求的信号带宽为20M,

所以整个系统我们设计的系统参数为,中频为80M,A/D采样为60M。本地接收端的载波频率为20M。

即发送端通过80M的中频调制之后,信号的频谱会搬移到80M附近,然后接收端通过AD60M采样后,会将频谱搬移到20M附近,且不会发生混叠现象。

那么系统测试方案可以简化为,一个中心频率在20M附近的中频输入测试信号进行测试。

首先设计一个发送测试信号。

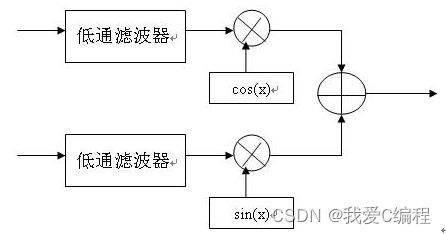

信号的基本结构如下所示:

我们首先在FPGA中设计这么一个结构得到中频测试信号,然后使用这个测试信号进行下变频测试。

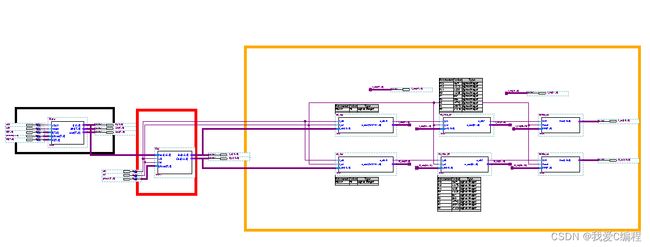

整个系统的原理框图如下所示:

RTL图:

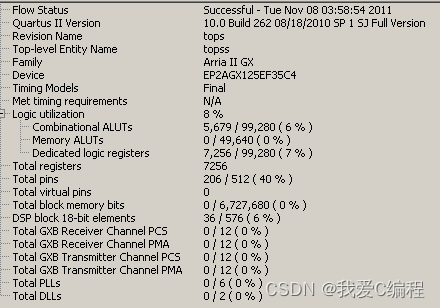

综合资源占用:

3.部分程序

// Copyright (C) 1991-2010 Altera Corporation

// Your use of Altera Corporation's design tools, logic functions

// and other software and tools, and its AMPP partner logic

// functions, and any output files from any of the foregoing

// (including device programming or simulation files), and any

// associated documentation or information are expressly subject

// to the terms and conditions of the Altera Program License

// Subscription Agreement, Altera MegaCore Function License

// Agreement, or other applicable license agreement, including,

// without limitation, that your use is for the sole purpose of

// programming logic devices manufactured by Altera and sold by

// Altera or its authorized distributors. Please refer to the

// applicable agreement for further details.

// PROGRAM "Quartus II"

// VERSION "Version 10.0 Build 262 08/18/2010 Service Pack 1 SJ Full Version"

// CREATED "Tue Nov 08 03:39:48 2011"

module tops2(

reset,

clk,

clk0,

rst0,

clk1,

rst1,

I0,

phase0,

phase1,

Q0,

cosr,

I_cic,

I_d,

I_hb,

I_out,

Q_d,

Q_out,

R,

sinr

);

input wire reset;

input wire clk;

input wire clk0;

input wire rst0;

input wire clk1;

input wire rst1;

input wire [7:0] I0;

input wire [7:0] phase0;

input wire [7:0] phase1;

input wire [7:0] Q0;

output wire [7:0] cosr;

output wire [47:0] I_cic;

output wire [13:0] I_d;

output wire [31:0] I_hb;

output wire [15:0] I_out;

output wire [13:0] Q_d;

output wire [15:0] Q_out;

output wire [13:0] R;

output wire [7:0] sinr;

wire [47:0] I_cic_ALTERA_SYNTHESIZED;

wire [31:0] I_hb_ALTERA_SYNTHESIZED;

wire [47:0] Q_cic;

wire [31:0] Q_hb;

wire [13:0] SYNTHESIZED_WIRE_0;

wire [13:0] SYNTHESIZED_WIRE_1;

wire [13:0] SYNTHESIZED_WIRE_2;

wire SYNTHESIZED_WIRE_3;

wire SYNTHESIZED_WIRE_4;

wire SYNTHESIZED_WIRE_5;

wire SYNTHESIZED_WIRE_6;

assign I_d = SYNTHESIZED_WIRE_0;

assign Q_d = SYNTHESIZED_WIRE_1;

assign R = SYNTHESIZED_WIRE_2;

cic_top b2v_inst(

.i_clk(clk),

.i_rst(reset),

.i_din(SYNTHESIZED_WIRE_0),

.o_clk16(SYNTHESIZED_WIRE_3),

.o_dout(I_cic_ALTERA_SYNTHESIZED));

defparam b2v_inst.WIDTH = 48;

cic_top b2v_inst1(

.i_clk(clk),

.i_rst(reset),

.i_din(SYNTHESIZED_WIRE_1),

.o_clk16(SYNTHESIZED_WIRE_4),

.o_dout(Q_cic));

defparam b2v_inst1.WIDTH = 48;

Rec b2v_inst12(

.clk(clk1),

.rst(rst1),

.phase(phase1),

.recs(SYNTHESIZED_WIRE_2),

.Iss(SYNTHESIZED_WIRE_0),

.Qss(SYNTHESIZED_WIRE_1));

hb_filter_02 b2v_inst2(

.i_clk(SYNTHESIZED_WIRE_3),

.i_rst(reset),

.i_din(I_cic_ALTERA_SYNTHESIZED[34:19]),

.o_clk2(SYNTHESIZED_WIRE_5),

.o_dout(I_hb_ALTERA_SYNTHESIZED));

defparam b2v_inst2.h0 = 27316;

defparam b2v_inst2.h1 = 20073;

defparam b2v_inst2.h11 = 1238;

defparam b2v_inst2.h13 = -1175;

defparam b2v_inst2.h15 = -624;

defparam b2v_inst2.h3 = -4745;

defparam b2v_inst2.h5 = 965;

defparam b2v_inst2.h7 = 667;

defparam b2v_inst2.h9 = -1238;

hb_filter_02 b2v_inst3(

.i_clk(SYNTHESIZED_WIRE_4),

.i_rst(reset),

.i_din(Q_cic[34:19]),

.o_clk2(SYNTHESIZED_WIRE_6),

.o_dout(Q_hb));

defparam b2v_inst3.h0 = 27316;

defparam b2v_inst3.h1 = 20073;

defparam b2v_inst3.h11 = 1238;

defparam b2v_inst3.h13 = -1175;

defparam b2v_inst3.h15 = -624;

defparam b2v_inst3.h3 = -4745;

defparam b2v_inst3.h5 = 965;

defparam b2v_inst3.h7 = 667;

defparam b2v_inst3.h9 = -1238;

firfilter_da b2v_inst4(

.CLK(SYNTHESIZED_WIRE_5),

.Reset(reset),

.DIN(I_hb_ALTERA_SYNTHESIZED[30:23]),

.Dout(I_out));

firfilter_da b2v_inst5(

.CLK(SYNTHESIZED_WIRE_6),

.Reset(reset),

.DIN(Q_hb[30:23]),

.Dout(Q_out));

Trans b2v_inst6(

.clock(clk0),

.reset(rst0),

.I(I0),

.phase(phase0),

.Q(Q0),

.cosr(cosr),

.r(SYNTHESIZED_WIRE_2),

.sinr(sinr));

assign I_cic = I_cic_ALTERA_SYNTHESIZED;

assign I_hb = I_hb_ALTERA_SYNTHESIZED;

endmodule

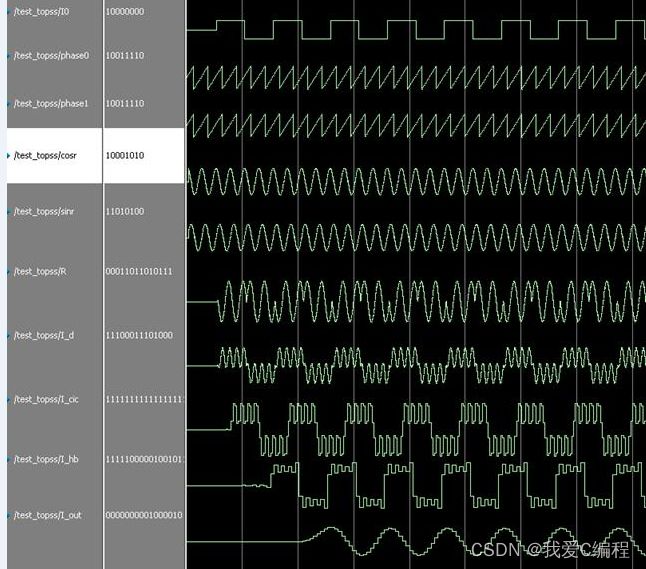

4.部分仿真图预览

01_115m