- 基于ARM的智能车载导航系统的设计与实现

柠檬树技术宅

51单片机物联网阿里云stm32单片机

主控采用stm32单片机1、实现高精度定位:通过集成GPS进行定位。3、用户友好的界面设计:oled显示器显示经纬度值。5、车辆信息集成:集成车辆信息,霍尔传感器监测车速包括车速、行驶里程。9、考虑车载环境下的特殊需求:考虑车载环境对系统的特殊要求,温度传感器监测温度,震动传感器监测有无异常震动,如高温、振动等,确保系统在各种极端条件下都能够正常运行。显示器可以显示温度、有无震动、定位经纬度、车速

- Python爬取微博(APP)榜单爬虫及数据可视化,整理出Python逆向系列学习进阶视频

weixin_58134620

2024年程序员学习python爬虫信息可视化

f=open(‘1.csv’,‘w+’,encoding=‘utf-8’,newline=‘’)writer=csv.writer(f)writer.writerow([‘user_id’,‘user_location’,‘user_gender’,‘user_follower’,‘text’,‘created_time’,‘reposts_count’,‘comments_count’,‘att

- STM32单片机 定时器TIM输出比较 PWM波形

斯kk

单片机stm32嵌入式硬件

一.OC(OutputCompare)输出比较了解:IC(InputCapture)输入捕获、CC(Capture/Compare)输入捕获和输出比较单元OC功能:用来输出PWM波形,PWM波形又是用来驱动电机的必要条件,用来做智能车、机器人等输出比较可以通过比较CNT计数器与CCR捕获/比较寄存器值的关系,来对输出电平进行置1、置0或翻转的操作,用于输出一定频率和占空比的PWM波形。当CNT>C

- 车载摄像头EMC问题剖析

硬核科技

安规EMC测试电脑高速电路PDNEMC认证测试测试EMI

随着智能驾驶技术的快速发展,车载摄像头已经从辅助性设备跃升为主动感知系统的核心组成部分。不论是360度全景监控、ADAS辅助驾驶功能,还是日益普及的自动泊车系统,摄像头的性能和稳定性已成为智能车辆安全运行的重要保障。然而,随着系统复杂度的提升,电磁兼容性(EMC)问题也随之凸显,尤其在高频传输和集成化设计背景下,成为整车系统测试中的一个关键难点。一、车载摄像头与EMC的冲突背景车载摄像头的典型硬件

- 基于YOLOv10的交通标志识别系统设计与实现(Traffic Sign Recognition)

YOLO实战营

YOLO目标检测人工智能深度学习ui

1.交通标志识别简介交通标志识别(TrafficSignRecognition,TSR)是智能交通系统(ITS)中的重要一环,广泛应用于自动驾驶辅助系统(ADAS)、智能车辆导航以及交通流量管理等领域。通过自动识别道路上的交通标志信息,车辆可以更安全、高效地进行路径规划和行驶控制。传统方法多依赖图像处理和手工特征,而现代深度学习技术通过端到端训练大幅提高了识别准确率和鲁棒性。基于YOLO(YouO

- 【区块链 | Solidity】Solidity开发教程:用Web3.js构建第一个Dapp

区块链(Web3)开发工程师

区块链web3javascript1024程序员节

Web3.js使用的实用介绍原文作者:wissalhaji欢迎订阅《Solidity智能合约零基础开发教程专栏》系列文章。如果你一直在跟着这个系列学习,那么你已经掌握了编写自己的智能合约。因此,今天给大家介绍一下构建去中心化应用的全貌,并向大家介绍一下web3.js,这是构建dapp不可缺失部分。

- [TriCore][官方例程][TC397以太网例程详解] - 18.ECHO 应用 - 接收报文

MaoXian_n

TriCore官方例程驱动开发tcp/ip嵌入式硬件单片机网络协议

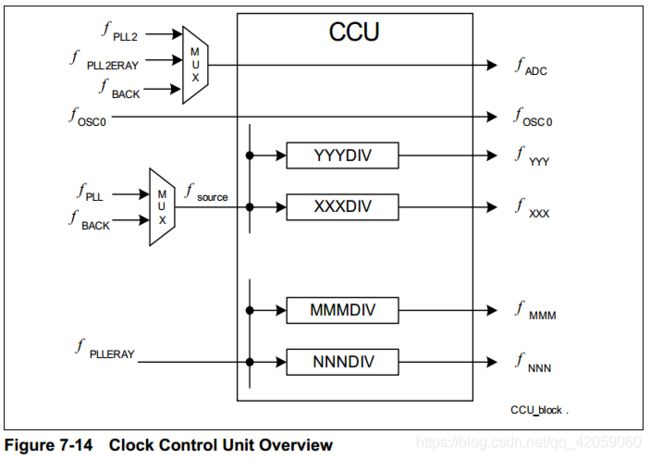

关键词TC397官方例程;TC397以太网例程;TC397GETH;简介本篇为AurixTriCoreTC397以太网官方例程分析,重点关注其硬件行为调试所用的开发板型号:KIT-A2G-TC397-5V-TFT所使用的例程:Ethernet_1_KIT_TC397_TFT英飞凌TriCore官方例程下载地址:https://github.com/Infineon/AURIX_code_examp

- 智能车域控制器设计——AutoSAR

程序员杨弋

AUTOSAR

随着人工智能和自动驾驶技术的快速发展,智能车域控制器成为了汽车行业中的重要组成部分,AutoSAR即汽车软件架构(AuomoiveOpensysiemArchiecture)为智能车域控制器的设计提供了一个开放且标准化的平台,本文将探讨智能车域控制器的设计原理,并给出相应的源代码示例。一、智能车域控制器概述智能车域控制器是指具有边缘计算和智能:决策能力的汽车电子控制单元(ECU),它负责管理车辆的

- Hacker-基础学习(1)

weixin_34081595

操作系统后端网络

最近在看一本关于hacker的书,想将一些相关的知识点做个汇总和笔记,方便日后的查阅也方便现在的学习。因为看的都是web篇的实战,所以该系列学习会偏向web的内容,本章将从三个方面阐述1.攻防永远都是不对等的;2.核心防御方法;3.辅助攻击软件。攻防永远都是不对等的为什么说Web应用上的攻防不对等?其本质在于所有的程序都有漏洞,世界上不存在完美的程序。大部分的Web漏洞分为以下几种1.不完善的身份

- Ecall P1140:车载紧急通讯的未来

众乐 认证

网络人工智能

随着科技的飞速发展,智能出行已经成为我们生活的一部分。EcallP1140,作为新一代的智能车载系统,正引领着这一变革,为我们的驾驶体验带来前所未有的便捷与安全。EcallP1140车载紧急呼叫系统概述EcallP1140,即ITU-TP.1140,是由国际电信联盟(ITU)提出的一套车载紧急呼叫系统的语音清晰度和通信效率的测试方法和要求。该系统旨在车辆发生事故或紧急情况下,通过自动或手动触发紧急

- 智能车联网安全发展形势、挑战

安全方案

安全

一、技术演进加速车联网安全环境复杂变化当前,5G、大数据、大算力、大模型等技术正加速在车联网领域实现融合应用。车联网的网络通信能力、感知计算水平以及创新业务应用都在快速发展,与此同时,车联网的网络安全环境也在随之演进变化,安全需求更多、保障要求更高、防护范围更广。(一)网络通信路径多元化一是车路云网通信交互显著增多。预测显示,2024年全球5G基站总数将超480万个,装配路侧联网设备近万套。据St

- 智能车速度刷新:仅10个月,首个纯端侧大模型上车量产!

量子位

原创关注前沿科技量子位端侧大模型圈子的《速度与激情》,就这么水灵灵地上演了。坐标上海车展,在长安马自达新车发布之际,车上的智能座舱竟然成了大亮点之一。因为速度着实有点太快——从零到量产,只花了10个月的时间!要知道,这件事儿在汽车领域里面,一般都是要按“年”这个单位来计算。此举可谓是一鸣惊人,一举刷新行业纪录,一步迈进了“月”的计量单位。而且啊,搞出这件事的,还是车圈的一位“新手”——面壁智能。没

- 商用车与农用车电气/电子架构 --- 赋能智能车队管理与远程信息处理

汽车电子实验室

汽车行业思考架构赋能智能车队管理与远程信息处理商用车与农用车电气/电子架构汽车电子电器架构二级boot设计说明需求规范

我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师:钝感力的“钝”,不是木讷、迟钝,而是直面困境的韧劲和耐力,是面对外界噪音的通透淡然。生活中有两种人,一种人格外在意别人的眼光;另一种人无论别人如何,他们始终有自己的节奏。过度关注别人的看法,会搅乱自己的步调,让自己更加慌乱。与其把情绪的开关交到别人手中,不如把有限的精力用在提升自己上

- 共享单车的通信原理解析

Miki_souls

付费专栏交通物流

共享单车作为城市短途出行的核心工具,其便捷性离不开复杂的通信技术支撑。本文将从通信系统架构、数据传输技术、定位与交互逻辑等角度,解析共享单车的通信原理。一、通信系统的硬件构成共享单车的通信系统主要由以下核心硬件组成:智能车锁集成嵌入式芯片、通信模块(支持2G/3G/4G/NB-IoT等)、GPS模块和物联网SIM卡,负责车辆控制、数据传输与定位。供电装置通过骑行时车轮转动切割磁感线发电,或内置可充

- 嵌入式智能车设计与实现 —— STM32F429版深度解析

2022级物联网应用技术1班 钟辉均

单片机嵌入式硬件

引言随着物联网和人工智能的发展,嵌入式智能车成为了一个热门的研究领域。本文将深入介绍如何使用STM32F429微控制器设计和实现一款基础的智能车,包括硬件选型、电路设计、软件编程等关键环节,旨在为嵌入式系统爱好者和工程师提供一个全面的技术指南。理论框架嵌入式系统理论微控制器(MCU)理论:STM32F429基于ARMCortex-M4架构,拥有浮点运算单元(FPU),适用于复杂算法处理。其内部结构

- 【图像分类】【深度学习】系列学习文章目录

牙牙要健康

图像分类深度学习分类深度学习数据挖掘

图像分类简介图像分类是计算机视觉领域中的一个核心问题,它涉及到将图像数据分配到一个或多个预定义类别中的过程。这项技术的目标是让机器模拟人类能够自动识别并分类图像内容。近年来,随着深度学习的发展,尤其是卷积神经网络(CNNs)的应用,图像分类的准确率得到了显著提升。CNNs可以自动地从原始图像中学习和提取分层的特征表示,而无需手工设计特征。这使得它们在许多复杂的图像分类任务上超越了传统方法,最近,又

- 嵌入式硬件自学思路 | PCB设计零基础入门-小白适用(附详细入门经验分享)

自动化小秋葵

stm32PCB嵌入式硬件嵌入式原理图

前言本人大一在实践课上就听说PCB,被虎的一楞一楞的,不过现在回看,发现其实并没有相信的那么难!想着把自己这一路摸索的学习路线分享一下,当时我是一边摸索一边上手,一把鼻涕一把泪的过来的。如果你想搞硬件或者需要搞硬件,下面是我的入门学习过程,希望可以帮到你。学完以后智能车硬件轻松搞定。目录前言选择一款设计软件好的入门课程掌握抄板元件采购焊板子烙铁头热风枪自己半设计明确设计需求全设计最后选择一款设计软

- 智能车摄像头开源—1.1核心代码:自适应八向迷宫(上)

三唐队队长

开源算法图像处理嵌入式硬件

目录一、开源项目简介二、前期探索与算法确定1.常用二值化算法对比(个人经验)大津法卷积核差比和自适应迷宫(八领域)三、自适应八向迷宫一、开源项目简介2024.8.19,决战前夕,正式决定将十个多月来的心血进行开源。本在区赛打完之后,就计划如果国一,就部分开源,若是国二,就全部开源。但显然,在封车的那一刻,结局就已经注定,已经无望国一。所以此行怀揣失意而来,注定满载遗憾而去,但不甘心于自己所有的成果

- 智能车摄像头开源—9 动态权、模糊PID、速度决策、路径优化

三唐队队长

图像处理人工智能算法开源嵌入式硬件边缘计算

目录一、前言二、动态权1.概述2.偏差值加动态权三、模糊PID四、速度决策1.曲率计算2.速度拟合3.速度控制五、路径六、国赛视频一、前言在前中期通过识别直道、弯道等元素可进行加减速操作实现速度的控制,可进一步缩减一圈的运行速度,但会出现刹车不及时、加速不及时、车路径较差等问题,反而导致处理后运行一圈时间反而多于之前。由此我们引入多个方法,使车辆能自行解算自行控制速度、转向力度等,以跑出最好效果。

- 高校单片机毕业设计大全题目(论文+源码)

毕设工作室_wlzytw

python论文项目单片机课程设计嵌入式硬件stm3251单片机proteus

单片机毕业设计大全题目(论文+源码)_kaic1基于单片机的温度湿度监测与控制系统2.基于单片机的智能照明控制系统3.基于单片机的家庭安防系统4.基于单片机的智能门禁系统5.基于单片机的智能插座设计6.基于单片机的智能楼宇管理系统7.基于单片机的智能家居控制系统8.基于单片机的环境监测与报警系统9.基于单片机的智能车库门控制系统10.基于单片机的智能农田灌溉系统11.基于单片机的智能垃圾分类回收系

- lasso模型交替方向matlab_TCGA系列学习笔记(7)建模及模型评价

weixin_39782752

微信公众号:生信小知识关注可了解更多的教程及单细胞知识。问题或建议,请公众号留言;TCGA系列学习笔记(7)建模及模型评价内容目录前言1.背景知识1.1Cox前提假设的验证1.2lasso和ridge回归1.3C-index1.3.1如何计算1.3.2关于C-index的取值1.3.3用R计算C-index1.4Cox模型验证1.4.1数据拆分1.4.2ROC和AUC1.5逐步回归1.6nomog

- 英飞凌 AURIX 系列单片机的HSM详解(5)——HSM硬件加速模块的使用

king110108

信息安全(CyberSecurity)HSM

本系列的其它几篇文章:《英飞凌AURIX系列单片机的HSM详解(1)——何为HSM》《英飞凌AURIX系列单片机的HSM详解(2)——与HSM相关的UCB和寄存器》《英飞凌AURIX系列单片机的HSM详解(3)——开发方法》《英飞凌AURIX系列单片机的HSM详解(4)——Tricore核与HSM核之间的通信方法》《英飞凌AURIX系列单片机的HSM详解(5)——HSM硬件加速模块的使用》1.概述

- 区块链3.0:拥抱EOS

链客区块链技术问答社区

区块链

链客,专为开发者而生,有问必答!此文章来自区块链技术社区,未经允许拒绝转载。EOS是当下最火的区块链技术,被社会广泛看好为下一代区块链3.0。不同于以太坊的学习,EOS的主语言是C++,本文作为EOS研究的首篇文章,重点介绍EOS的创新点,它的周边生态,各种概念原理的解释,以及它被看好的原因。而针对EOS的源码学习,原理实现以及并行的C++语言的快速学习与掌握,我会在接下来制定一系列学习计划一一付

- 一周速递|全球车联网产业动态(2024年7月28日)

有辕有辙_智能网联

汽车物联网人工智能大数据

政策法规1、7月26日,苏州市工信局近日印发《关于开展2024年苏州市智能车联网典型示范应用场景遴选工作的通知》,将围绕公共管理、示范运营、公共服务等方面,包括但不限于智慧公交、智慧乘用车(自动驾驶出租车)、智慧物流、智慧环卫、智慧配送、智慧巡逻以及停车场自动泊车等重点领域,遴选一批智能车联网典型示范应用场景,单个项目最高补助100万元。2、7月25日,《广州市智能网联汽车创新发展条例(草案修改稿

- 探索TriCore架构:AURIX芯片的强大内核

裴辰垚Simone

探索TriCore架构:AURIX芯片的强大内核g_tricore_architecture项目地址:https://gitcode.com/gh_mirrors/gt/g_tricore_architecture项目介绍TriCore架构是英飞凌(Infineon)公司开发的一种高性能、低功耗的嵌入式处理器架构,广泛应用于汽车电子、工业控制和消费电子等领域。AURIX系列芯片是基于TriCore

- Spring系列学习之Spring Messaging消息支持

m0_74825488

面试学习路线阿里巴巴springlinqjava

英文原文:https://docs.spring.io/spring-boot/docs/current/reference/html/boot-features-messaging.html目录JMSActiveMQ支持Artemis支持使用JNDIConnectionFactory发送消息接收消息AMQPRabbitMQ支持发送消息接收消息ApacheKafka支持发送消息接收消息Kafka流

- Simulink实例演示:智能车辆远程驾驶控制系统仿真

xiaoheshang_123

MATLAB开发项目实例1000例专栏手把手教你学MATLAB专栏simulinkmatlab自动驾驶人工智能机器学习

目录Simulink实例演示:智能车辆远程驾驶控制系统仿真一、背景介绍二、所需工具和环境三、步骤详解步骤1:创建Simulink模型步骤1.1:打开Simulink并新建模型步骤2:设计车辆动力学模型步骤2.1:添加车辆底盘模块步骤2.2:添加纵向和横向控制模块步骤2.3:连接各模块步骤3:设计动力总成系统步骤3.1:选择动力源类型步骤3.2:配置动力总成参数步骤3.3:连接动力总成模块到车辆底盘

- 38份DeepSeek核心资料汇总|可下载

航锦234

人工智能pdf

资料链接:https://pan.quark.cn/s/b469ed4018ff为了方便大家查找和使用,我们对之前发布过的DeepSeek系列学习资料进行了分类和汇总。内容包括但不限于清北浙DeepSeek课件资料汇总manus学习资料DeepSeek实操变现指南DeepSeek本地部署教学等等点击最上方链接即可保存下载~

- Simulink实例演示:智能车辆自动超车策略仿真

xiaoheshang_123

手把手教你学MATLAB专栏MATLAB开发项目实例1000例专栏matlabsimulink

目录Simulink实例演示:智能车辆自动超车策略仿真一、背景介绍二、所需工具和环境三、步骤详解步骤1:创建Simulink模型

- 智能车辆控制技术:MPC与轨迹规划实战项目

柚木i

本文还有配套的精品资源,点击获取简介:本压缩包集合了车辆转向控制与轨迹规划的MATLAB代码,包含模型预测控制(MPC)策略、MPT工具箱应用、车辆动力学模型构建、轨迹规划实现、mp-QP算法应用及MATLAB编程实践。旨在通过源码分析,提供智能车辆控制技术的深入学习与研究平台,涉及横向和纵向运动控制、系统模型的定义、控制策略的制定及仿真流程。1.模型预测控制(MPC)基础与应用模型预测控制(MP

- [星球大战]阿纳金的背叛

comsci

本来杰迪圣殿的长老是不同意让阿纳金接受训练的.........

但是由于政治原因,长老会妥协了...这给邪恶的力量带来了机会

所以......现代的地球联邦接受了这个教训...绝对不让某些年轻人进入学院

- 看懂它,你就可以任性的玩耍了!

aijuans

JavaScript

javascript作为前端开发的标配技能,如果不掌握好它的三大特点:1.原型 2.作用域 3. 闭包 ,又怎么可以说你学好了这门语言呢?如果标配的技能都没有撑握好,怎么可以任性的玩耍呢?怎么验证自己学好了以上三个基本点呢,我找到一段不错的代码,稍加改动,如果能够读懂它,那么你就可以任性了。

function jClass(b

- Java常用工具包 Jodd

Kai_Ge

javajodd

Jodd 是一个开源的 Java 工具集, 包含一些实用的工具类和小型框架。简单,却很强大! 写道 Jodd = Tools + IoC + MVC + DB + AOP + TX + JSON + HTML < 1.5 Mb

Jodd 被分成众多模块,按需选择,其中

工具类模块有:

jodd-core &nb

- SpringMvc下载

120153216

springMVC

@RequestMapping(value = WebUrlConstant.DOWNLOAD)

public void download(HttpServletRequest request,HttpServletResponse response,String fileName) {

OutputStream os = null;

InputStream is = null;

- Python 标准异常总结

2002wmj

python

Python标准异常总结

AssertionError 断言语句(assert)失败 AttributeError 尝试访问未知的对象属性 EOFError 用户输入文件末尾标志EOF(Ctrl+d) FloatingPointError 浮点计算错误 GeneratorExit generator.close()方法被调用的时候 ImportError 导入模块失

- SQL函数返回临时表结构的数据用于查询

357029540

SQL Server

这两天在做一个查询的SQL,这个SQL的一个条件是通过游标实现另外两张表查询出一个多条数据,这些数据都是INT类型,然后用IN条件进行查询,并且查询这两张表需要通过外部传入参数才能查询出所需数据,于是想到了用SQL函数返回值,并且也这样做了,由于是返回多条数据,所以把查询出来的INT类型值都拼接为了字符串,这时就遇到问题了,在查询SQL中因为条件是INT值,SQL函数的CAST和CONVERST都

- java 时间格式化 | 比较大小| 时区 个人笔记

7454103

javaeclipsetomcatcMyEclipse

个人总结! 不当之处多多包含!

引用 1.0 如何设置 tomcat 的时区:

位置:(catalina.bat---JAVA_OPTS 下面加上)

set JAVA_OPT

- 时间获取Clander的用法

adminjun

Clander时间

/**

* 得到几天前的时间

* @param d

* @param day

* @return

*/

public static Date getDateBefore(Date d,int day){

Calend

- JVM初探与设置

aijuans

java

JVM是Java Virtual Machine(Java虚拟机)的缩写,JVM是一种用于计算设备的规范,它是一个虚构出来的计算机,是通过在实际的计算机上仿真模拟各种计算机功能来实现的。Java虚拟机包括一套字节码指令集、一组寄存器、一个栈、一个垃圾回收堆和一个存储方法域。 JVM屏蔽了与具体操作系统平台相关的信息,使Java程序只需生成在Java虚拟机上运行的目标代码(字节码),就可以在多种平台

- SQL中ON和WHERE的区别

avords

SQL中ON和WHERE的区别

数据库在通过连接两张或多张表来返回记录时,都会生成一张中间的临时表,然后再将这张临时表返回给用户。 www.2cto.com 在使用left jion时,on和where条件的区别如下: 1、 on条件是在生成临时表时使用的条件,它不管on中的条件是否为真,都会返回左边表中的记录。

- 说说自信

houxinyou

工作生活

自信的来源分为两种,一种是源于实力,一种源于头脑.实力是一个综合的评定,有自身的能力,能利用的资源等.比如我想去月亮上,要身体素质过硬,还要有飞船等等一系列的东西.这些都属于实力的一部分.而头脑不同,只要你头脑够简单就可以了!同样要上月亮上,你想,我一跳,1米,我多跳几下,跳个几年,应该就到了!什么?你说我会往下掉?你笨呀你!找个东西踩一下不就行了吗?

无论工作还

- WEBLOGIC事务超时设置

bijian1013

weblogicjta事务超时

系统中统计数据,由于调用统计过程,执行时间超过了weblogic设置的时间,提示如下错误:

统计数据出错!

原因:The transaction is no longer active - status: 'Rolling Back. [Reason=weblogic.transaction.internal

- 两年已过去,再看该如何快速融入新团队

bingyingao

java互联网融入架构新团队

偶得的空闲,翻到了两年前的帖子

该如何快速融入一个新团队,有所感触,就记下来,为下一个两年后的今天做参考。

时隔两年半之后的今天,再来看当初的这个博客,别有一番滋味。而我已经于今年三月份离开了当初所在的团队,加入另外的一个项目组,2011年的这篇博客之后的时光,我很好的融入了那个团队,而直到现在和同事们关系都特别好。大家在短短一年半的时间离一起经历了一

- 【Spark七十七】Spark分析Nginx和Apache的access.log

bit1129

apache

Spark分析Nginx和Apache的access.log,第一个问题是要对Nginx和Apache的access.log文件进行按行解析,按行解析就的方法是正则表达式:

Nginx的access.log解析正则表达式

val PATTERN = """([^ ]*) ([^ ]*) ([^ ]*) (\\[.*\\]) (\&q

- Erlang patch

bookjovi

erlang

Totally five patchs committed to erlang otp, just small patchs.

IMO, erlang really is a interesting programming language, I really like its concurrency feature.

but the functional programming style

- log4j日志路径中加入日期

bro_feng

javalog4j

要用log4j使用记录日志,日志路径有每日的日期,文件大小5M新增文件。

实现方式

log4j:

<appender name="serviceLog"

class="org.apache.log4j.RollingFileAppender">

<param name="Encoding" v

- 读《研磨设计模式》-代码笔记-桥接模式

bylijinnan

java设计模式

声明: 本文只为方便我个人查阅和理解,详细的分析以及源代码请移步 原作者的博客http://chjavach.iteye.com/

/**

* 个人觉得关于桥接模式的例子,蜡笔和毛笔这个例子是最贴切的:http://www.cnblogs.com/zhenyulu/articles/67016.html

* 笔和颜色是可分离的,蜡笔把两者耦合在一起了:一支蜡笔只有一种

- windows7下SVN和Eclipse插件安装

chenyu19891124

eclipse插件

今天花了一天时间弄SVN和Eclipse插件的安装,今天弄好了。svn插件和Eclipse整合有两种方式,一种是直接下载插件包,二种是通过Eclipse在线更新。由于之前Eclipse版本和svn插件版本有差别,始终是没装上。最后在网上找到了适合的版本。所用的环境系统:windows7JDK:1.7svn插件包版本:1.8.16Eclipse:3.7.2工具下载地址:Eclipse下在地址:htt

- [转帖]工作流引擎设计思路

comsci

设计模式工作应用服务器workflow企业应用

作为国内的同行,我非常希望在流程设计方面和大家交流,刚发现篇好文(那么好的文章,现在才发现,可惜),关于流程设计的一些原理,个人觉得本文站得高,看得远,比俺的文章有深度,转载如下

=================================================================================

自开博以来不断有朋友来探讨工作流引擎该如何

- Linux 查看内存,CPU及硬盘大小的方法

daizj

linuxcpu内存硬盘大小

一、查看CPU信息的命令

[root@R4 ~]# cat /proc/cpuinfo |grep "model name" && cat /proc/cpuinfo |grep "physical id"

model name : Intel(R) Xeon(R) CPU X5450 @ 3.00GHz

model name :

- linux 踢出在线用户

dongwei_6688

linux

两个步骤:

1.用w命令找到要踢出的用户,比如下面:

[root@localhost ~]# w

18:16:55 up 39 days, 8:27, 3 users, load average: 0.03, 0.03, 0.00

USER TTY FROM LOGIN@ IDLE JCPU PCPU WHAT

- 放手吧,就像不曾拥有过一样

dcj3sjt126com

内容提要:

静悠悠编著的《放手吧就像不曾拥有过一样》集结“全球华语世界最舒缓心灵”的精华故事,触碰生命最深层次的感动,献给全世界亿万读者。《放手吧就像不曾拥有过一样》的作者衷心地祝愿每一位读者都给自己一个重新出发的理由,将那些令你痛苦的、扛起的、背负的,一并都放下吧!把憔悴的面容换做一种清淡的微笑,把沉重的步伐调节成春天五线谱上的音符,让自己踏着轻快的节奏,在人生的海面上悠然漂荡,享受宁静与

- php二进制安全的含义

dcj3sjt126com

PHP

PHP里,有string的概念。

string里,每个字符的大小为byte(与PHP相比,Java的每个字符为Character,是UTF8字符,C语言的每个字符可以在编译时选择)。

byte里,有ASCII代码的字符,例如ABC,123,abc,也有一些特殊字符,例如回车,退格之类的。

特殊字符很多是不能显示的。或者说,他们的显示方式没有标准,例如编码65到哪儿都是字母A,编码97到哪儿都是字符

- Linux下禁用T440s,X240的一体化触摸板(touchpad)

gashero

linuxThinkPad触摸板

自打1月买了Thinkpad T440s就一直很火大,其中最让人恼火的莫过于触摸板。

Thinkpad的经典就包括用了小红点(TrackPoint)。但是小红点只能定位,还是需要鼠标的左右键的。但是自打T440s等开始启用了一体化触摸板,不再有实体的按键了。问题是要是好用也行。

实际使用中,触摸板一堆问题,比如定位有抖动,以及按键时会有飘逸。这就导致了单击经常就

- graph_dfs

hcx2013

Graph

package edu.xidian.graph;

class MyStack {

private final int SIZE = 20;

private int[] st;

private int top;

public MyStack() {

st = new int[SIZE];

top = -1;

}

public void push(i

- Spring4.1新特性——Spring核心部分及其他

jinnianshilongnian

spring 4.1

目录

Spring4.1新特性——综述

Spring4.1新特性——Spring核心部分及其他

Spring4.1新特性——Spring缓存框架增强

Spring4.1新特性——异步调用和事件机制的异常处理

Spring4.1新特性——数据库集成测试脚本初始化

Spring4.1新特性——Spring MVC增强

Spring4.1新特性——页面自动化测试框架Spring MVC T

- 配置HiveServer2的安全策略之自定义用户名密码验证

liyonghui160com

具体从网上看

http://doc.mapr.com/display/MapR/Using+HiveServer2#UsingHiveServer2-ConfiguringCustomAuthentication

LDAP Authentication using OpenLDAP

Setting

- 一位30多的程序员生涯经验总结

pda158

编程工作生活咨询

1.客户在接触到产品之后,才会真正明白自己的需求。

这是我在我的第一份工作上面学来的。只有当我们给客户展示产品的时候,他们才会意识到哪些是必须的。给出一个功能性原型设计远远比一张长长的文字表格要好。 2.只要有充足的时间,所有安全防御系统都将失败。

安全防御现如今是全世界都在关注的大课题、大挑战。我们必须时时刻刻积极完善它,因为黑客只要有一次成功,就可以彻底打败你。 3.

- 分布式web服务架构的演变

自由的奴隶

linuxWeb应用服务器互联网

最开始,由于某些想法,于是在互联网上搭建了一个网站,这个时候甚至有可能主机都是租借的,但由于这篇文章我们只关注架构的演变历程,因此就假设这个时候已经是托管了一台主机,并且有一定的带宽了,这个时候由于网站具备了一定的特色,吸引了部分人访问,逐渐你发现系统的压力越来越高,响应速度越来越慢,而这个时候比较明显的是数据库和应用互相影响,应用出问题了,数据库也很容易出现问题,而数据库出问题的时候,应用也容易

- 初探Druid连接池之二——慢SQL日志记录

xingsan_zhang

日志连接池druid慢SQL

由于工作原因,这里先不说连接数据库部分的配置,后面会补上,直接进入慢SQL日志记录。

1.applicationContext.xml中增加如下配置:

<bean abstract="true" id="mysql_database" class="com.alibaba.druid.pool.DruidDataSourc