【NVMe2.0b 4】Controller Property

Controller Registers

-

-

- 3.1.3Controller Properties

-

- 3.1.3.1Offset 0h: CAP – Controller Capabilities

- 3.1.3.2Offset 8h: VS – Version

-

- 3.1.3.2.1VS Value for 1.0 Compliant Controllers

- 3.1.3.2.2VS Value for 1.1 Compliant Controllers

- 3.1.3.2.3VS Value for 1.2 Compliant Controllers

- 3.1.3.2.5 VS Value for 1.3 Compliant Controllers

- 3.1.3.2.6VS Value for 1.4 Compliant Controllers

- 3.1.3.2.7VS Value for 2.0 Compliant Controllers

- 3.1.3.3Offset Ch: INTMS – Interrupt Mask Set

- 3.1.3.4Offset 10h: INTMC – Interrupt Mask Clear

- 3.1.3.5Offset 14h: CC – Controller Configuration

- 3.1.3.6Offset 1Ch: CSTS – Controller Status

- 3.1.3.7Offset 20h: NSSR – NVM Subsystem Reset

- 3.1.3.8Offset 24h: AQA – Admin Queue Attributes

- 3.1.3.9Offset 28h: ASQ – Admin Submission Queue Base Address

- 3.1.3.10Offset 30h: ACQ – Admin Completion Queue Base Address

- 3.1.3.11Offset 38h: CMBLOC – Controller Memory Buffer Location

- 3.1.3.12Offset 3Ch: CMBSZ – Controller Memory Buffer Size

- 3.1.3.13Offset 40h: BPINFO – Boot Partition Information

- 3.1.3.14Offset 44h: BPRSEL – Boot Partition Read Select

- 3.1.3.15Offset 48h: BPMBL – Boot Partition Memory Buffer Location (Optional)

- 3.1.3.16Offset 50h: CMBMSC – Controller Memory Buffer Memory Space Control

- 3.1.3.17Offset 58h: CMBSTS – Controller Memory Buffer Status

- 3.1.3.18Offset 5Ch: CMBEBS – Controller Memory Buffer Elasticity Buffer Size

- 3.1.3.19Offset 60h: CMBSWTP – Controller Memory Buffer Sustained Write Throughput

- 3.1.3.20Offset 64h: NSSD – NVM Subsystem Shutdown

- 3.1.3.21Offset 68h: CRTO – Controller Ready Timeouts

- 3.1.3.22Offset E00h: PMRCAP – Persistent Memory Region Capabilities

- 3.1.3.23Offset E04h: PMRCTL – Persistent Memory Region Control

- 3.1.3.24Offset E08h: PMRSTS – Persistent Memory Region Status

- 3.1.3.25Offset E0Ch: PMREBS – Persistent Memory Region Elasticity Buffer Size

- 3.1.3.26Offset E10h: PMRSWTP – Persistent Memory Region Sustained Write Throughput

- 3.1.3.27Offset E14h: PMRMSCL – Persistent Memory Region Memory Space Control Lower

- 3.1.3.28Offset E18h: PMRMSCU – Persistent Memory Region Memory Space Control Upper

-

3.1.3Controller Properties

Property(寄存器)是控制器的 dword 或 qword 属性。该属性可能具有读、写或读/写访问权限。除非在传输特定规范中另有说明,否则主机应使用为该寄存器指定的宽度和位于该寄存器开头的偏移量来访问该寄存器。所有reserved寄存器和寄存器中的所有reserved位都是只读的,读取时返回 0h。寄存器可以通过 Property Get 命令读取,使用基于消息传输模型的控制器通过 Property Set 命令写入。对于使用基于内存传输模型的控制器,请参阅适用的 NVMe Transport binding规范以了解访问方法和规则(例如,NVMe PCIe Transport Specification)。

Figure 35 描述了控制器的寄存器映射。

不支持以两个或多个寄存器的任何部分为目标的访问。

软件不应依赖于返回 0h。

以下约定用于描述所有传输模型的控制器寄存器。对于标记为reserved的所有位,硬件应返回“0”,主机软件应将所有reserved位和寄存器写入值 0h

使用以下术语和缩写:

RO Read Only

RW Read Write

RWC Read/Write ‘1’ to clear

RWS Read/Write ‘1’ to set

Impl Spec Implementation Specific – 控制器可以自由选择其实现。

HwInit 默认状态取决于 NVM Express 控制器和系统配置。

Reset 此列指示在第 3.7.2 节中定义的 Controller Level Reset 后的字段值。

对于某些字段,该字段是 RW、RWC 还是 RO 是特定实现的;通常显示为 RW/RO 或 RWC/RO,表示如果不支持该功能,则该字段是只读的。

当文档中引用字段时,使用的约定是“Property Symbol.Field Symbol”,即寄存器标签.字段标签。例如,PCI 命令寄存器 Parity Error Response Enable 位由名称 CMD.PEE 引用。如果该字段是位数组,则该字段被称为“Property Symbol.Field Symbol (数组到元素的偏移量)”。当文档中提到子字段时,使用的约定是“Property Symbol.Field Symbol.Sub Field Symbol”。例如,当 Controller Capability 属性内的 Controller Ready Modes Supported 字段的 Controller Ready With Media Support 子字段时,该子字段由名称 CAP.CRMS.CRWMS 引用。

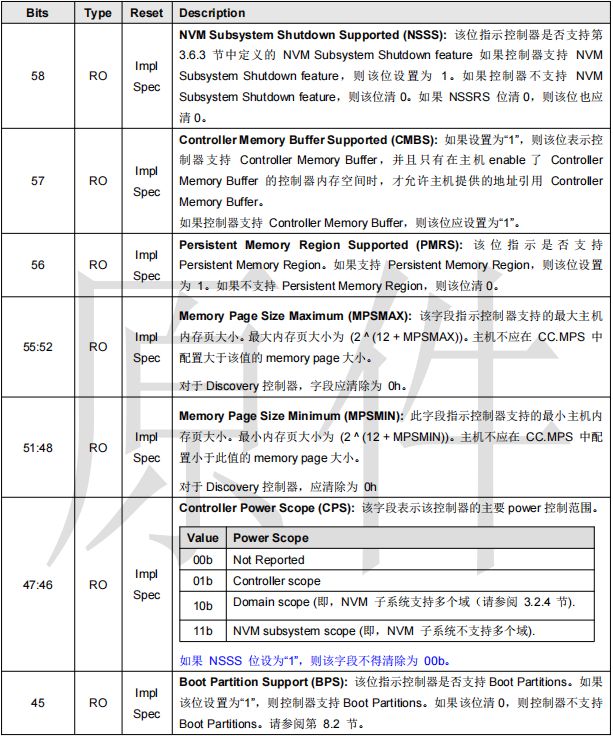

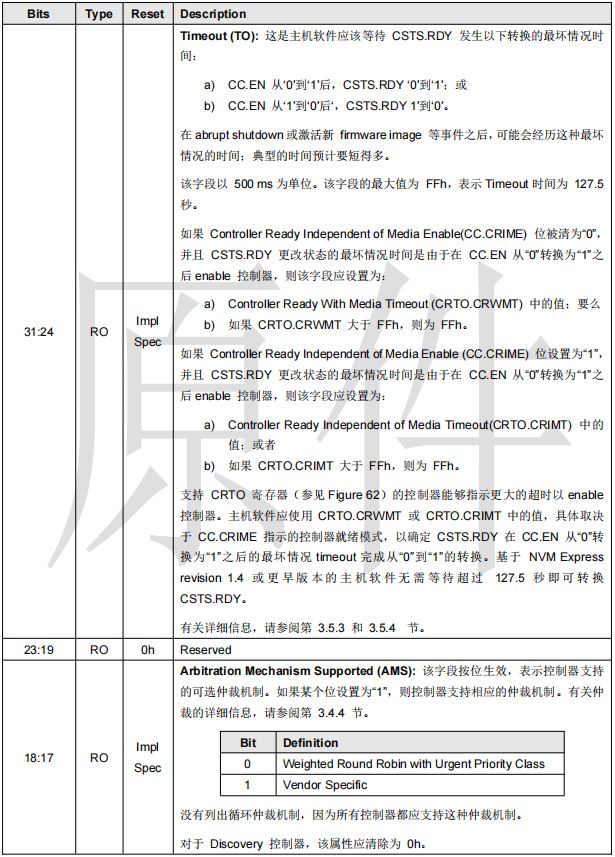

3.1.3.1Offset 0h: CAP – Controller Capabilities

此寄存器指示controller向host软件展示的基本capabilities。

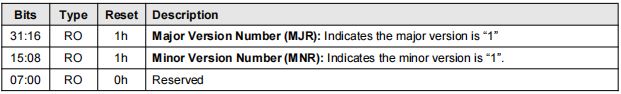

3.1.3.2Offset 8h: VS – Version

此寄存器指示控制器支持的 NVM Express 基本规范的主要、次要和第三版本。该规范的有效版本是:1.0、1.1、1.2、1.2.1、1.3、1.4 和 2.0。

3.1.3.2.1VS Value for 1.0 Compliant Controllers

3.1.3.2.2VS Value for 1.1 Compliant Controllers

3.1.3.2.3VS Value for 1.2 Compliant Controllers

3.1.3.2.5 VS Value for 1.3 Compliant Controllers

3.1.3.2.6VS Value for 1.4 Compliant Controllers

3.1.3.2.7VS Value for 2.0 Compliant Controllers

3.1.3.3Offset Ch: INTMS – Interrupt Mask Set

此寄存器用于在使用基于引脚的中断、单消息 MSI 或多消息 MSI 时屏蔽中断。使用 MSI-X 时,应使用定义为 MSI-X 一部分的中断屏蔽表来屏蔽中断。为 MSI-X 配置时,主机软件不应访问此寄存器;为 MSI-X 配置时的任何访问都是未定义的。有关中断行为要求,请参阅 NVMe over PCIe Transport Specification的Interrupts部分。

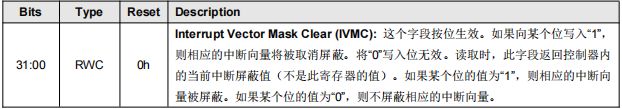

3.1.3.4Offset 10h: INTMC – Interrupt Mask Clear

此寄存器用于在使用基于引脚的中断、单消息 MSI 或多消息 MSI 时取消屏蔽中断。使用 MSI-X 时,应使用定义为 MSI-X 一部分的中断屏蔽表来取消屏蔽中断。为 MSI-X 配置时,主机软件不应访问此寄存器;为 MSI-X 配置时的任何访问都是未定义的。有关中断行为要求,请参阅 NVMe over PCIe Transport Specification 的Interrupts部分。

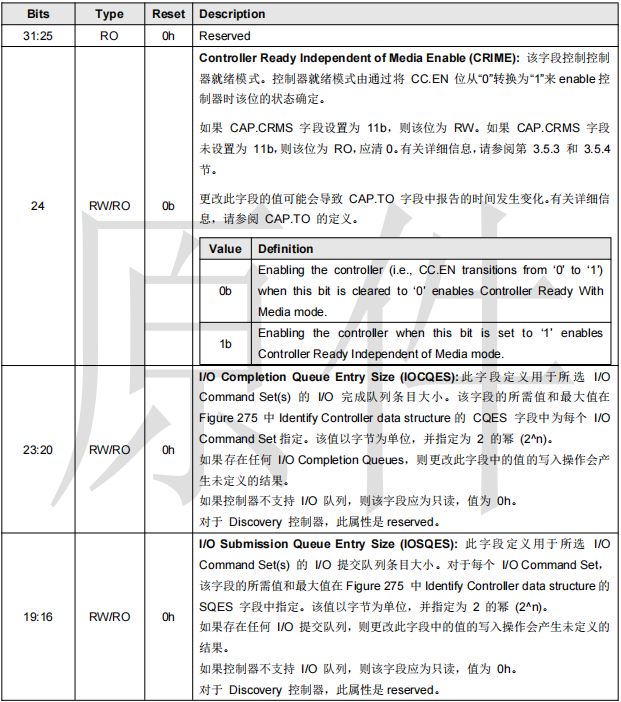

3.1.3.5Offset 14h: CC – Controller Configuration

此寄存器修改控制器的设置。在设置CC.EN enable控制器之前,主机软件应将Arbitration Mechanism Selected (CC.AMS)、 Memory Page Size (CC.MPS) 和I/O Command Set Selected (CC.CSS) 设置为有效值。在初始化 I/O Completion Queue Entry Size (CC.IOCQES) 和 I/O Submission Queue Entry Size(CC.IOSQES) 之前尝试创建 I/O 队列应该导致控制器中止创建 I/O Completion Queue 命令或 Create I/O Submission Queue 命令,状态代码为 Invalid Queue Size。

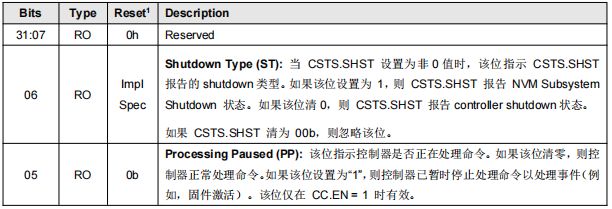

3.1.3.6Offset 1Ch: CSTS – Controller Status

3.1.3.7Offset 20h: NSSR – NVM Subsystem Reset

此可选寄存器为主机软件提供启动 NVM Subsystem Reset的capability。支持此寄存器的状态由 NVM Subsystem Reset Supported (CAP.NSSRS) 字段的状态指示。如果不支持该寄存器,则保留该寄存器占用的地址范围。请参阅第 3.7.1 节。

3.1.3.8Offset 24h: AQA – Admin Queue Attributes

此寄存器定义Admin Submission Queue和Admin Completion Queue的属性。Admin Submission Queue和Admin Completion Queue的Queue Identifier为 0h。Admin Submission Queue 的优先级由选择的仲裁机制决定,参见第 3.4.4 节。Admin Submission Queue和Admin Completion Queue必须在物理上连续的内存中。

注意:建议在boot操作期间使用 UEFI。在低内存环境(如旧版 BIOS 环境中的Option ROMs)中,可能没有足够的可用内存来分配必要的Submission和Completion Queues。在这些类型的条件下,控制器的低内存操作是供应商特定的。

3.1.3.9Offset 28h: ASQ – Admin Submission Queue Base Address

此寄存器定义 Admin Submission Queue 的 base memory address。

3.1.3.10Offset 30h: ACQ – Admin Completion Queue Base Address

此属性定义Admin Completion Queue的base memory address。

3.1.3.11Offset 38h: CMBLOC – Controller Memory Buffer Location

此可选寄存器定义Controller Memory Buffer的位置(请参阅第 8.1 节)。如果控制器不支持Controller Memory Buffer(CAP.CMBS),则保留此寄存器。如果控制器支持Controller Memory Buffer且 CMBMSC.CRE 清0,则该寄存器应清0。

3.1.3.12Offset 3Ch: CMBSZ – Controller Memory Buffer Size

此可选寄存器定义 Controller Memory Buffer 的大小(请参阅第 8.1 节)。如果控制器不支持 Controller Memory Buffer 功能,或者如果控制器支持 Controller Memory Buffer(CAP.CMBS) 并且 CMBMSC.CRE 清0,则该属性应清0。

3.1.3.13Offset 40h: BPINFO – Boot Partition Information

此可选寄存器定义 Boot Partitions 的特征(请参阅第 8.2 节)。如果控制器不支持Boot Partitions,则该属性应清除为 0h。

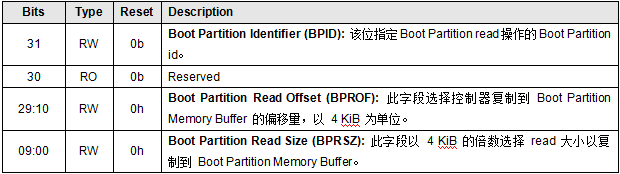

3.1.3.14Offset 44h: BPRSEL – Boot Partition Read Select

此可选寄存器用于启动 Boot Partition(请参阅第 8.2 节)中的数据从控制器到主机的传输。如果控制器不支持 Boot Partition 功能,则该属性应清除为 0h。

如果主机尝试读取超出 Boot Partition 的末尾(即Boot Partition Read Offset + Boot Partition Read Size,大于以字节为单位的 Boot Partition Size),则控制器不应传输数据并报告错误 BPINFO.BRS 字段。

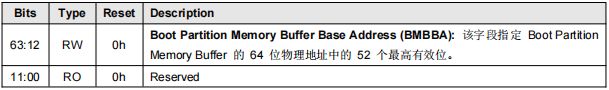

3.1.3.15Offset 48h: BPMBL – Boot Partition Memory Buffer Location (Optional)

此可选寄存器指定在读 Boot Partition 时用作数据目标的 memory buffer(请参阅第 8.2 节)。如果控制器不支持 Boot Partition 功能,则该属性应清除为 0h。

3.1.3.16Offset 50h: CMBMSC – Controller Memory Buffer Memory Space Control

此可选寄存器指定控制器如何使用主机提供的地址引用 Controller Memory Buffer。如果控制器支持 Controller Memory Buffer(CAP.CMBS),则此寄存器是强制的。否则,保留此寄存器。

此寄存器不应被 Controller Reset 或 Function Level Reset 重置,但应由所有其他 Controller Level Resets 重置。

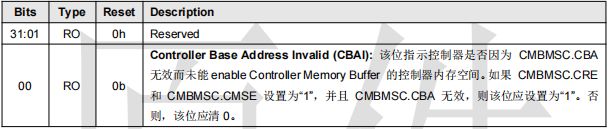

3.1.3.17Offset 58h: CMBSTS – Controller Memory Buffer Status

此可选寄存器指示 Controller Memory Buffer 的状态。如果控制器支持Controller Memory Buffer (CAP.CMBS),则此寄存器是强制的。否则,保留此寄存器。

3.1.3.18Offset 5Ch: CMBEBS – Controller Memory Buffer Elasticity Buffer Size

此可选寄存器向主机标识 CMB 弹性缓冲区的大小。此寄存器中的值 0h 向主机表明没有关于 CMB 弹性缓冲区的存在或大小信息可用。

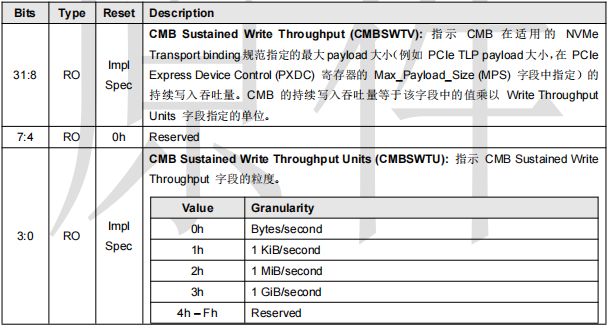

3.1.3.19Offset 60h: CMBSWTP – Controller Memory Buffer Sustained Write Throughput

此可选寄存器向主机标识最大 CMB 持续写入吞吐量。此属性中的值 0h 向主机表明没有关于 CMB 持续写入吞吐量的信息可用。

3.1.3.20Offset 64h: NSSD – NVM Subsystem Shutdown

此可选寄存器为主机软件提供启动normal或abrupt NVM subsystem shutdown的capability。 支持此寄存器的状态由 NVM Subsystem Shutdown Supported (CAP.NSSS) 字段的状态指示。如果不支持该寄存器,则保留寄存器占用的地址范围。

3.1.3.21Offset 68h: CRTO – Controller Ready Timeouts

此寄存器指示控制器就绪超时值。对于符合 NVM Express Base Specification revision 2.0 及更高版本的控制器,此寄存器是强制性的。

3.1.3.22Offset E00h: PMRCAP – Persistent Memory Region Capabilities

此寄存器指示 Persistent Memory Region的capabilities。如果控制器不支持 Persistent Memory Region 功能,则该属性应清除为 0h。

3.1.3.23Offset E04h: PMRCTL – Persistent Memory Region Control

此可选寄存器控制 Persistent Memory Region 的操作。如果控制器不支持 Persistent Memory Region 功能,则该寄存器应清除为 0h。

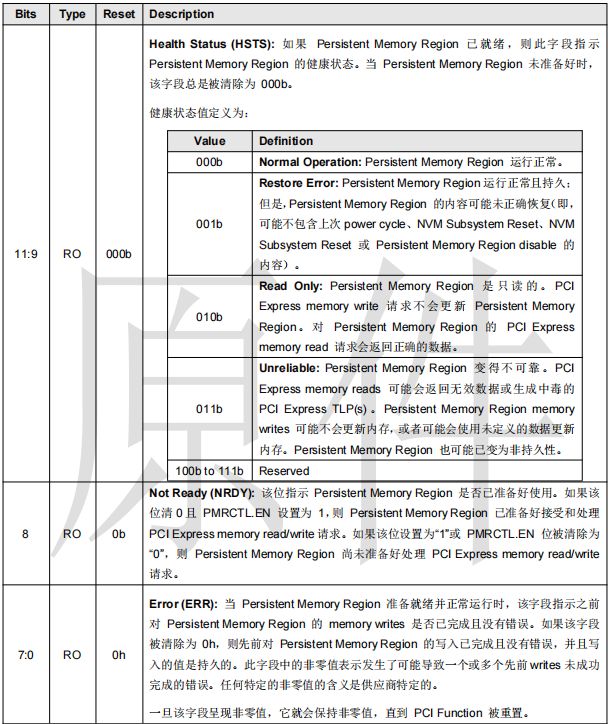

3.1.3.24Offset E08h: PMRSTS – Persistent Memory Region Status

此可选寄存器提供 Persistent Memory Region 的状态。如果控制器不支持 Persistent Memory Region 功能,则该寄存器应清除为 0h。

3.1.3.25Offset E0Ch: PMREBS – Persistent Memory Region Elasticity Buffer Size

此可选寄存器向主机标识 PMR 弹性缓冲区的大小。此属性中的值 0h 向主机表明没有关于 PMR 弹性缓冲区的存在或大小的信息可用。

3.1.3.26Offset E10h: PMRSWTP – Persistent Memory Region Sustained Write Throughput

此可选寄存器向主机标识最大 PMR 持续写入吞吐量。此属性中的值 0h 向主机表明没有关于 PMR 持续写入吞吐量的信息可用。

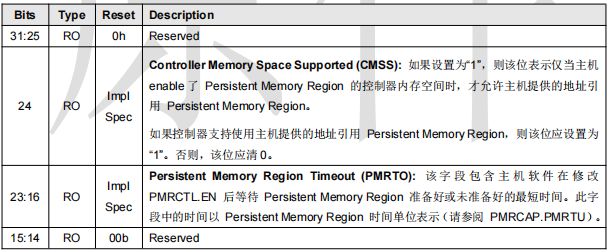

3.1.3.27Offset E14h: PMRMSCL – Persistent Memory Region Memory Space Control Lower

此可选寄存器和 PMRMSCU 寄存器指定控制器如何使用主机提供的地址引用 Persistent Memory Region。如果控制器支持 Persistent Memory Region 的 controller memory space (PMRCAP.CMSS),则此寄存器是强制的。否则,保留此寄存器。主机应使用对齐的 32 位访问来访问该寄存器。

此寄存器不应被 Controller Reset 重置。

3.1.3.28Offset E18h: PMRMSCU – Persistent Memory Region Memory Space Control Upper

此可选寄存器和 PMRMSCL 属性指定控制器如何使用主机提供的地址引用 Persistent Memory Region。如果控制器支持 Persistent Memory Region 的 controller memory space (PMRCAP.CMSS),则此寄存器是强制的。否则,保留此寄存器。主机应使用对齐的 32 位访问来访问该寄存器。

该寄存器不应被 Controller Reset 复位。