- HarmonyOS开发秘籍:从监听系统变量到掌握AbilityStage回调

大雨淅淅

#HarmonyOS开发harmonyos华为

目录一、HarmonyOS开发新视野二、AbilityStage组件初相识(一)组件定义与作用(二)与Module的对应关系三、开发前的准备工作(一)创建AbilityStage文件步骤(二)导入依赖与配置文件四、监听系统环境变量变化实战(一)关键代码解析(二)回调函数触发机制五、AbilityStage其他回调函数探秘(一)onAcceptWant()(二)onMemoryLevel()(三)o

- 鸿蒙(HarmonyOS)性能优化实战-启动分析工具Launch Profiler 学习指南

愿天堂没有996

HarmonyOS鸿蒙开发移动开发harmonyos性能优化HarmonyOSOpenHarmony移动开发

LaunchProfiler概述DevEcoStudio内置Profiler分析调优工具。其中Launch主要用于分析应用或服务的启动耗时,分析启动周期各阶段的耗时情况、核心线程的运行情况等,协助开发者识别启动缓慢的原因。此外,Launch任务窗口还集成了Time、CPU、Frame场景分析任务的功能,方便开发者在分析启动耗时的过程中同步对比同一时段的其他资源占用情况。场景示例如下代码在页面绘制之

- HarmonyOS 生命周期详解:用三张图彻底搞懂 UIAbility、页面与组件的生命周期

作者:像素笔记|发布时间:2025年6月27日摘要本文通过三层结构图、状态流程图、对比表格三大图表,深入解析HarmonyOSArkUI的生命周期机制,涵盖UIAbility、页面、组件各层级的触发顺序与最佳实践。同时提供高级场景管理方案、常见误区分析及实战级生命周期管理工具设计,助你打造高性能、高稳定性的HarmonyOS应用!一、三层生命周期结构图(图1)下图展示了HarmonyOS应用框架的

- .NET9 实现字符串拼接(StringConcatenation)性能测试

ChaITSimpleLove

.NET跨平台.netstring拼接字符串拼接性能测试BenchmarkTestcsharp

为了评估.NET9平台上使用C#中不同字符串拼接操作的性能表现,我们可以使用BenchmarkDotNet这一强大的开源库来构建科学且可重复的基准测试。BenchmarkDotNet能够自动处理诸如JIT编译、预热(Warm-up)、运行次数控制、统计误差分析等底层细节,确保测试结果具有高度准确性与可比性。在.NET9中,使用C#字符串拼接的常见方式包括:使用+运算符使用string.Concat

- HarmonyOS多语言支持:如何实现语言资源智能分发

操作系统内核探秘

操作系统内核揭秘harmonyos华为ai

HarmonyOS多语言支持:如何实现语言资源智能分发关键词:HarmonyOS、多语言支持、资源分发、智能调度、动态加载、国际化、本地化摘要:本文深入解析HarmonyOS多语言资源管理体系,系统阐述从基础架构设计到智能分发算法的核心技术。通过剖析资源目录结构、配置文件语法、动态加载机制等底层原理,结合自适应优先级调度算法和数学匹配模型,展示如何实现基于用户习惯、设备环境、区域特征的智能资源分发

- 深入解析HarmonyOS5 UIAbility组件:从核心架构到实战应用

颜颜yan_

架构harmonyos鸿蒙鸿蒙系统

⭐本期内容:深入解析HarmonyOS5UIAbility组件:从核心架构到实战应用系列专栏:鸿蒙HarmonyOS:探索未来智能生态新纪元文章目录前言核心定位架构特性分析系统调度的基本单元灵活的多实例架构实际应用场景——智能办公应用综合案例详细的架构设计思路解析总结前言在万物互联的智能时代,HarmonyOS作为面向全场景的分布式操作系统,其独特的架构设计为开发者提供了前所未有的开发体验。其中,

- OpenHarmony解读之设备认证:Pake协议详解与实战

陈乔布斯

鸿蒙开发HarmonyOSOpenHarmonyharmonyos分布式鸿蒙开发软总线openHarmony嵌入式硬件

往期推文全新看点(文中附带最新·鸿蒙全栈学习笔记)①鸿蒙应用开发与鸿蒙系统开发哪个更有前景?②嵌入式开发适不适合做鸿蒙南向开发?看完这篇你就了解了~③对于大前端开发来说,转鸿蒙开发究竟是福还是祸?④鸿蒙岗位需求突增!移动端、PC端、IoT到底该怎么选?⑤记录一场鸿蒙开发岗位面试经历~⑥持续更新中……一、概述在设备认证过程中,pake协议用于认证会话密钥协商,基于该会话密钥,双方可以安全地交换各自的

- JetBrains 2025 全家桶 11合1 Mac电脑

2501_92680691

intellij-ideajavamacospycharmdatagripwebstormphpstorm

JetBrains2025全家桶11合1Mac电脑,11个包含:IDEA、WebStorm、DataSpell、DataGrip、Pycharm、RustRover、CLion、Rider、PhpStorm、RubyMine、GoLand。原文地址:JetBrains2025全家桶11合1含IDEA、PyCharm、DataGrip、WebStrom、GoLand、CLion、PhpStorm、D

- 写测试太烦?Copilot + Jest 让你 3 分钟搞定单元测试

网罗开发(小红书、快手、视频号同名) 大家好,我是展菲,目前在上市企业从事人工智能项目研发管理工作,平时热衷于分享各种编程领域的软硬技能知识以及前沿技术,包括iOS、前端、HarmonyOS、Java、Python等方向。在移动端开发、鸿蒙开发、物联网、嵌入式、云原生、开源等领域有深厚造诣。图书作者:《ESP32-C3物联网工程开发实战》图书作者:《SwiftUI入门,进阶与实战》超级个体:CO

- 【优秀文章】7月优秀文章推荐

优秀文章智能自主运动体与人工智能技术——环境感知、SLAM定位、路径规划、运动控制、多智能体协同作者:fpga和matlabC++之红黑树认识与实现作者:zzh_zao【手把手带你刷好题】–C语言基础编程题(十)作者:草莓熊Lotso飞算JavaAI:从“码农”到“代码指挥官”的终极进化论作者:可涵不会debug前端网页开发学习(HTML+CSS+JS)有这一篇就够!作者:一颗小谷粒

- 交叉编译Python-3.6.0到aarch64/aarch32 —— 支持sqlite3

参考https://datko.net/2013/05/10/cross-compiling-python-3-3-1-for-beaglebone-arm-angstrom/平台主机:ubuntu14.0464bit开发板:qemu+aarch64(参考:http://www.cnblogs.com/pengdonglin137/p/6442583.html)工具链:aarch64-linux-

- HarmonyOS5.0仓颉引擎与盘古大模型:个性化作业批改系统架构设计与实现

H老师带你学鸿蒙

系统架构HarmonyOS5.0鸿蒙华为仓颉教育

人工智能与边缘计算的融合正在重塑教育评价体系。本文将展示如何基于HarmonyOS5.0仓颉并发引擎和盘古大模型,构建新一代智能作业批改系统。系统架构全景graphTDA[学生端设备]-->|提交作业|B[仓颉边缘处理]B-->C[盘古大模型分析]C-->D[个性化反馈生成]D-->E[学生终端]D-->F[教师仪表盘]subgraphHarmonyOS分布式系统B-->|设备协同|G[教室平板集

- 知识图谱的个性化智能教学推荐系统(论文+源码)

毕设工作室_wlzytw

python论文项目知识图谱人工智能

目录摘要Abstract目录第1章绪论1.1研究背景及意义1.2国内外研究现状1.2.1知识图谱1.2.2个性化推荐系统1.3本文研究内容及创新点1.4全文组织结构第2章相关理论与技术概述2.1知识图谱2.1.1知识图谱的介绍与发展2.1.2知识图谱的构建2.3协同过滤推荐算法2.2.1推荐算法概述2.2.2Pearson相关系数2.2.3Spearman相关系数2.4Bert模型和Albert模

- 【HarmonyOS】鸿蒙应用开发Text控件常见错误

【HarmonyOS】鸿蒙应用开发Text控件常见错误一、前言Text文本控件,是我们应用开发中最为基本和常见使用的控件之一。很多人觉得对于控件的使用已经非常熟悉,一个文本控件,能有什么使用错误呢?其实不然,今天本文,就对于Text常用会导致问题的点进行阐述。二、Text设置字体大小是否可用于百分号?对于初学者最常见的问题之一,就是使用Text的fontSize属性设置字体大小时,传入百分比字符串

- Linux 启动过程流程图--ARM版

进击的程序汪

linuxarm开发运维

以下是ARM版本Linux启动过程的超详细树状图,涵盖硬件上电到应用程序交互的全流程,并包含关键函数调用链及源码位置,适用于系统开发与调试场景:ARMLinux启动全流程(含函数调用链)ARMLinux启动流程(函数级调用链)│├───**1.硬件上电与BootROM阶段**│││├───硬件复位与初始化││├───CPU进入Reset异常向量(ARM异常向量表基址0x0或0xffff0000)│

- ARM SMMUv3故障和错误(五)

业余程序员plus

ARMv8-A架构SMMUFaultsErrorsSMMU_GERRORCMDQ_ERRFaultmodelsStallmodel

1.概述SMMU有三种方式将故障和错误(FaultsandErrors)报告给软件,具体如下:提交给SMMU命令在某些情况下不正确时,命令队列有机制报告这些错误。事件队列中记录了一些错误和故障。包括了来自设备流量(traffic)引起的错误和故障,比如配置错误或者设备地址引起的缺页异常。一种基于全局寄存器的SMMU_GERROR机制用于上报以下情况引发的事件:当无法将记录写入事件队列或PRI队列时

- ARMv8 创建3级页表示例

liuluyang530

FPGA验证ARMv8armv8页表mmu

最近在研究armv8页表创建过程,顺带做了一个如下形式的页表,//level1table,4entries://00000000-3FFFFFFF,1GBblock,DDR//40000000-7FFFFFFF,1GBblock,DDR//80000000-BFFFFFFF,1GBblock,DDR//C0000000-FFFFFFFF,pointtolevel2tabel////level2ta

- ARMv8 创建1、2、3级页表代码与注释

liuluyang530

armv8mmu页表

对下面的地址空间创建3级页表//level1table,4entries://00000000-3FFFFFFF,1GBblock,DDR//40000000-7FFFFFFF,1GBblock,DDR//80000000-BFFFFFFF,1GBblock,DDR//C0000000-FFFFFFFF,pointtolevel2tabel////level2table,512entries://

- STM32 开发笔记:从环境搭建到任务调度

嵌入式的小萌新

stm32笔记嵌入式硬件

今天体验了一把augment确实好用,记录一下STM32开发笔记:从环境搭建到任务调度️环境准备必需工具STM32CubeMX:图形化配置工具,用于初始化MCU外设和生成基础代码STM32CubeCLT:包含编译工具链(arm-none-eabi-gcc)和烧录工具(STM32_Programmer_CLI)CMake:跨平台构建系统,用于管理项目编译流程OpenOCD:开源调试器(可选,用于DA

- 60天python训练计划----day59

在之前的学习中,我们层层递进的介绍了时序模型的发展,从AR到MA到ARMA,再到ARIMA。本质就是把数据处理的操作和模型结合在一起了,实际上昨天提到的季节性差分也可以合并到模型中,让流程变得更加统一。季节性差分用S来表示,所以这个模型叫做SARIMA模型一、SARIMA模型SARIMA(SeasonalAutoRegressiveIntegratedMovingAverage)是标准ARIMA模

- 单片机:STM32F103的开发环境搭建

InnoLink_1024

单片机嵌入式单片机stm32嵌入式硬件

本文将详细介绍如何搭建STM32F103的开发环境。STM32F103是STMicroelectronics推出的一款基于ARMCortex-M3内核的32位微控制器(MCU),广泛应用于嵌入式开发。以下是搭建开发环境的详细步骤,涵盖硬件准备、软件安装、工具链配置及简单的开发示例。1.硬件准备在搭建STM32F103开发环境之前,需要准备以下硬件:STM32F103开发板:常见型号包括STM32F

- 单片机:STM32F103的架构

STM32F103是STMicroelectronics推出的一款基于ARMCortex-M3内核的32位微控制器(MCU),属于STM32F1系列,广泛应用于工业控制、汽车电子、消费电子等领域。以下是对STM32F103架构的详细介绍,涵盖其核心、存储器、总线、外设及关键特性,旨在提供全面且清晰的说明。1.总体架构概述STM32F103采用ARMCortex-M3内核,结合ST的定制化外设和存储

- FPGA的开发流程

InnoLink_1024

FPGARTL设计Verilogfpga开发

FPGA(现场可编程门阵列)的开发流程是一个系统化的过程,涉及从设计构思到最终硬件实现的多步骤工作。以下以XilinxKintex-7系列FPGA为例,详细介绍典型的FPGA开发流程,涵盖设计、实现、验证和部署等阶段,力求清晰、全面且简洁。FPGA开发流程概述FPGA开发流程通常包括以下主要阶段:需求分析与架构设计RTL设计(硬件描述语言编码)功能仿真综合(Synthesis)实现(Impleme

- 【Linux命令大全】Linux安全模块(LSM)终极指南:SELinux与AppArmor实战

【Linux命令大全】Linux安全模块(LSM)终极指南:SELinux与AppArmor实战安全警报:90%的Linux系统未正确配置强制访问控制!掌握这些技术可防御95%的提权攻击!本文包含100+策略案例,25张权限流程图,企业级安全方案全公开!前言:为什么LSM是系统安全的最后防线?在日益复杂的攻击环境下,我们面临的核心安全挑战:零日漏洞的应急防护容器逃逸攻击防御横向移动限制合规审计要求

- 基于STM32F103C8T6的超声波测距开发详解:从接线到精确测量的完整指南

快撑死的鱼

硬件算法实践stm32嵌入式硬件单片机

基于STM32F103C8T6的超声波测距开发详解:从接线到精确测量的完整指南引言超声波测距技术是一种基于超声波的传播时间来测量目标物体与传感器之间距离的技术。由于其测量精度高、成本低、易于实现,广泛应用于机器人避障、自动停车、液位测量等领域。STM32F103C8T6是一款基于ARMCortex-M3内核的高性能微控制器,凭借其丰富的外设和强大的处理能力,成为嵌入式开发中常用的选择。本文将通过一

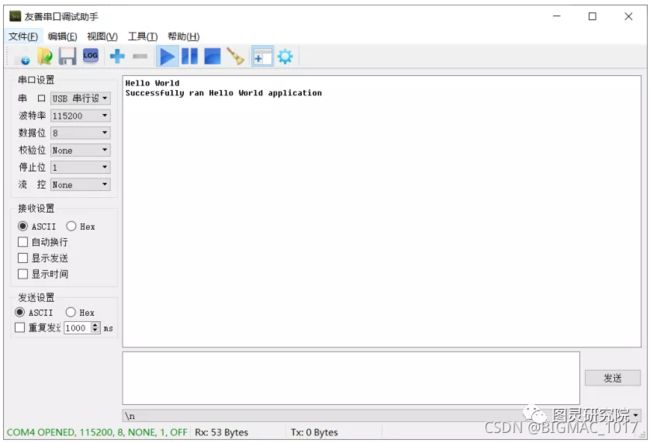

- HarmonyOS基础学习(一)

是隐墨啊啊

学习harmonyos

前言:这篇文章主要讲解一下我的初期HarmonyOS的学习所得和知识分享,并用一个简单的示例对所概括的知识点进行讲解,如果有什么内容问题或者错误请及时指出,感谢各位的阅读啦,跟着许小白的视角进入咱们的知识分享啦啦啦:一:引入的简单示例项目1.简单示例项目的要求:对于一个界面中类似于下面界面中,一个屏幕无法显示全部的内容,当你进行向上手滑的时候会自动加载后边的内容,不往下滑动的时候数据不进行加载,这

- Python与ESP32开发环境搭建详解

Despacito0o

ai语音助手python开发语言

Python与ESP32开发环境搭建详解一、前言大家好!今天给各位分享一篇超实用的开发环境配置教程,涵盖Python环境(PyCharm+Anaconda)和ESP32开发环境的完整搭建流程。无论你是新手还是老手,这篇教程都能帮你快速上手,避开各种配置陷阱。二、Python开发环境搭建2.1Anaconda安装Anaconda是Python最强大的包管理和环境管理工具之一,它可以让我们轻松创建独立

- 如何解决pip安装报错ModuleNotFoundError: No module named ‘os’问题

lyzybbs

全栈Bug解决方案专栏pippythonpycharm开发语言pandasnumpybeautifulsoup

【Python系列Bug修复PyCharm控制台pipinstall报错】如何解决pip安装报错ModuleNotFoundError:Nomodulenamed‘os’问题1.摘要在使用PyCharm2025的控制台执行pipinstall时,常常会遇到各种奇怪的安装失败或安装后仍然报ModuleNotFoundError的问题,例如“Nomodulenamed‘os’”。本文将从开发场景、环境

- 如何解决pip安装报错ModuleNotFoundError: No module named ‘sys’问题

lyzybbs

全栈Bug解决方案专栏pippycharmpythonpandasscrapybeautifulsoupmatplotlib

【Python系列Bug修复PyCharm控制台pipinstall报错】如何解决pip安装报错ModuleNotFoundError:Nomodulenamed‘sys’问题摘要在使用PyCharm内置终端或控制台执行pipinstallsys等命令时,常常会遇到如下异常:ModuleNotFoundError:Nomodulenamed‘sys’该错误看似与常驻Python核心库sys有关,但

- 鸿蒙设备开发OpenHarmony深度解读之设备认证:HiChain机制部分源码解析1(推荐模块之外)

往期推文全新看点(文中附带最新·鸿蒙全栈学习笔记)鸿蒙(HarmonyOS)北向开发知识点记录~鸿蒙(OpenHarmony)南向开发保姆级知识点汇总~鸿蒙应用开发与鸿蒙系统开发哪个更有前景?嵌入式开发适不适合做鸿蒙南向开发?看完这篇你就了解了~对于大前端开发来说,转鸿蒙开发究竟是福还是祸?鸿蒙岗位需求突增!移动端、PC端、IoT到底该怎么选?记录一场鸿蒙开发岗位面试经历~持续更新中……一、概述H

- C/C++Win32编程基础详解视频下载

择善Zach

编程C++Win32

课题视频:C/C++Win32编程基础详解

视频知识:win32窗口的创建

windows事件机制

主讲:择善Uncle老师

学习交流群:386620625

验证码:625

--

- Guava Cache使用笔记

bylijinnan

javaguavacache

1.Guava Cache的get/getIfPresent方法当参数为null时会抛空指针异常

我刚开始使用时还以为Guava Cache跟HashMap一样,get(null)返回null。

实际上Guava整体设计思想就是拒绝null的,很多地方都会执行com.google.common.base.Preconditions.checkNotNull的检查。

2.Guava

- 解决ora-01652无法通过128(在temp表空间中)

0624chenhong

oracle

解决ora-01652无法通过128(在temp表空间中)扩展temp段的过程

一个sql语句后,大约花了10分钟,好不容易有一个结果,但是报了一个ora-01652错误,查阅了oracle的错误代码说明:意思是指temp表空间无法自动扩展temp段。这种问题一般有两种原因:一是临时表空间空间太小,二是不能自动扩展。

分析过程:

既然是temp表空间有问题,那当

- Struct在jsp标签

不懂事的小屁孩

struct

非UI标签介绍:

控制类标签:

1:程序流程控制标签 if elseif else

<s:if test="isUsed">

<span class="label label-success">True</span>

</

- 按对象属性排序

换个号韩国红果果

JavaScript对象排序

利用JavaScript进行对象排序,根据用户的年龄排序展示

<script>

var bob={

name;bob,

age:30

}

var peter={

name;peter,

age:30

}

var amy={

name;amy,

age:24

}

var mike={

name;mike,

age:29

}

var john={

- 大数据分析让个性化的客户体验不再遥远

蓝儿唯美

数据分析

顾客通过多种渠道制造大量数据,企业则热衷于利用这些信息来实现更为个性化的体验。

分析公司Gartner表示,高级分析会成为客户服务的关键,但是大数据分析的采用目前仅局限于不到一成的企业。 挑战在于企业还在努力适应结构化数据,疲于根据自身的客户关系管理(CRM)系统部署有效的分析框架,以及集成不同的内外部信息源。

然而,面对顾客通过数字技术参与而产生的快速变化的信息,企业需要及时作出反应。要想实

- java笔记4

a-john

java

操作符

1,使用java操作符

操作符接受一个或多个参数,并生成一个新值。参数的形式与普通的方法调用不用,但是效果是相同的。加号和一元的正号(+)、减号和一元的负号(-)、乘号(*)、除号(/)以及赋值号(=)的用法与其他编程语言类似。

操作符作用于操作数,生成一个新值。另外,有些操作符可能会改变操作数自身的

- 从裸机编程到嵌入式Linux编程思想的转变------分而治之:驱动和应用程序

aijuans

嵌入式学习

笔者学习嵌入式Linux也有一段时间了,很奇怪的是很多书讲驱动编程方面的知识,也有很多书将ARM9方面的知识,但是从以前51形式的(对寄存器直接操作,初始化芯片的功能模块)编程方法,和思维模式,变换为基于Linux操作系统编程,讲这个思想转变的书几乎没有,让初学者走了很多弯路,撞了很多难墙。

笔者因此写上自己的学习心得,希望能给和我一样转变

- 在springmvc中解决FastJson循环引用的问题

asialee

循环引用fastjson

我们先来看一个例子:

package com.elong.bms;

import java.io.OutputStream;

import java.util.HashMap;

import java.util.Map;

import co

- ArrayAdapter和SimpleAdapter技术总结

百合不是茶

androidSimpleAdapterArrayAdapter高级组件基础

ArrayAdapter比较简单,但它只能用于显示文字。而SimpleAdapter则有很强的扩展性,可以自定义出各种效果

ArrayAdapter;的数据可以是数组或者是队列

// 获得下拉框对象

AutoCompleteTextView textview = (AutoCompleteTextView) this

- 九封信

bijian1013

人生励志

有时候,莫名的心情不好,不想和任何人说话,只想一个人静静的发呆。有时候,想一个人躲起来脆弱,不愿别人看到自己的伤口。有时候,走过熟悉的街角,看到熟悉的背影,突然想起一个人的脸。有时候,发现自己一夜之间就长大了。 2014,写给人

- Linux下安装MySQL Web 管理工具phpMyAdmin

sunjing

PHPInstallphpMyAdmin

PHP http://php.net/

phpMyAdmin http://www.phpmyadmin.net

Error compiling PHP on CentOS x64

一、安装Apache

请参阅http://billben.iteye.com/admin/blogs/1985244

二、安装依赖包

sudo yum install gd

- 分布式系统理论

bit1129

分布式

FLP

One famous theory in distributed computing, known as FLP after the authors Fischer, Lynch, and Patterson, proved that in a distributed system with asynchronous communication and process crashes,

- ssh2整合(spring+struts2+hibernate)-附源码

白糖_

eclipsespringHibernatemysql项目管理

最近抽空又整理了一套ssh2框架,主要使用的技术如下:

spring做容器,管理了三层(dao,service,actioin)的对象

struts2实现与页面交互(MVC),自己做了一个异常拦截器,能拦截Action层抛出的异常

hibernate与数据库交互

BoneCp数据库连接池,据说比其它数据库连接池快20倍,仅仅是据说

MySql数据库

项目用eclipse

- treetable bug记录

braveCS

table

// 插入子节点删除再插入时不能正常显示。修改:

//不知改后有没有错,先做个备忘

Tree.prototype.removeNode = function(node) {

// Recursively remove all descendants of +node+

this.unloadBranch(node);

// Remove

- 编程之美-电话号码对应英语单词

bylijinnan

java算法编程之美

import java.util.Arrays;

public class NumberToWord {

/**

* 编程之美 电话号码对应英语单词

* 题目:

* 手机上的拨号盘,每个数字都对应一些字母,比如2对应ABC,3对应DEF.........,8对应TUV,9对应WXYZ,

* 要求对一段数字,输出其代表的所有可能的字母组合

- jquery ajax读书笔记

chengxuyuancsdn

jQuery ajax

1、jsp页面

<%@ page language="java" import="java.util.*" pageEncoding="GBK"%>

<%

String path = request.getContextPath();

String basePath = request.getScheme()

- JWFD工作流拓扑结构解析伪码描述算法

comsci

数据结构算法工作活动J#

对工作流拓扑结构解析感兴趣的朋友可以下载附件,或者下载JWFD的全部代码进行分析

/* 流程图拓扑结构解析伪码描述算法

public java.util.ArrayList DFS(String graphid, String stepid, int j)

- oracle I/O 从属进程

daizj

oracle

I/O 从属进程

I/O从属进程用于为不支持异步I/O的系统或设备模拟异步I/O.例如,磁带设备(相当慢)就不支持异步I/O.通过使用I/O 从属进程,可以让磁带机模仿通常只为磁盘驱动器提供的功能。就好像支持真正的异步I/O 一样,写设备的进程(调用者)会收集大量数据,并交由写入器写出。数据成功地写出时,写入器(此时写入器是I/O 从属进程,而不是操作系统)会通知原来的调用者,调用者则会

- 高级排序:希尔排序

dieslrae

希尔排序

public void shellSort(int[] array){

int limit = 1;

int temp;

int index;

while(limit <= array.length/3){

limit = limit * 3 + 1;

- 初二下学期难记忆单词

dcj3sjt126com

englishword

kitchen 厨房

cupboard 厨柜

salt 盐

sugar 糖

oil 油

fork 叉;餐叉

spoon 匙;调羹

chopsticks 筷子

cabbage 卷心菜;洋白菜

soup 汤

Italian 意大利的

Indian 印度的

workplace 工作场所

even 甚至;更

Italy 意大利

laugh 笑

m

- Go语言使用MySQL数据库进行增删改查

dcj3sjt126com

mysql

目前Internet上流行的网站构架方式是LAMP,其中的M即MySQL, 作为数据库,MySQL以免费、开源、使用方便为优势成为了很多Web开发的后端数据库存储引擎。MySQL驱动Go中支持MySQL的驱动目前比较多,有如下几种,有些是支持database/sql标准,而有些是采用了自己的实现接口,常用的有如下几种:

http://code.google.c...o-mysql-dri

- git命令

shuizhaosi888

git

---------------设置全局用户名:

git config --global user.name "HanShuliang" //设置用户名

git config --global user.email "

[email protected]" //设置邮箱

---------------查看环境配置

git config --li

- qemu-kvm 网络 nat模式 (四)

haoningabc

kvmqemu

qemu-ifup-NAT

#!/bin/bash

BRIDGE=virbr0

NETWORK=192.168.122.0

GATEWAY=192.168.122.1

NETMASK=255.255.255.0

DHCPRANGE=192.168.122.2,192.168.122.254

TFTPROOT=

BOOTP=

function check_bridge()

- 不要让未来的你,讨厌现在的自己

jingjing0907

生活 奋斗 工作 梦想

故事one

23岁,他大学毕业,放弃了父母安排的稳定工作,独闯京城,在家小公司混个小职位,工作还算顺手,月薪三千,混了混,混走了一年的光阴。 24岁,有了女朋友,从二环12人的集体宿舍搬到香山民居,一间平房,二人世界,爱爱爱。偶然约三朋四友,打扑克搓麻将,日子快乐似神仙; 25岁,出了几次差,调了两次岗,薪水涨了不过百,生猛狂飙的物价让现实血淋淋,无力为心爱银儿购件大牌

- 枚举类型详解

一路欢笑一路走

enum枚举详解enumsetenumMap

枚举类型详解

一.Enum详解

1.1枚举类型的介绍

JDK1.5加入了一个全新的类型的”类”—枚举类型,为此JDK1.5引入了一个新的关键字enum,我们可以这样定义一个枚举类型。

Demo:一个最简单的枚举类

public enum ColorType {

RED

- 第11章 动画效果(上)

onestopweb

动画

index.html

<!DOCTYPE html PUBLIC "-//W3C//DTD XHTML 1.0 Transitional//EN" "http://www.w3.org/TR/xhtml1/DTD/xhtml1-transitional.dtd">

<html xmlns="http://www.w3.org/

- Eclipse中jsp、js文件编辑时,卡死现象解决汇总

ljf_home

eclipsejsp卡死js卡死

使用Eclipse编辑jsp、js文件时,经常出现卡死现象,在网上百度了N次,经过N次优化调整后,卡死现象逐步好转,具体那个方法起到作用,不太好讲。将所有用过的方法罗列如下:

1、取消验证

windows–>perferences–>validation

把 除了manual 下面的全部点掉,build下只留 classpath dependency Valida

- MySQL编程中的6个重要的实用技巧

tomcat_oracle

mysql

每一行命令都是用分号(;)作为结束

对于MySQL,第一件你必须牢记的是它的每一行命令都是用分号(;)作为结束的,但当一行MySQL被插入在PHP代码中时,最好把后面的分号省略掉,例如:

mysql_query("INSERT INTO tablename(first_name,last_name)VALUES('$first_name',$last_name')");

- zoj 3820 Building Fire Stations(二分+bfs)

阿尔萨斯

Build

题目链接:zoj 3820 Building Fire Stations

题目大意:给定一棵树,选取两个建立加油站,问说所有点距离加油站距离的最大值的最小值是多少,并且任意输出一种建立加油站的方式。

解题思路:二分距离判断,判断函数的复杂度是o(n),这样的复杂度应该是o(nlogn),即使常数系数偏大,但是居然跑了4.5s,也是醉了。 判断函数里面做了3次bfs,但是每次bfs节点最多