Rockchip RK3588 kernel dts解析之显示模块

Rockchip RK3588 kernel dts解析之显示模块

文章目录

- Rockchip RK3588 kernel dts解析之显示模块

-

- RK3588 显示模块介绍

-

- RK3588 的VOP (video output process)分为4个Port

- 支持8个图层,每个图层可以灵活分配到每个Video Port上

- RK3588 支持的显示接口

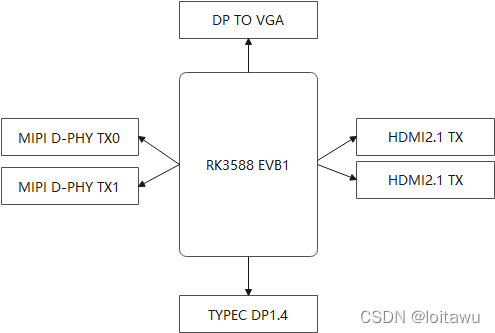

- RK3588 开发板EVB1的显示部分硬件设计

- 显示模块的DTS配置

-

- VOP的配置

- 显示接口配置

-

- HDMI

- MIPI DSI

- DP TO VGA

- TYPEC DP

RK3588 显示模块介绍

RK3588 的VOP (video output process)分为4个Port

| port | 分辨率 |

|---|---|

| VP0 | 4K |

| VP1 | 4K |

| VP2 | 4K |

| VP3 | 1080P |

支持8个图层,每个图层可以灵活分配到每个Video Port上

RK3588 支持的显示接口

- 2个DP

- 2个HDMI/eDP 共用接口

- 2个MIPI DSI

- BT656/BT1120

RK3588 开发板EVB1的显示部分硬件设计

显示模块的DTS配置

VOP的配置

arch/arm64/boot/dts/rockchip/rk3588-evb.dtsi

//开启VOP,必须配置

&vop {

status = "okay";

};

&vop_mmu {

status = "okay";

};

//配置VP的图层,这里配置为每个port分别配置2个图层,这里可以根据需求配置,可以把vp0和vp1合并来支持8K显示需求

/* vp0 & vp1 splice for 8K output */

&vp0 {

rockchip,plane-mask = <(1 << ROCKCHIP_VOP2_CLUSTER0 | 1 << ROCKCHIP_VOP2_ESMART0)>;

rockchip,primary-plane = ;

};

&vp1 {

rockchip,plane-mask = <(1 << ROCKCHIP_VOP2_CLUSTER1 | 1 << ROCKCHIP_VOP2_ESMART1)>;

rockchip,primary-plane = ;

};

&vp2 {

rockchip,plane-mask = <(1 << ROCKCHIP_VOP2_CLUSTER2 | 1 << ROCKCHIP_VOP2_ESMART2)>;

rockchip,primary-plane = ;

};

&vp3 {

rockchip,plane-mask = <(1 << ROCKCHIP_VOP2_CLUSTER3 | 1 << ROCKCHIP_VOP2_ESMART3)>;

rockchip,primary-plane = ;

};

显示接口配置

HDMI

arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

//使能HDMI0

&hdmi0 {

enable-gpios = <&gpio4 RK_PB1 GPIO_ACTIVE_HIGH>;

status = "okay";

};

//配置HDMI0到VP0上面

&hdmi0_in_vp0 {

status = "okay";

};

//打开HDMI0 声音

&hdmi0_sound {

status = "okay";

};

//配置HDMI0上面显示开机logo

&route_hdmi0 {

status = "okay";

};

//使能HDMI1

&hdmi1 {

enable-gpios = <&gpio4 RK_PB2 GPIO_ACTIVE_HIGH>;

status = "okay";

};

//配置HDMI1到VP1上面

&hdmi1_in_vp1 {

status = "okay";

};

//打开HDMI1 声音

&hdmi1_sound {

status = "okay";

};

//配置HDMI1上面显示开机logo

&route_hdmi1 {

status = "okay";

};

MIPI DSI

arch/arm64/boot/dts/rockchip/rk3588-evb.dtsi

//配置背光,这里主要配置背光使用的pwm口

&backlight {

pwms = <&pwm2 0 25000 0>;

status = "okay";

};

//dsi0接口的mipi屏配置

&dsi0 {

status = "disabled"; //这里默认是disabled,在下一级的rk3588-evb1-lp4.dtsi里面开启,根据实际硬件配置来确认是否打开

//rockchip,lane-rate = <1000>;

//配置mipi屏的参数

dsi0_panel: panel@0 {

status = "okay";

compatible = "simple-panel-dsi";

reg = <0>;

backlight = <&backlight>;

reset-delay-ms = <10>;

enable-delay-ms = <10>;

prepare-delay-ms = <10>;

unprepare-delay-ms = <10>;

disable-delay-ms = <60>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;

dsi,format = ;

dsi,lanes = <4>;

panel-init-sequence = [

23 00 02 FE 21

23 00 02 04 00

23 00 02 00 64

23 00 02 2A 00

23 00 02 26 64

23 00 02 54 00

23 00 02 50 64

23 00 02 7B 00

23 00 02 77 64

23 00 02 A2 00

23 00 02 9D 64

23 00 02 C9 00

23 00 02 C5 64

23 00 02 01 71

23 00 02 27 71

23 00 02 51 71

23 00 02 78 71

23 00 02 9E 71

23 00 02 C6 71

23 00 02 02 89

23 00 02 28 89

23 00 02 52 89

23 00 02 79 89

23 00 02 9F 89

23 00 02 C7 89

23 00 02 03 9E

23 00 02 29 9E

23 00 02 53 9E

23 00 02 7A 9E

23 00 02 A0 9E

23 00 02 C8 9E

23 00 02 09 00

23 00 02 05 B0

23 00 02 31 00

23 00 02 2B B0

23 00 02 5A 00

23 00 02 55 B0

23 00 02 80 00

23 00 02 7C B0

23 00 02 A7 00

23 00 02 A3 B0

23 00 02 CE 00

23 00 02 CA B0

23 00 02 06 C0

23 00 02 2D C0

23 00 02 56 C0

23 00 02 7D C0

23 00 02 A4 C0

23 00 02 CB C0

23 00 02 07 CF

23 00 02 2F CF

23 00 02 58 CF

23 00 02 7E CF

23 00 02 A5 CF

23 00 02 CC CF

23 00 02 08 DD

23 00 02 30 DD

23 00 02 59 DD

23 00 02 7F DD

23 00 02 A6 DD

23 00 02 CD DD

23 00 02 0E 15

23 00 02 0A E9

23 00 02 36 15

23 00 02 32 E9

23 00 02 5F 15

23 00 02 5B E9

23 00 02 85 15

23 00 02 81 E9

23 00 02 AD 15

23 00 02 A9 E9

23 00 02 D3 15

23 00 02 CF E9

23 00 02 0B 14

23 00 02 33 14

23 00 02 5C 14

23 00 02 82 14

23 00 02 AA 14

23 00 02 D0 14

23 00 02 0C 36

23 00 02 34 36

23 00 02 5D 36

23 00 02 83 36

23 00 02 AB 36

23 00 02 D1 36

23 00 02 0D 6B

23 00 02 35 6B

23 00 02 5E 6B

23 00 02 84 6B

23 00 02 AC 6B

23 00 02 D2 6B

23 00 02 13 5A

23 00 02 0F 94

23 00 02 3B 5A

23 00 02 37 94

23 00 02 64 5A

23 00 02 60 94

23 00 02 8A 5A

23 00 02 86 94

23 00 02 B2 5A

23 00 02 AE 94

23 00 02 D8 5A

23 00 02 D4 94

23 00 02 10 D1

23 00 02 38 D1

23 00 02 61 D1

23 00 02 87 D1

23 00 02 AF D1

23 00 02 D5 D1

23 00 02 11 04

23 00 02 39 04

23 00 02 62 04

23 00 02 88 04

23 00 02 B0 04

23 00 02 D6 04

23 00 02 12 05

23 00 02 3A 05

23 00 02 63 05

23 00 02 89 05

23 00 02 B1 05

23 00 02 D7 05

23 00 02 18 AA

23 00 02 14 36

23 00 02 42 AA

23 00 02 3D 36

23 00 02 69 AA

23 00 02 65 36

23 00 02 8F AA

23 00 02 8B 36

23 00 02 B7 AA

23 00 02 B3 36

23 00 02 DD AA

23 00 02 D9 36

23 00 02 15 74

23 00 02 3F 74

23 00 02 66 74

23 00 02 8C 74

23 00 02 B4 74

23 00 02 DA 74

23 00 02 16 9F

23 00 02 40 9F

23 00 02 67 9F

23 00 02 8D 9F

23 00 02 B5 9F

23 00 02 DB 9F

23 00 02 17 DC

23 00 02 41 DC

23 00 02 68 DC

23 00 02 8E DC

23 00 02 B6 DC

23 00 02 DC DC

23 00 02 1D FF

23 00 02 19 03

23 00 02 47 FF

23 00 02 43 03

23 00 02 6E FF

23 00 02 6A 03

23 00 02 94 FF

23 00 02 90 03

23 00 02 BC FF

23 00 02 B8 03

23 00 02 E2 FF

23 00 02 DE 03

23 00 02 1A 35

23 00 02 44 35

23 00 02 6B 35

23 00 02 91 35

23 00 02 B9 35

23 00 02 DF 35

23 00 02 1B 45

23 00 02 45 45

23 00 02 6C 45

23 00 02 92 45

23 00 02 BA 45

23 00 02 E0 45

23 00 02 1C 55

23 00 02 46 55

23 00 02 6D 55

23 00 02 93 55

23 00 02 BB 55

23 00 02 E1 55

23 00 02 22 FF

23 00 02 1E 68

23 00 02 4C FF

23 00 02 48 68

23 00 02 73 FF

23 00 02 6F 68

23 00 02 99 FF

23 00 02 95 68

23 00 02 C1 FF

23 00 02 BD 68

23 00 02 E7 FF

23 00 02 E3 68

23 00 02 1F 7E

23 00 02 49 7E

23 00 02 70 7E

23 00 02 96 7E

23 00 02 BE 7E

23 00 02 E4 7E

23 00 02 20 97

23 00 02 4A 97

23 00 02 71 97

23 00 02 97 97

23 00 02 BF 97

23 00 02 E5 97

23 00 02 21 B5

23 00 02 4B B5

23 00 02 72 B5

23 00 02 98 B5

23 00 02 C0 B5

23 00 02 E6 B5

23 00 02 25 F0

23 00 02 23 E8

23 00 02 4F F0

23 00 02 4D E8

23 00 02 76 F0

23 00 02 74 E8

23 00 02 9C F0

23 00 02 9A E8

23 00 02 C4 F0

23 00 02 C2 E8

23 00 02 EA F0

23 00 02 E8 E8

23 00 02 24 FF

23 00 02 4E FF

23 00 02 75 FF

23 00 02 9B FF

23 00 02 C3 FF

23 00 02 E9 FF

23 00 02 FE 3D

23 00 02 00 04

23 00 02 FE 23

23 00 02 08 82

23 00 02 0A 00

23 00 02 0B 00

23 00 02 0C 01

23 00 02 16 00

23 00 02 18 02

23 00 02 1B 04

23 00 02 19 04

23 00 02 1C 81

23 00 02 1F 00

23 00 02 20 03

23 00 02 23 04

23 00 02 21 01

23 00 02 54 63

23 00 02 55 54

23 00 02 6E 45

23 00 02 6D 36

23 00 02 FE 3D

23 00 02 55 78

23 00 02 FE 20

23 00 02 26 30

23 00 02 FE 3D

23 00 02 20 71

23 00 02 50 8F

23 00 02 51 8F

23 00 02 FE 00

23 00 02 35 00

05 78 01 11

05 00 01 29

];

panel-exit-sequence = [

05 00 01 28

05 00 01 10

];

disp_timings0: display-timings {

native-mode = <&dsi0_timing0>;

dsi0_timing0: timing0 {

clock-frequency = <132000000>;

hactive = <1080>;

vactive = <1920>;

hfront-porch = <15>;

hsync-len = <4>;

hback-porch = <30>;

vfront-porch = <15>;

vsync-len = <2>;

vback-porch = <15>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_in_dsi: endpoint {

remote-endpoint = <&dsi_out_panel>;

};

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

dsi_out_panel: endpoint {

remote-endpoint = <&panel_in_dsi>;

};

};

};

};

//dsi1接口的mipi屏配置

&dsi1 {

status = "disabled";//这里默认是disabled,根据实际硬件配置来确认是否打开

//rockchip,lane-rate = <1000>;

//配置mipi屏的参数

dsi1_panel: panel@0 {

status = "okay";

compatible = "simple-panel-dsi";

reg = <0>;

backlight = <&backlight>;

reset-delay-ms = <10>;

enable-delay-ms = <10>;

prepare-delay-ms = <10>;

unprepare-delay-ms = <10>;

disable-delay-ms = <10>;

dsi,flags = <(MIPI_DSI_MODE_VIDEO | MIPI_DSI_MODE_VIDEO_BURST |

MIPI_DSI_MODE_LPM | MIPI_DSI_MODE_EOT_PACKET)>;

dsi,format = ;

dsi,lanes = <4>;

panel-init-sequence = [

23 00 02 FE 21

23 00 02 04 00

23 00 02 00 64

23 00 02 2A 00

23 00 02 26 64

23 00 02 54 00

23 00 02 50 64

23 00 02 7B 00

23 00 02 77 64

23 00 02 A2 00

23 00 02 9D 64

23 00 02 C9 00

23 00 02 C5 64

23 00 02 01 71

23 00 02 27 71

23 00 02 51 71

23 00 02 78 71

23 00 02 9E 71

23 00 02 C6 71

23 00 02 02 89

23 00 02 28 89

23 00 02 52 89

23 00 02 79 89

23 00 02 9F 89

23 00 02 C7 89

23 00 02 03 9E

23 00 02 29 9E

23 00 02 53 9E

23 00 02 7A 9E

23 00 02 A0 9E

23 00 02 C8 9E

23 00 02 09 00

23 00 02 05 B0

23 00 02 31 00

23 00 02 2B B0

23 00 02 5A 00

23 00 02 55 B0

23 00 02 80 00

23 00 02 7C B0

23 00 02 A7 00

23 00 02 A3 B0

23 00 02 CE 00

23 00 02 CA B0

23 00 02 06 C0

23 00 02 2D C0

23 00 02 56 C0

23 00 02 7D C0

23 00 02 A4 C0

23 00 02 CB C0

23 00 02 07 CF

23 00 02 2F CF

23 00 02 58 CF

23 00 02 7E CF

23 00 02 A5 CF

23 00 02 CC CF

23 00 02 08 DD

23 00 02 30 DD

23 00 02 59 DD

23 00 02 7F DD

23 00 02 A6 DD

23 00 02 CD DD

23 00 02 0E 15

23 00 02 0A E9

23 00 02 36 15

23 00 02 32 E9

23 00 02 5F 15

23 00 02 5B E9

23 00 02 85 15

23 00 02 81 E9

23 00 02 AD 15

23 00 02 A9 E9

23 00 02 D3 15

23 00 02 CF E9

23 00 02 0B 14

23 00 02 33 14

23 00 02 5C 14

23 00 02 82 14

23 00 02 AA 14

23 00 02 D0 14

23 00 02 0C 36

23 00 02 34 36

23 00 02 5D 36

23 00 02 83 36

23 00 02 AB 36

23 00 02 D1 36

23 00 02 0D 6B

23 00 02 35 6B

23 00 02 5E 6B

23 00 02 84 6B

23 00 02 AC 6B

23 00 02 D2 6B

23 00 02 13 5A

23 00 02 0F 94

23 00 02 3B 5A

23 00 02 37 94

23 00 02 64 5A

23 00 02 60 94

23 00 02 8A 5A

23 00 02 86 94

23 00 02 B2 5A

23 00 02 AE 94

23 00 02 D8 5A

23 00 02 D4 94

23 00 02 10 D1

23 00 02 38 D1

23 00 02 61 D1

23 00 02 87 D1

23 00 02 AF D1

23 00 02 D5 D1

23 00 02 11 04

23 00 02 39 04

23 00 02 62 04

23 00 02 88 04

23 00 02 B0 04

23 00 02 D6 04

23 00 02 12 05

23 00 02 3A 05

23 00 02 63 05

23 00 02 89 05

23 00 02 B1 05

23 00 02 D7 05

23 00 02 18 AA

23 00 02 14 36

23 00 02 42 AA

23 00 02 3D 36

23 00 02 69 AA

23 00 02 65 36

23 00 02 8F AA

23 00 02 8B 36

23 00 02 B7 AA

23 00 02 B3 36

23 00 02 DD AA

23 00 02 D9 36

23 00 02 15 74

23 00 02 3F 74

23 00 02 66 74

23 00 02 8C 74

23 00 02 B4 74

23 00 02 DA 74

23 00 02 16 9F

23 00 02 40 9F

23 00 02 67 9F

23 00 02 8D 9F

23 00 02 B5 9F

23 00 02 DB 9F

23 00 02 17 DC

23 00 02 41 DC

23 00 02 68 DC

23 00 02 8E DC

23 00 02 B6 DC

23 00 02 DC DC

23 00 02 1D FF

23 00 02 19 03

23 00 02 47 FF

23 00 02 43 03

23 00 02 6E FF

23 00 02 6A 03

23 00 02 94 FF

23 00 02 90 03

23 00 02 BC FF

23 00 02 B8 03

23 00 02 E2 FF

23 00 02 DE 03

23 00 02 1A 35

23 00 02 44 35

23 00 02 6B 35

23 00 02 91 35

23 00 02 B9 35

23 00 02 DF 35

23 00 02 1B 45

23 00 02 45 45

23 00 02 6C 45

23 00 02 92 45

23 00 02 BA 45

23 00 02 E0 45

23 00 02 1C 55

23 00 02 46 55

23 00 02 6D 55

23 00 02 93 55

23 00 02 BB 55

23 00 02 E1 55

23 00 02 22 FF

23 00 02 1E 68

23 00 02 4C FF

23 00 02 48 68

23 00 02 73 FF

23 00 02 6F 68

23 00 02 99 FF

23 00 02 95 68

23 00 02 C1 FF

23 00 02 BD 68

23 00 02 E7 FF

23 00 02 E3 68

23 00 02 1F 7E

23 00 02 49 7E

23 00 02 70 7E

23 00 02 96 7E

23 00 02 BE 7E

23 00 02 E4 7E

23 00 02 20 97

23 00 02 4A 97

23 00 02 71 97

23 00 02 97 97

23 00 02 BF 97

23 00 02 E5 97

23 00 02 21 B5

23 00 02 4B B5

23 00 02 72 B5

23 00 02 98 B5

23 00 02 C0 B5

23 00 02 E6 B5

23 00 02 25 F0

23 00 02 23 E8

23 00 02 4F F0

23 00 02 4D E8

23 00 02 76 F0

23 00 02 74 E8

23 00 02 9C F0

23 00 02 9A E8

23 00 02 C4 F0

23 00 02 C2 E8

23 00 02 EA F0

23 00 02 E8 E8

23 00 02 24 FF

23 00 02 4E FF

23 00 02 75 FF

23 00 02 9B FF

23 00 02 C3 FF

23 00 02 E9 FF

23 00 02 FE 3D

23 00 02 00 04

23 00 02 FE 23

23 00 02 08 82

23 00 02 0A 00

23 00 02 0B 00

23 00 02 0C 01

23 00 02 16 00

23 00 02 18 02

23 00 02 1B 04

23 00 02 19 04

23 00 02 1C 81

23 00 02 1F 00

23 00 02 20 03

23 00 02 23 04

23 00 02 21 01

23 00 02 54 63

23 00 02 55 54

23 00 02 6E 45

23 00 02 6D 36

23 00 02 FE 3D

23 00 02 55 78

23 00 02 FE 20

23 00 02 26 30

23 00 02 FE 3D

23 00 02 20 71

23 00 02 50 8F

23 00 02 51 8F

23 00 02 FE 00

23 00 02 35 00

05 78 01 11

05 00 01 29

];

panel-exit-sequence = [

05 00 01 28

05 00 01 10

];

disp_timings1: display-timings {

native-mode = <&dsi1_timing0>;

dsi1_timing0: timing0 {

clock-frequency = <132000000>;

hactive = <1080>;

vactive = <1920>;

hfront-porch = <15>;

hsync-len = <4>;

hback-porch = <30>;

vfront-porch = <15>;

vsync-len = <2>;

vback-porch = <15>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

panel_in_dsi1: endpoint {

remote-endpoint = <&dsi1_out_panel>;

};

};

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@1 {

reg = <1>;

dsi1_out_panel: endpoint {

remote-endpoint = <&panel_in_dsi1>;

};

};

};

};

arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

/*

* mipi_dcphy0 needs to be enabled

* when dsi0 is enabled

*/

//evb1在dsi0上接了一个mipi屏,这个配置开启dsi0

&dsi0 {

status = "okay";

};

//默认dsi配置vp2和vp3上面,这里配置为dsi使用vp3,可以根据屏的分辨率来确认使用vp2还是vp3,vp2支持4K,vp3只支持 2048x1536

&dsi0_in_vp2 {

status = "disabled";

};

&dsi0_in_vp3 {

status = "okay";

};

//配置屏的电源和控制脚

&dsi0_panel {

power-supply = <&vcc3v3_lcd_n>; //使用gpio模拟regulator

reset-gpios = <&gpio2 RK_PB4 GPIO_ACTIVE_LOW>;

pinctrl-names = "default";

pinctrl-0 = <&lcd_rst_gpio>;

};

//配置dsi0显示开机logo

&route_dsi0 {

status = "okay";

connect = <&vp3_out_dsi0>;

};

//dsi1的屏配置,与dsi0相同,根据实际需求配置

/*

* mipi_dcphy1 needs to be enabled

* when dsi1 is enabled

*/

&dsi1 {

status = "disabled";

};

&dsi1_in_vp2 {

status = "disabled";

};

&dsi1_in_vp3 {

status = "disabled";

};

&dsi1_panel {

power-supply = <&vcc3v3_lcd_n>;

/*

* because in hardware, the two screens share the reset pin,

* so reset-gpios need only in dsi1 enable and dsi0 disabled

* case.

*/

//reset-gpios = <&gpio2 RK_PB4 GPIO_ACTIVE_LOW>;

//pinctrl-names = "default";

//pinctrl-0 = <&lcd_rst_gpio>;

};

&route_dsi1 {

status = "disabled";

connect = <&vp3_out_dsi1>;

};

DP TO VGA

arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

&dp1 {

pinctrl-names = "default";

pinctrl-0 = <&dp1_hpd>;

hpd-gpios = <&gpio1 RK_PB5 GPIO_ACTIVE_HIGH>;

status = "okay";

};

&dp1_in_vp2 {

status = "okay";

};

TYPEC DP

arch/arm64/boot/dts/rockchip/rk3588-evb1-lp4.dtsi

&dp0 {

status = "okay";

};

&dp0_in_vp2 {

status = "okay";

};

在后续文章中将对其他模块的dts进行详细解析说明,尽情关注。也可以把你需要了解的内容留言告诉我。

上一篇:Rockchip RK3588 kernel dts解析之dts架构

下一篇:Rockchip RK3588 kernel dts解析之电源模块