傻白入门芯片设计,先进封装技术(五)

集成电路芯片与封装之间是不可分割的整体。没有一个芯片可以不用封装就能正常工作,封装对芯片来说是必不可少的,随着IC生产技术的进步,封装技术也不断更新换代,每一代IC都与新一代的IC封装技术紧密相连。

目录

一、什么是封装?

二、传统封装

三、先进封装

(1)倒装芯片(FC)技术

(2)晶圆级封装(WLP)技术

(3)平板级封装(PLP)技术

(4)微系统封装技术(Micro System Packaging)

一、什么是封装?

封装(Package)顾名思义它是将一些物体进行包裹和封闭。在集成电路中则是指将裸片(Die)固定到承接基板上,同时完成一些连接并引出管脚,进而包装成一个完整的芯片。

芯片进行封装的主要目的是对芯片进行保护,同时也要确保芯片经过封装之后应当满足集成电路芯片内部电路和外部系统的电气连接。其次也起着固定、密封的作用,为芯片提供一个长期稳定可靠的工作环境,而且可以增强芯片电热性能,保证芯片正常工作的高稳定性和可靠性。

芯片封装的主要功能作用可概括为以下几点:

- (1). 传递电能。所有电子产品都以电为能源,电能的传递包括电源电压的分配和导通,在封装过程中对于电能传递的主要考量是将不同部位的器件和模块所需的不同大小的电压进行恰当的分配,以避免不必要的电损耗,同时兼顾考虑地线分配问题。电能的传送必须经过线路的连接才能实现,这是芯片封装的主要功能作用。

- (2). 传递电信号。集成电路产生的电信号或外部输入的电信号,需通过封装将不同层之间的线路传递到正确的位置,这些线路不仅要保证电信号的延迟尽可能小,而且还要保证传递的路径达到最短。因此在经过芯片封装使各线路连接后,各电子组件间的电信号传递既有效也高效。

- (3). 散热。集成电路的各元器件、部件、模块在长时间工作时会产生一定的热量。芯片封装就是利用封装材料良好的导热性能将电路间产生的热量有效地散失,使芯片在合适的工作温度下正常工作并达到各项性能指标的要求,不致因工作环境温度积累过高而造成电路的毁损。

- (4). 电路保护。有效的电路保护不仅需要为芯片和其他连接部件之间提供可靠的机械支撑,而且还要确保精细的集成电路不受外界物质的污染。芯片封装为集成电路的稳定性和可靠性提供了良好的结构性保护和支持。

- (5). 系统集成。多个芯片可以通过封装工艺集成整合为一,科学的封装工艺不仅减少了电路之间连接的焊点数量,而且可以显著减小封装体积和重量,同时缩短组件之间的连接线路,整体提高了集成电路的电性能。

- (4). 电路保护。有效的电路保护不仅需要为芯片和其他连接部件之间提供可靠的机械支撑,而且还要确保精细的集成电路不受外界物质的污染。芯片封装为集成电路的稳定性和可靠性提供了良好的结构性保护和支持。

- (3). 散热。集成电路的各元器件、部件、模块在长时间工作时会产生一定的热量。芯片封装就是利用封装材料良好的导热性能将电路间产生的热量有效地散失,使芯片在合适的工作温度下正常工作并达到各项性能指标的要求,不致因工作环境温度积累过高而造成电路的毁损。

- (2). 传递电信号。集成电路产生的电信号或外部输入的电信号,需通过封装将不同层之间的线路传递到正确的位置,这些线路不仅要保证电信号的延迟尽可能小,而且还要保证传递的路径达到最短。因此在经过芯片封装使各线路连接后,各电子组件间的电信号传递既有效也高效。

二、传统封装

传统封装概念从最初的三极管直插时期开始产生。传统封装过程如下:将晶圆(Wafer)切割为晶粒(Die)后,使晶粒贴合到相应的基板架的小岛(LeadframePad)上,再利用导线将晶片的接合焊盘与基板的引脚相连,实现电气连接,最后用外壳加以保护。典型封装方式有DIP、SOP、QFP等。

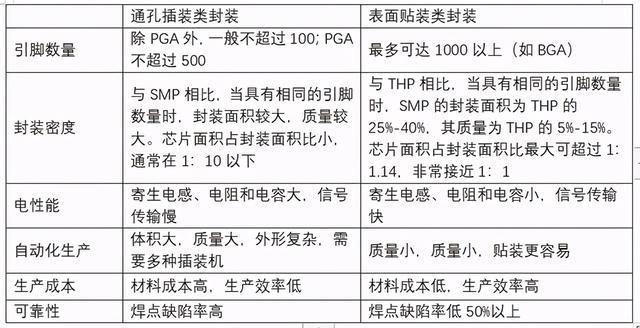

尽管表面贴装封装比通孔插装封装具有很多的优势,但由于表面贴装封装在PCB上的安装密度高,对散热的要求更高;同时,由于器件与PCB的热膨胀系数(CTE)不同,容易造成焊点处出现裂纹甚至开裂。最严重的是塑封体的吸湿问题,由于表面贴装封装在焊接时塑封体整体受热,容易造成塑封体吸收的水汽受热膨胀而产生内部分层现象,严重时可能产生塑封体爆裂。

由此可见,表面贴装封装与通孔插装封装相比,区别不仅是外形的不同,也是对集成电路芯片设计、封装结构设计、封装材料、检测技术和相应的设备提出了更高的要求

当然,通孔插装类封装具有焊接方便、可靠性好、易于维修、对材料湿气敏感要求低、散热性能好、功率大等特点,通常使用在对体积要求不严苛的场合,也可用于大功率器件的封装。因此,到目前为止,通孔插装类封装仍占据着一定的市场份额。

三、先进封装

进入21世纪,随着半导体技术逐渐逼近硅工艺尺寸的极限,半导体技术进入“后摩尔定律”时代,先进封装技术得到了空前发展。出现于20世纪末的多芯片组件(MCM)封装、系统级封装(SiP)、三维立体(3D)封装和芯片尺寸封装等技术快速发展,并被广泛应用。同时,系统级芯片(SoC)封装、微机电系统(MEMS)封装、硅通孔(TSV)技术、凸点制作(Bumping)、表面活化室温连接(SAB)等技术实现了新的突破,并已实现批量生产。

先进封装主要是指:倒装(FlipChip)、凸块(Bumping)、晶圆级封装(Wafer level package)、2.5D封装(interposer,RDL等)、3D封装(TSV)等技术。

(1)倒装芯片(FC)技术

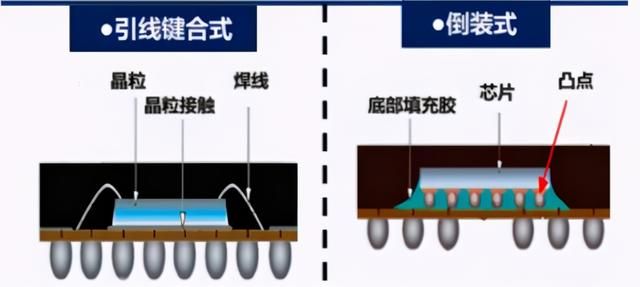

FlipChip指的是芯片倒装,以往的封装技术都是将芯片的有源区面朝上,背对基板贴装键合。而FlipChip则将芯片有源区面对着基板,通过芯片上呈阵列排列的焊料凸点(Bumping)实现芯片与基板的互联。其工艺过程为:先在芯片上制作金属凸点,然后将芯片面朝下利用焊料直接与基板相连,通常会使用底部填充(Underfill)树脂对热应力进行再分布来提高可靠性。其优点是封装面积减小,引线互连长度缩短,引脚数量增加。

传统封装和先进封装结构对比

(2)晶圆级封装(WLP)技术

在传统封装概念中,晶圆是先被切割成小的晶粒,之后再进行连接和塑封。而晶圆级封装(Wafer-level packaging(WLP))工序恰好相反,是直接以圆片为加工对象,同时对圆片上的众多芯片进行封装及测试,最后切割成单颗成品,可以直接贴装到基板或PCB上,其中主要工艺为再布线(RDL)技术,包括溅射、光刻、电镀等工序。WLP封装时裸片还在晶圆上,一般来说,WLP是一种无基板封装。WLP利用由布线层(routing layers)或重新布线层(RDL)构成的薄膜来代替基板,该薄膜在封装中提供电气连接。RDL不会直接与电路板连接。相反,WLP会在封装体底部使用锡球,从而将RDL连接到电路板。具备两大优势:(1)将芯片 I/O 分布在 IC 芯片的整个表面,使得芯片尺寸达到微型化的极限。(2)直接在晶圆片上对众多芯片封装、老化、测试,从而减少常规工艺流程,提高封装效率。

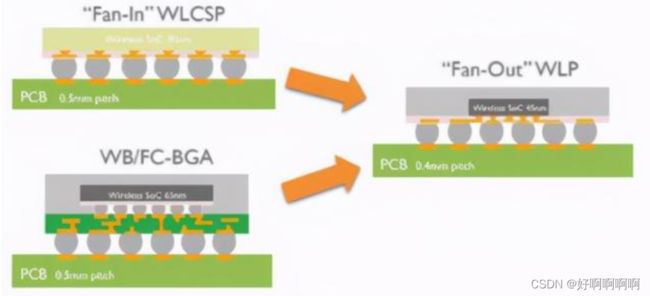

扇入型封装、倒装芯片与扇出型封装技术的比较

WLP封装与传统封装的区别在于,封装和测试程序直接在晶圆上进行,然后进行切割。根据引线方式的不同,WLP封装分为扇入式(WLCSP)和扇出式(fow-lp)。与传统封装技术相比,WLP具有成本低、散热性能好、体积小等优点。另一个显著的优点是采用了批处理操作。因此,晶圆尺寸越大,芯片尺寸越小,封装效率越高,封装成本越低。

A. 扇入型封装(Fan-in WLP):是在 wafer 未进行切片前对 wafer 进行封装,之后再进行切片分割,完成后的封装大小和芯片尺寸一致,该结构的芯片面积尺寸和最终的封装体面积尺寸为标准的1:1,扇入式 WLP 是一种独特的封装形式,并具有真正裸片尺寸的显著特点。具有扇入设计的 WLP 通常用于低输入/输出(I/O)数量(一般小于 400)和较小裸片尺寸的工艺当中。

B. 扇出型封装(Fan-Out WLP)技术:初始用于将独立的裸片重新组装或重新配置到晶圆工艺中,并以此为基础,通过批量处理、构建和金属化结构,如传统的扇入式 WLP 后端处理,以形成最终封装。其工艺过程为先将芯片作切割分离,将芯片重新布局到一块人工晶圆上,然后将芯片正面朝下黏于载具(Carrier)上,并且芯片间距要符合电路设计的节距(Pitch)规格,接着进行封胶(Molding)后形成面板(Panel),后续将封胶面板与载具分离,可实现在芯片范围外延伸RD以容纳更多的I/O数。

随着金线价格的上涨,一些公司也正在考虑采用 WLP 作为低成本替代方案,而不是采用引线键合封装(可以参考这篇文章,较为详细的介绍了芯片键合技术,包括引线键合、FC技术及TAB:(19条消息) 傻白入门芯片设计,芯片键合(Die Bonding)(四)_好啊啊啊啊的博客-CSDN博客),尤其是针对更高引脚数的器件。最近几年中,WLP 也已经被广泛用于图像传感器的应用中。目前,硅通孔(TSV)技术已被纳入用于封装图像传感器的 WLP 解决方案。其他更新的封装技术也在逐渐发展,并与现有的 WLP 技术进行整合,例如三维(3D)集成技术。

(3)平板级封装(PLP)技术

PLP:全称Panel-levelpackaging,平板级封装,封装方法与FOWLP类似,只不过将晶粒重组于更大的矩形面板上,而不是圆形的晶圆。更大的面积意味着节约更多的成本,更高的封装效率。而且切割的晶粒为方形,晶圆封装会导致边角面积的浪费,矩形面板恰恰解决了浪费问题。但也对光刻及对准提出了更高的要求。

(4)微系统封装技术(Micro System Packaging)

微系统封装技术是指将多个功能芯片,用必要的配件和装配平台,按照系统最优的原则进行集成、组合,从而构成应用产品的封装技术。微系统是以微电子技术、射频技术、无线电技术、光学(或光电子学)技术、微机电系统(MEMS)等技术为核心,从系统工程的高度出发,通过包封、互连等微细加工技术,在框架、基板等载体上制造、装配、集成出微小化的功能装置。微系统封装技术,根据其微系统定义的不同,分为微电子封装技术、射频封装技术、光电子封装技术、微机电系统封装技术和多功能系统集成封装技术等多个方面的封装技术。

在整个MEMS生态系统中,MEMS封装发展迅速,晶圆级和3D集成越来越重要。主要的趋势是为低温晶圆键合等单芯片集成开发出与CMOS兼容的MEMS制造工艺。另一个新趋势是裸片叠层应用于低成本无铅半导体封装,这种技术可为量产带来更低的成本和更小的引脚封装。但是,MEMS器件的CMOS和3D集成给建模、测试和可靠性带来挑战。

2.5D封装和3D封装详见:

(18条消息) 傻白入门芯片设计,RDL/Interposer/EMIB/TSV(三)_好啊啊啊啊的博客-CSDN博客

参考资料:(还有师兄的PPT和讲稿)

传统封装 Vs 先进封装核心技术 (baidu.com)