FPGA基本原理

FPGA基本原理

FPGA基本结构

Field—Programmable Gate Array

现场 可编程 门 阵列

1、现场可编程

通过JTAG、AS、PS等方式,可以现场对器件进行编程,以实现各种不同的定制功能;

2、门

只能实现基本逻辑关系的电路称为门,最基本的逻辑关系是与、或、非,最基本的门就是与门、或门、非门;

3、门阵列

将实现基本逻辑关系的门电路按照阵列的形式排布,就形成了门阵列;

FPGA组成三要素

.可编程逻辑功能块(类比PCB板上的各种芯片)

.片内互连线(Programmable Interconnect)(类比PCB板上各芯片之间的连线)

.输入输出块(I/O)(类比PCB板上的各种IO接口)

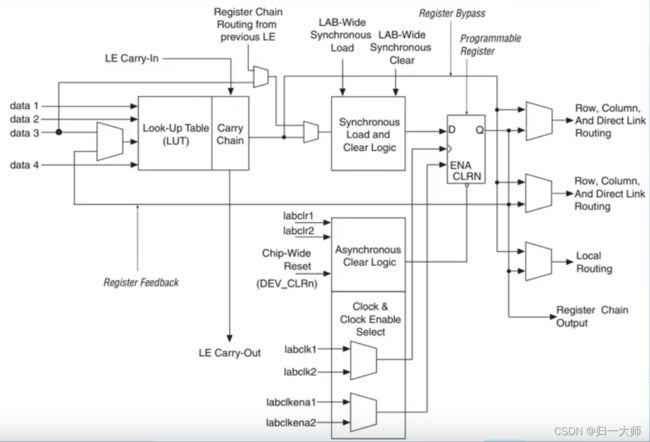

可编程逻辑功能块(FPGA逻辑资源的基本单位)(LE)

可编程逻辑功能块是实现用户功能的基本单元,多个逻辑功能通常规则地排成一个阵列结构,分布于整个芯片。

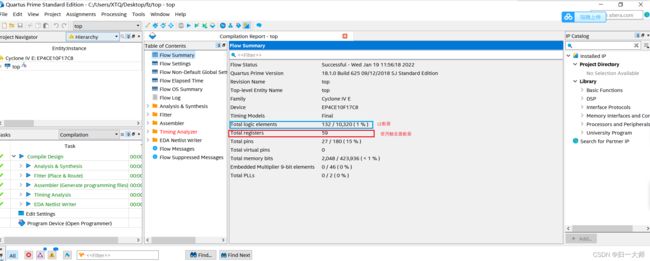

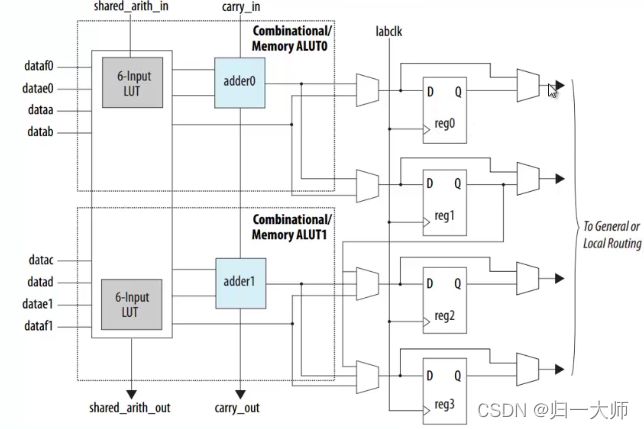

通过上图可知,该器件是四输入的查找表(LUT),查找表的运算结果可以直接通过数据选择器输出,或者通过另一个数据选择器作为D触发器(DFF)的输入;D触发器的输入也可以直接来自查找表的输入,D触发器的输出通过数据选择器的输出进行输出,所以最终输出是通过数据选择器选则查找表的输出或者D触发器的输出作为此可编程逻辑块的输出;D触发器的时钟来自数据选择器,并且上升沿有效,所以intel的器件推荐使用时钟上升沿作为D触发器的触发时钟,清零端是低电平有效,所以推荐使用低电平对D触发器进行复位。

Cyclone V器件使用的是六输入的查找表,具体是将两个四输入查找表组合成六输入的查找表;

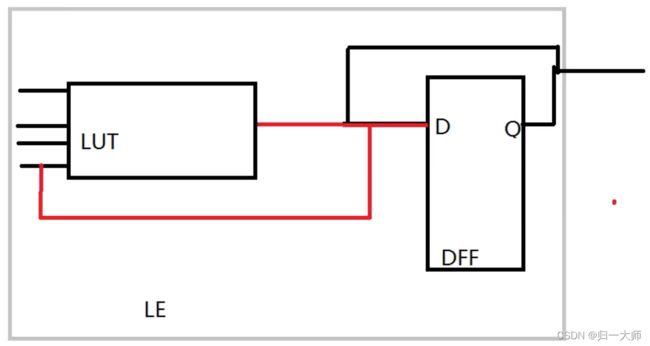

综上可编程逻辑块的简图如下:

可以只是用查找表LUT,实现组合逻辑运算;

可以只是用D触发器,实现打拍的时序逻辑;

同时使用查找表和D触发器,实现时序逻辑运算;

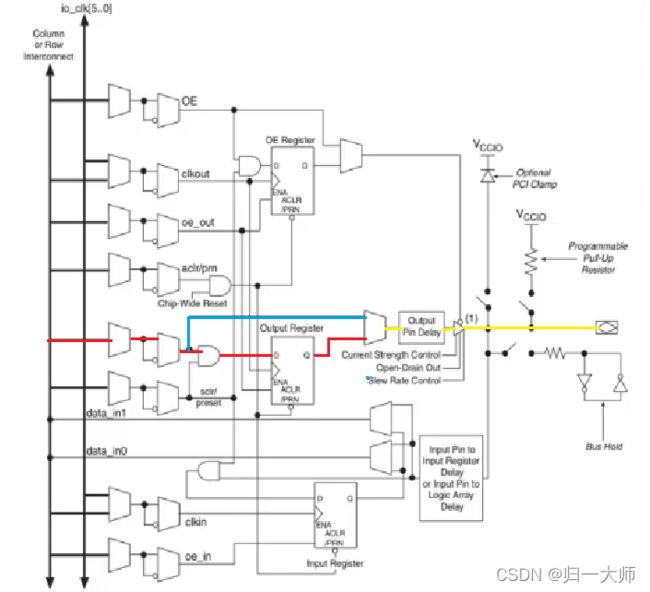

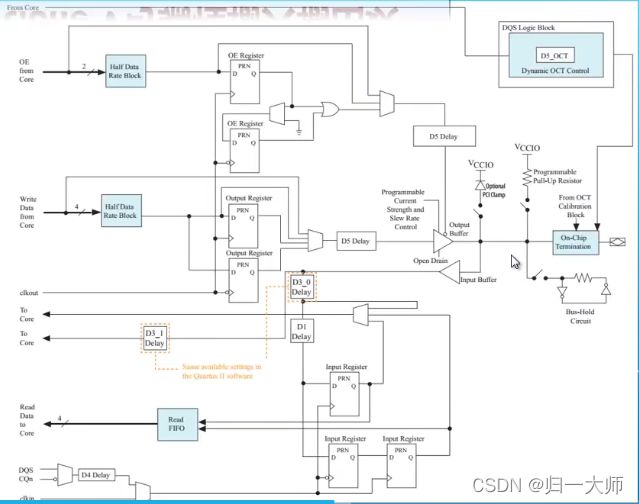

可编程输入输出块

可编程输入输出块完成芯片内部逻辑与外部管脚之间的接口,围绕在逻辑单元阵列四周,可编程输入输出块的功能和性能从一定程度上也决定了该器件的市场地位。

-

一个可编程输入输出基本单元包括:

1、输出寄存器(Output Register)

2、输入寄存器(Input Register)

3、输出使能寄存器(OE Register),用于三态功能;

4、输入延迟链

5、输出延迟链(Output Pin Delay)

6、上拉电阻(Pll Up Resistor)

数据通过总线进入可编程输入输出块之后,经过数据选择器之后可以通过蓝色走线连接数据选择器的输入端,或者通过红线进入输出寄存器中,在进入数据选择器,数据选择器选择输出其中一路信号,输出信号经黄色路径,经过输出延迟链,三态门到达输出管脚输出;

数据从输入管脚进入输入输出块,经过输入延迟链,可以直接通过数据选择器进入数据总线,也可以经过与门进入输入寄存器暂存,之后如蓝线、黄线所示,通过数据选择器进入数据总线;

输出使能寄存器(OE Register),当OE使输出的三态门使能时,该管脚作为输出,当三态门无效时,该管脚作为输入,注意当管脚作为输出时,输入通路是导通的,此时如果对输入数据进行读取,则会得到与输出相同的数据,但是此时管脚的作用是输出,所以输入是无效的,正常情况下并不会对输入进行读取,所以并没有什么影响;

可编程内部互联资源(IC)

可编程内部互联资源包括各种长度的连线线段和一些可编程连接开关,它们将各个可编程逻辑块或输入/输出块连接起来,构成特定功能的电路。用户可以通过编程决定每个单元的功能以及它们的互连关系,从而实现所需的逻辑功能。

Altera FPGA采用行、列、局部快速通道

局部快速通道最快,列快速通道次之,最后是行快速通道,时序约束时尽量让相关信号分布在局部快速通道里,可以保证系统时钟;

FPGA可编程原理

-

与CPLD的主要区别

CPLD:修改具有固定内联电路的逻辑功能来进行编程;

FPGA:修改一或多根内连线的布线,更适合实现多级的逻辑功能;

-

按编程的方式和逻辑功能的类型主要有三种:

SRAM-查找表类型(Intel Xilinx)

反熔丝的多路开关类型FPGA器件(Actel)

基于Flash的FPGA(Lattice)

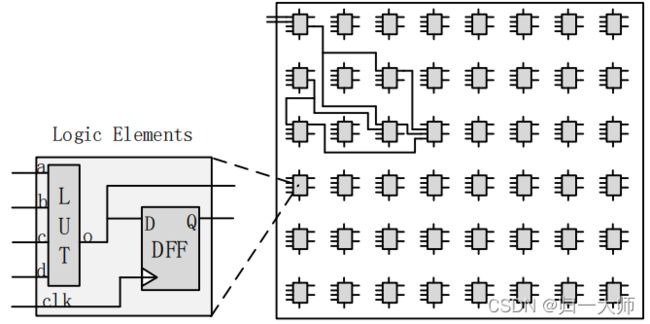

FPGA 是如何实现现场可编程的?大家可能都知道,FPGA 是基于查找表(LUT)原理实现任意组合逻辑的,那么时序逻辑呢?大家又都知道,FPGA 中有很多的 D 触发器(DFF),既然有了 D 触发器(DFF),加上时钟,就能实现时序逻辑了。那么不同的 D 触发器(DFF)之间怎么连接起来呢?答案就是内部连线。FPGA 内部有大量的长的短的连线,这些连线能够将不同的 LE 的输入和输出连接起来。这样,假设每个 LE 实现一个单独的功能,然后多个 LE 的输入输出按照一定的规则使用连线连接起来,就能实现复杂的功能了。光写文字估计大家越看越迷糊,那我就画图吧。

上图为一个最最基本的 FPGA 架构,且不包括 I/O 块。通过上图右半部分可以看到,一 个 FPGA 中以阵列的形式分布着很多的小逻辑块,这个块就是我们熟知的逻辑单元(LogicElements,简称LE),这些所有的小块共同构成了 FPGA 的可编程逻辑门阵列,而为了把不同的逻辑单元连接起来,FPGA 中分布着大量的可编程互联资源,通过对这些可编程互联资源编程,就能够把各个不同的逻辑单元的输入输出连接起来,在上图的上半部分就演示了部分互联资源将多个逻辑单元按照一定的规则连接了起来。这样看起来,是不是和我们的电路板模型非常的相似,在电路板上有各种芯片,每个芯片都有很多的管脚,通过 PCB 板走线把这些管脚按照正确的方式连接到一起,就能够形成一个可以实现特定功能的电路板了。

那么,上面说到的逻辑单元又是什么呢?在上图的左半部分,绘制了一个逻辑单元的内部示意图(简化版),可以看到,一个逻辑单元由一个查找表(LUT)和 D 触发器(DFF)组成,当然,真实的逻辑单元里面可能还包含了很多其他辅助的电路,这里省略。LUT 有 4 个 输入端口(a、b、c、d),一个输出端口(o)。LUT 的输出 Q可以送给 D 触发器的数据输入端口 D,也可以不经过 D 触发器直接输出。当然了,实际上 D 触发器的输入也可以不来自于LUT 的输出,而来自于其他逻辑单元的输出。不经过 D 触发器输出,那这个 LE 实现的就是一个纯组合逻辑,经过 D 触发器输出,那这个 LE 实现的就是一个时序逻辑。

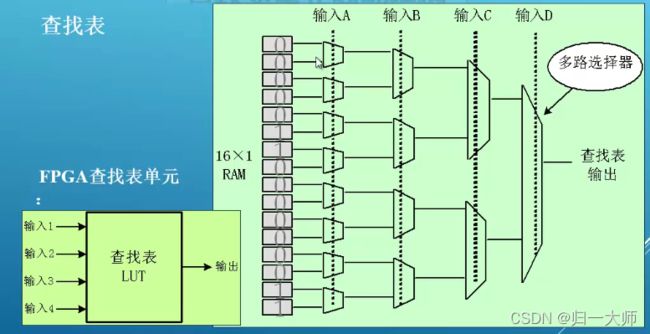

一个 LUT 里面可以实现各种组合逻辑,与门、或门、非门等等,LUT 里面实际有 16 个 1bit 的基于 SRAM 结构的存储器,能够对应 a、b、c、d 四个输入的逻辑组合的所有可能,Quartus 通过向这 16bit 的存储器里写入不同的初始值,就能使 a、b、c、d 四个输入在不同的状态下输出不同的逻辑结果,从而实现使用一个 LUT 实现各种组合逻辑的功能。

查找表实现任意逻辑的原理

原理:其实就是通过控制数据选择器将RAM的数据进行输出,比如要实现A|B|C|D运算,则该运算只有当A、B、C、D同时为0时,输出为0,其余时间输出均为1;加入规定当数据选择端输入低电平时,数据选择器的上面输入端与输出端导通,当数据选择端输入高电平时,数据选择器的下面输入端与输出端导通,则查找表应如下图所示:

对FPGA进行编程,实际上就是把需要进行的运算结果计算出来并存储在RAM之中,当输入发生相应变化时,将RAM中对应的值进行输出即可;

一个N输入查找表(LUT)可以实现N个输入变量的任何逻辑功能,如N输入“与”、N输入“异或”等。

输入多于N个的函数、方程必须分开用几个查找表(LUT)实现,这个过程由综合软件自动完成。

FPGA可选扩展资源

除了上述构成FPGA基本结构的三种资源以外,随着工艺的进步和应用系统需求的发展,一般在FPGA中还可能包含以下可选资源:

1、存储器资源(块RAM、分布式RAM);

2、数字时钟管理单元(分频/倍频、数字延迟、时钟锁定);

3、算数运算单元(高速硬件乘法器、乘法器);

4、高速串行I/O接口;

5、特殊功能模块(PCIE、DDR等硬IP核);

6、微处理器(Cortex-M3、Cortex-A9、Cortex-A53、PowerPC);

典型的FPGA内部结构

总结(需要解决的问题):

1、FPGA基本结构:

2、可编程逻辑块的基本结构:

3、LUT实现任意运算的原理:

4、可编程输入输出块的基本结构:

5、可编程互联线的意义: