m基于FPGA的GPS收发系统开发,包括码同步,载波同步,早迟门跟踪环,其中L1采用QPSK,L2采用BPSK

目录

1.算法描述

2.仿真效果预览

3.MATLAB核心程序

4.完整MATLAB

1.算法描述

最早的GPS包含L1和L2两个频段,其中L1上调制CA码,P码以及导航电文,L2上调制P码和导航电文。在实际接收到的GPS信号中,我们除了能够接受到CA码和P码外,还能检测到L1和L2两种载波信号。GPS双频发送器的基本构架如下所示:

使用CA码和P码两种码来区分双频道中的两种不同的频道。但是P码周期非常长,美国用P码周期是140多天,而简化后的民用版本也要7天多,我们无法在仿真或者实际测试的时候花那么多时间去验证P码的捕获,所以这里,我们将P码部分做了下简化,使用伪随机序列周期为2048bit,来代替P码部分。

一般情况下,导航电文的频率为50hz,CA码的频率为1M,P码的频率为10M。这里,为了测试的需要,我们需要降低频率来进行测试。整个发送端,按如下的结构设计:

通过捕获模块获得初始的频偏值,然后进行载波同步。与此同时,通过码同步,完成相位的捕获。最后进入跟踪阶段。

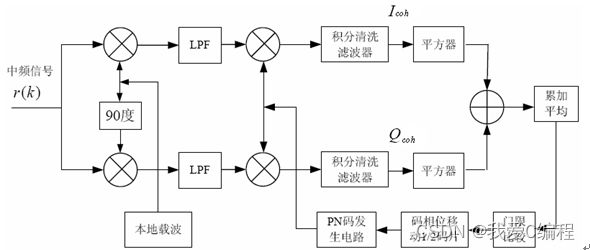

先介绍一下捕获的基本原理:

本地码生成器以C/A码标称频率产生C/A码与接收到的采样信号相关累加,一个积分周期(通常1个码周期)后,相关峰与检测门限比较,如果相关峰大于门限,则认为捕获成功,得到对应的码相位估计;如果相关峰小于门限,码发生器自动将本地码码相位向前或向后跳动1/2或1/4个码片,然后继续相关累加检测,最多在 或 个伪码周期后找到与本地伪码同步的输入伪码的相位状态( 即为一个码周期内码片的数目),以实现伪码的捕获。下面对步进相关法进行简单介绍,其原理图见图1。

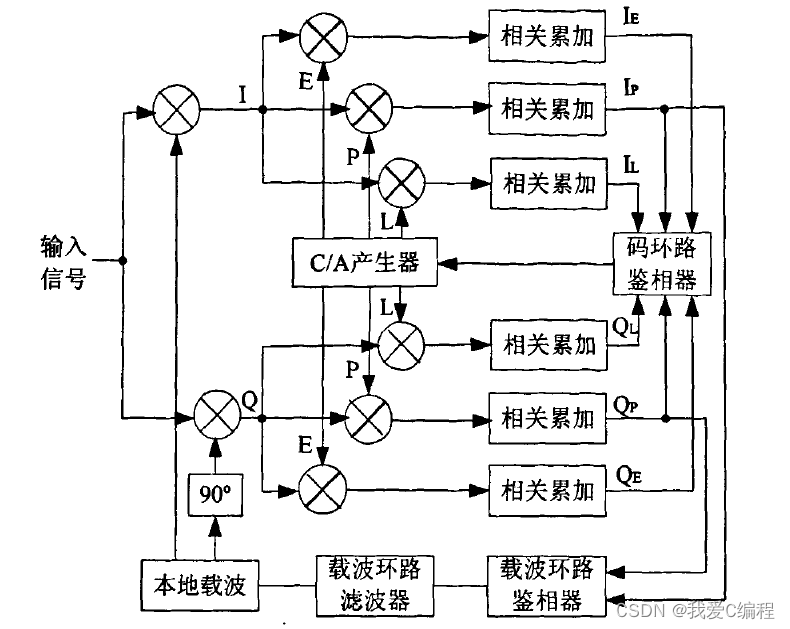

跟踪部分:

其内部详细结构如下所示:

2.仿真效果预览

算法仿真:MATLAB 2010b

FPGA设计:ISE12.2

FPGA仿真:Modelsim6.5SE

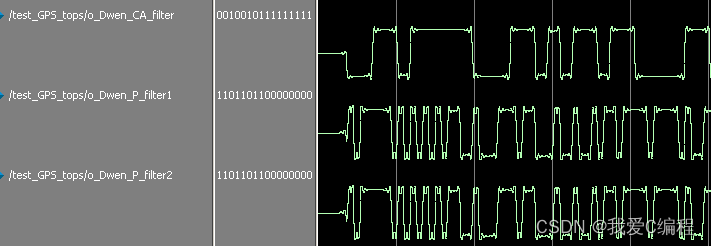

导航电文和CA码及P码异或之后的信号。

导航电文和CA码及P码异或之后的信号,通过成型滤波器之后的效果。

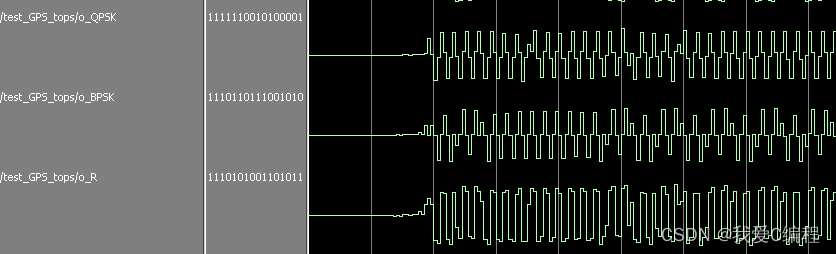

这个最后发送出去的QPSK,BPSK以及相加之后的射频信号。

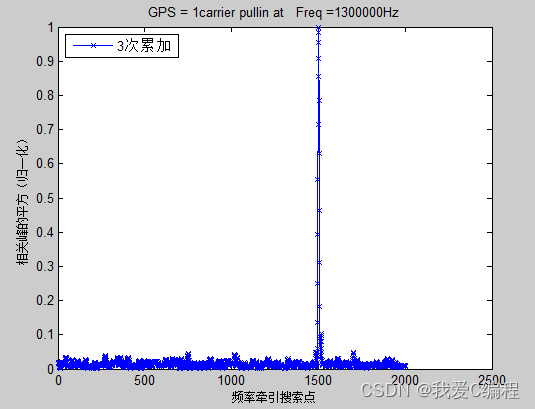

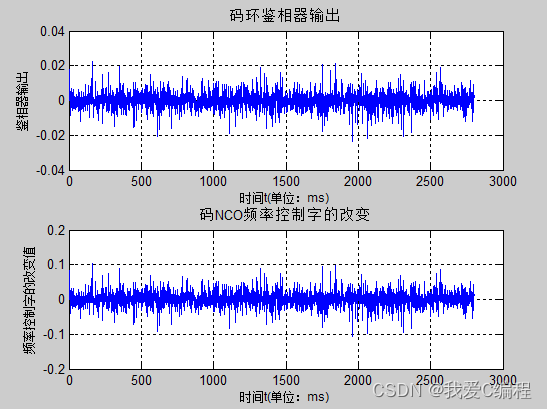

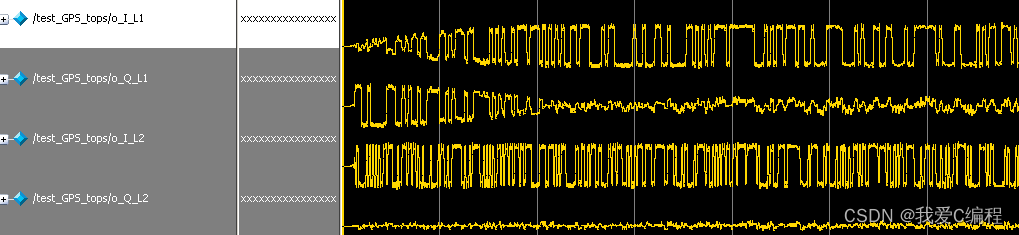

最后捕获跟踪之后的信号,放大看如下所示:

一开始的逐渐变大的过程就是锁定过程

3.MATLAB核心程序

`timescale 1ns / 1ps

module GPS_Rec(

i_clk,

i_rst,

i_QPSK,

i_BPSK,

//Capture

o_Ca_index,

o_CA,

o_abs_addCA,

o_P_index,

o_P,

o_abs_addP,

o_fre_est_Ca,

o_fre_est_P,

//Tracking

o_I_L1,

o_Q_L1,

o_I_L2,

o_Q_L2,

o_Dwen_rec_L1,

o_Dwen_rec_L2

);

input i_clk;

input i_rst;

input signed[15:0] i_QPSK;

input signed[15:0] i_BPSK;

//Capture

output [9:0] o_Ca_index;

output signed[1:0] o_CA;

output signed[21:0]o_abs_addCA;

output [10:0]o_P_index;

output signed[1:0] o_P;

output signed[23:0]o_abs_addP;

output signed[23:0]o_fre_est_Ca;

output signed[23:0]o_fre_est_P;

//Tracking

output signed[15:0]o_I_L1;

output signed[15:0]o_Q_L1;

output signed[15:0]o_I_L2;

output signed[15:0]o_Q_L2;

output signed[1:0] o_Dwen_rec_L1;

output signed[1:0] o_Dwen_rec_L2;

wire clk_ca;

wire clk_ca_2code;

wire clk_p;

wire clk_p_2code;

//2 time ca clock

CLOCK_DCM2 CLOCK_DCM2_u(

.i_clk (i_clk),

.i_rst (i_rst),

.o_clk_dwen (),

.o_clk_ca (clk_ca),

.o_clk_ca_2code (clk_ca_2code),

.o_clk_p (clk_p),

.o_clk_p_2code (clk_p_2code)

);

//CAPTURE

//CAPTURE

//frequency capture

wire signed[9:0] o_Ca_index;

wire signed[1:0] o_CA;

wire signed[21:0]o_abs_addCA;

frequency_capture_channel1 frequency_capture_channel1_u(

.i_clk (i_clk),

.i_clk_ca (clk_ca),

.i_clk_ca2times (clk_ca_2code),

.i_rst (i_rst),

.i_QPSK (i_QPSK),

.o_fre_est (o_fre_est_Ca),

.o_I_filter (),

.o_Q_filter (),

.o_Ca_index (o_Ca_index),

.o_CA (o_CA),

.o_abs_addIQ (o_abs_addCA)

);

wire signed[10:0] o_p_index;

wire signed[1:0] o_p;

wire signed[23:0] o_abs_addP;

frequency_capture_channel2 frequency_capture_channel2_u (

.i_clk (i_clk),

.i_clk_p (clk_p),

.i_clk_p2times (clk_p_2code),

.i_rst (i_rst),

.i_BPSK (i_BPSK),

.o_fre_est (o_fre_est_P),

.o_I_filter (),

.o_Q_filter (),

.o_p_index (o_P_index),

.o_p (o_P),

.o_abs_addIQ (o_abs_addP)

);

//TRACKING

//TRACKING

wire signed[15:0]o_I_filter1;

wire signed[15:0]o_Q_filter1;

wire signed[15:0]o_I_filter2;

wire signed[15:0]o_Q_filter2;

Frequency_track_tops Frequency_track_tops_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_QPSK (i_QPSK),

.i_BPSK (i_BPSK),

.i_FRE_index1(o_fre_est_Ca),

.i_FRE_index2(o_fre_est_P),

.o_I_filter1 (o_I_L1),

.o_Q_filter1 (o_Q_L1),

.o_I_filter2 (o_I_L2),

.o_Q_filter2 (o_Q_L2)

);

//CA capture

wire signed[1:0]Dwen_rec_L1;

CA_early_late_track_tops CA_early_late_track_tops_u(

.i_clk (clk_ca_2code),

.i_clk_ca (clk_ca),

.i_rst (i_rst),

.i_CA_index (o_Ca_index+1),

.i_Idin (o_I_L1),

.i_Qdin (o_Q_L1),

.o_dout (o_Dwen_rec_L1)

);

//P capture

wire signed[1:0]Dwen_rec_L2;

P_early_late_track_tops P_early_late_track_tops_u (

.i_clk (clk_p_2code),

.i_clk_p (clk_p),

.i_rst (i_rst),

.i_P_index (o_P_index+1),

.i_Idin (o_I_L2),

.i_Qdin (o_Q_L2),

.o_dout (o_Dwen_rec_L2)

);

endmodule

01_118m4.完整MATLAB

V