fpga实操训练(锁相环pll)

【 声明:版权所有,欢迎转载,请勿用于商业用途。 联系信箱:feixiaoxing @163.com】

锁相环pll是fpga区别于stm32、soc很重要的一个特征。通常来说,输入的晶振一般是25m、50m这样的,不一定能满足功能的开发。这个时候就需要对时钟进行倍频,或者分频处理。fpga上面配置pll非常简单,就算不懂得pll的实现原理,也完全也不影响自己的使用。

为了验证pll有没有成功,我们可以通过led点灯的方法,只通过修改clk0的输出,就可以判断pll是不是真的发挥了作用。

1、准备led_test项目

led_test项目的创建和之前其他fpga测试项目一样,没有什么特别之处。

2、配置pll

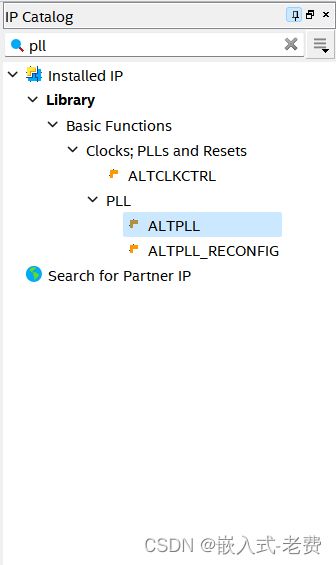

首先从IP Catalog中添加ALTPLL,

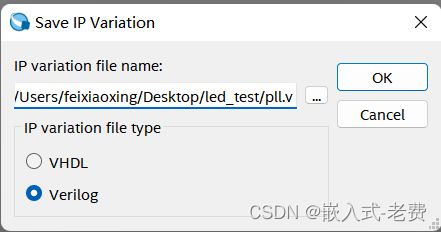

选择ALTPLL之后,单击弹出窗口,保存为pll.v文件,

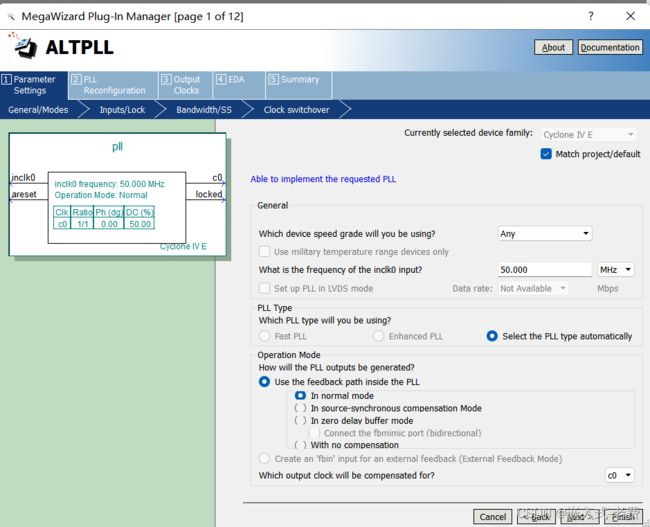

输入input时钟,我们的时钟是50M,所以这里修改成50,

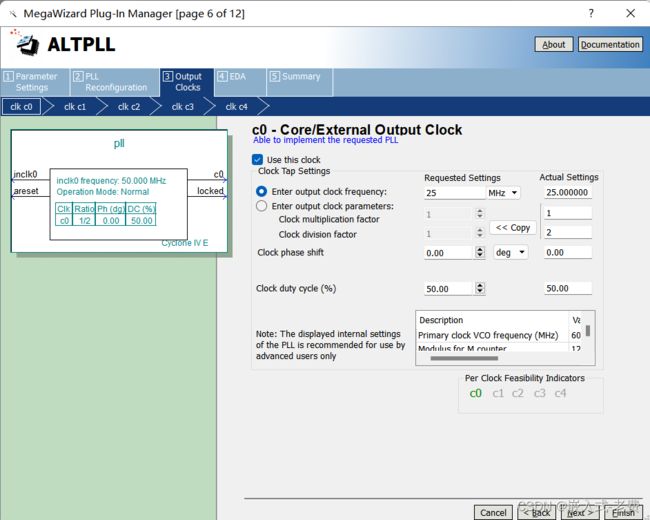

一路单击下去,直到遇到第1个输出时钟,设置为25M,

单击下一步,第2个时钟设置为50M,

继续单击,第3个时钟设置为75M,

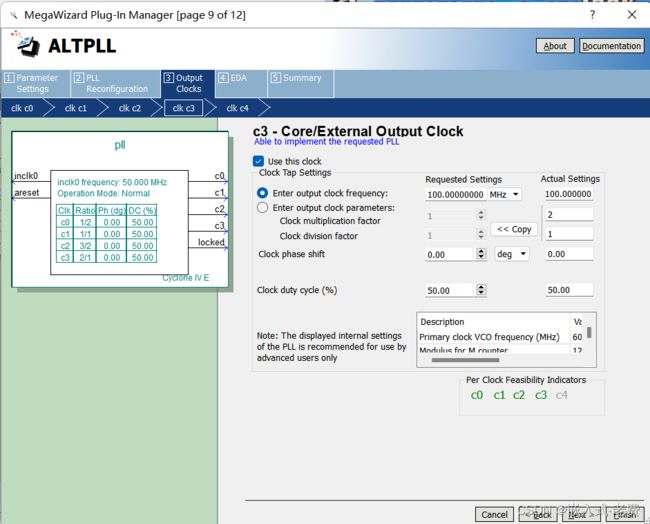

单击下一步,第4个输出时钟为100M,

单击下一步,配置最后一个时钟为200M,

单击到最后一步,直接Finish,

这个时候一般还会提醒你,是不是要把对应的文件保存在当前项目中,直接确认即可。

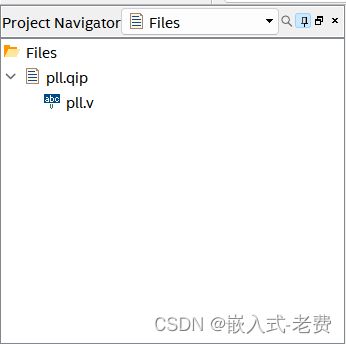

此时不出意外的话,pll.v应该已经创建好了。可以看看file视图,有没有对应的文件,

3、准备led_test.v文件

为了判断生成的pll有没有效果,还需要一个led_test.v文件,内容如下所示。注意,需要将verilog文件设置为top entry。文件中clk只是一个输入源,posedge中用到的clock已经变成了clk0。

module led_test(clk ,rst, led);

`define MAX_NUM 32'd4999_9999

// input signal

input clk;

input rst;

// output signal

output led;

// signal type

wire clk;

wire rst;

reg led;

wire clk0;

wire lock;

// inner signal

reg[31:0] count;

pll pll0(

.areset(!rst),

.inclk0(clk),

.c0(),

.c1(clk0),

.c2(),

.c3(),

.c4(),

.locked(lock));

// count register

always@(posedge clk0 or negedge rst)

if(!rst)

count <= 32'b0;

else if(count == `MAX_NUM)

count <= 32'b0;

else

count <= count + 1'b1;

// led data

always@(posedge clk0 or negedge rst)

if(!rst)

led <= 1'b1;

else if(count == `MAX_NUM)

led <= ~led;

endmodule

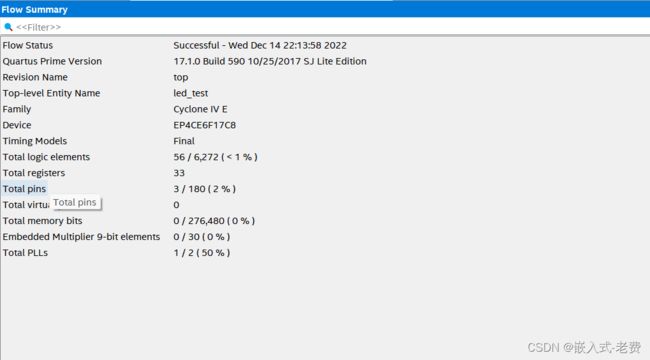

4、综合verilog文件后,没有问题的话,你会看到pll资源确实被占用了,

5、开始进行pin脚的bind处理,

6、开始对比实验测试

可以先将clk0绑定到c1上面,这个时候输出的应该是50M。那我们可以看下50M的时候,led灯的闪烁是什么情况。有了这么一个基础认知之后,就可以把clk0分别绑定到c0和c4上。分析下,是不是绑定到c0的时候,灯变慢了,bind到c4的时候灯变快了。如果确实看到了这样的效果,那说明pll确实发挥了作用,实现了倍频和分频的功能。

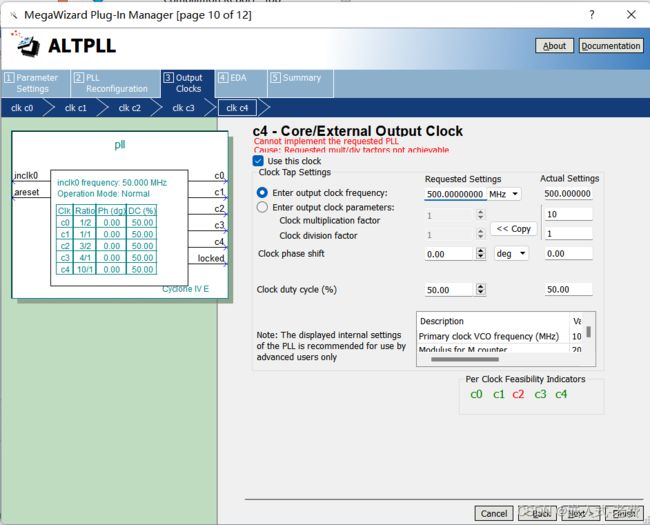

在这过程中,如果需要重新修改频率,只需要在hierarchy视图下,单击pll:pll0即可重新配置pll。目前测试下来,发现最多可以倍频8倍,达到400M,

但是如果是500M的话,就无法成功配置下去了。