VIVADO入门教学系列 1.1工程的建立逻辑分析仪的使用

随着FPGA行业热度的水涨船高,越来越多的学校开设了对应的课程,但是相信有部分同学的学校和我们一样,采用的试验箱比较老旧,对应的芯片类型不支持目前主流的VIVADO,自己购入卡发板后熟悉软件是一个比较磨人的过程。本系列文章便是为了为想要熟悉VIVADO和入门SOC的同学分享一些经验。

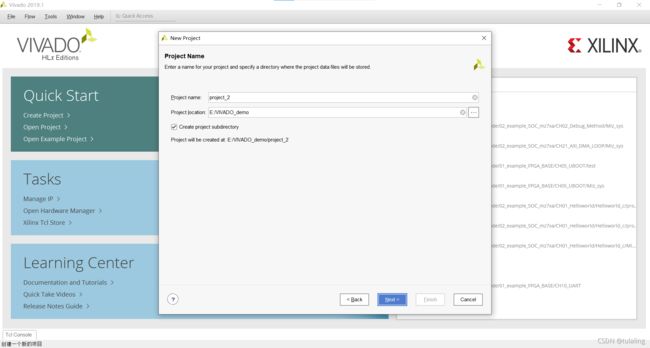

1.建立FPGA工程

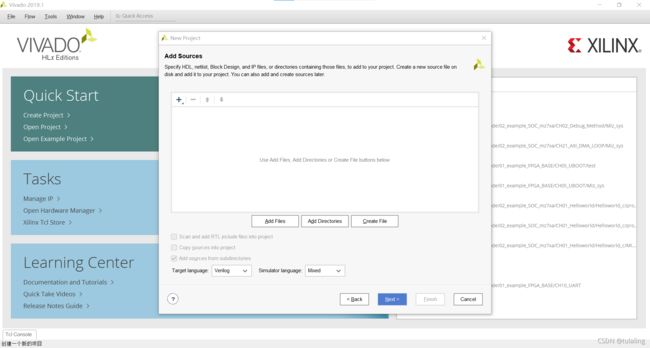

可以选择在这里创建源文件,也可以选择在工程创立后创建,这里我们选择之后再添加。一直点NEXT就可以了。

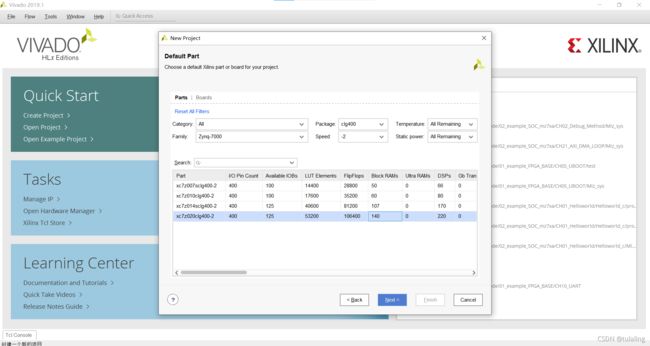

根据你的芯片选择对应的芯片型号,可以通过封装啊,速度啊来减小筛选范围 。

根据你的芯片选择对应的芯片型号,可以通过封装啊,速度啊来减小筛选范围 。

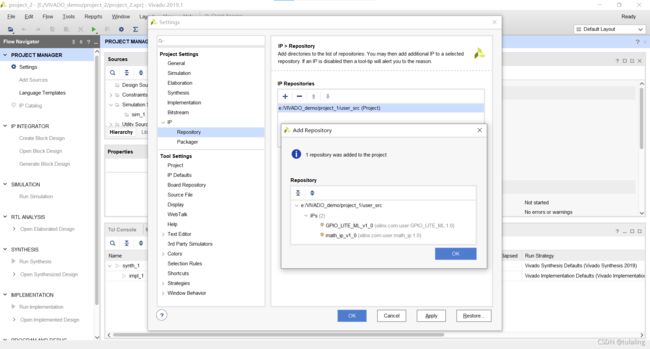

再工程建立完成后,添加你的需要用到的自定义IP到工程的文件夹中,这里我们添加的IP文件夹名为user_src(用户源文件)里面一共有两个IP核,一个叫math是一个简单的加法器,另外一个为GPIO_LITE_ML_0.

点击SEETING--->IP---->Repostiory,点击加号,添加上述文件夹路径。

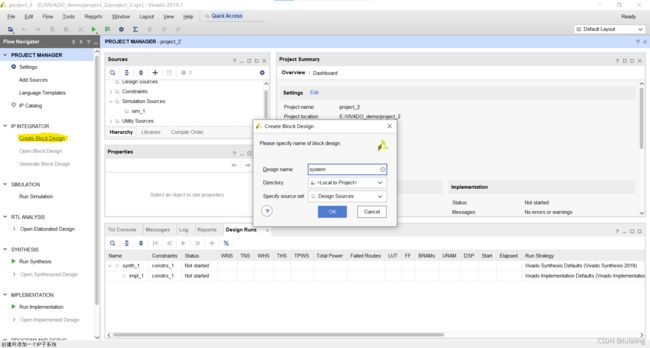

2.搭建 FPGA BD 工程

VIVADO本质上来说是一个调用IP核来实现功能的分步设计软件,SOC的设计的精髓就是IP核的调用。VIVADO的拖拽和绘图式连接无疑使得这一过程更加的直观,同时大大的降低了难度。

点击 IP INTEGROR 中的create Bolck Design

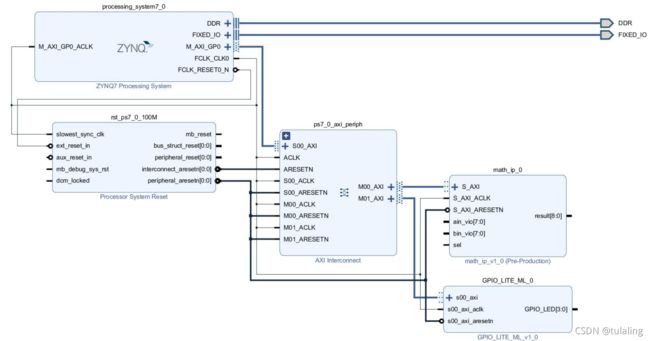

因为是SOC设计,所以这个实验工程中,除了我们上述添加的两个自定义IP,还需要调用一个处理器核。 我用的是ZYQN7020,这个芯片里自己集成了一块硬核,Z系列的其他芯片也有对应的硬核,如果卡发板上是其他系列的FPGA芯片可以从ARM官网上下载软核的IP来进行调用。除了处理器核,这里还会调用两个将来会很常用的IP核;Processor System Reset --复位 IP 和 AXI Interconnect-- 总线互联 IP。

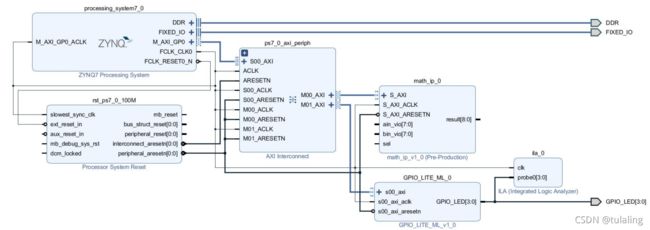

按住Ctrl+L后,输入这些IP核的名字,查找并调用他们,将它们摆放在相同位置后,如下图进行连线。在连线之前,双击这里的AXI Interconnect,设置成1个Slave,2个Mater的形式。然后注意时钟连线在一起,保证全局同步。

添加逻辑分析仪IP,同样是Ctrl+L,查找ila模块。调用后双击该模块,进行参数设置,将其设置的与GPIO部分相匹配,然后相连接。这个里为了后续方便观察,我们引出GPIO_LED.只用选中该口后Ctrl+T即可。

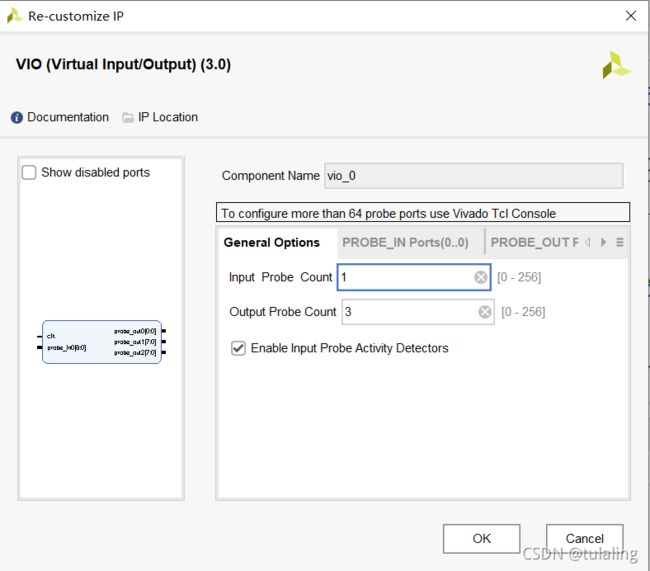

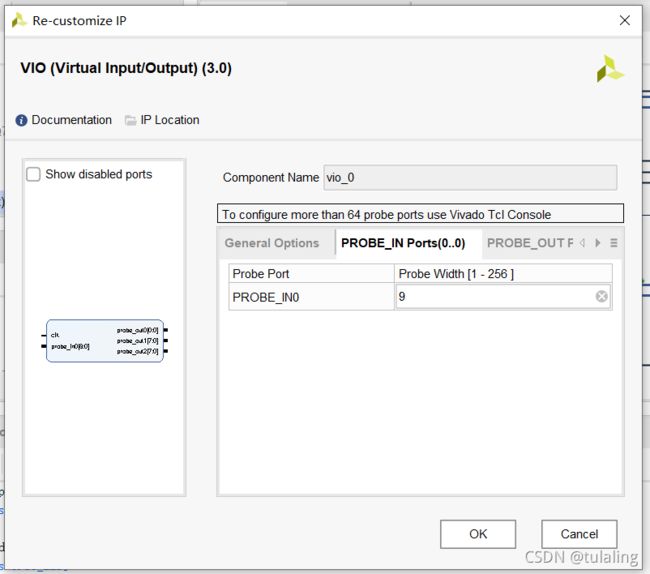

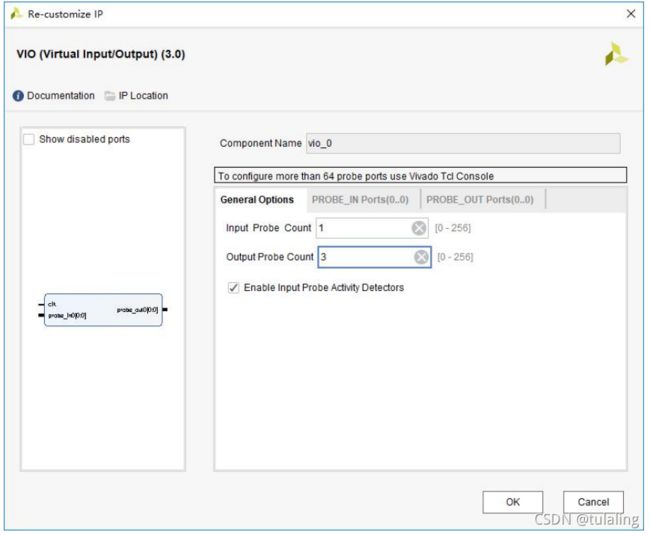

下面一步我们添加vio的 IP。老规矩Ctrl+L,查找模块vio。添加进来后,双击VIO core 修改参数 。

下面一步我们添加vio的 IP。老规矩Ctrl+L,查找模块vio。添加进来后,双击VIO core 修改参数 。

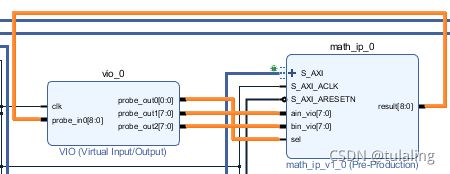

然后将它与mathIP进行连接。

右击需要观察的总线,这里选择 math_ip 的 S_AXI 接口,然后点击Debug。添加完成后,单击 内容框上方出现的Run Conection Automation。

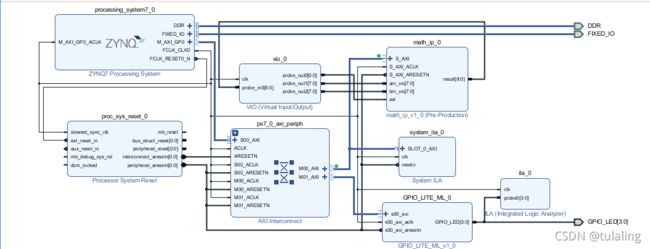

整体架构图如下所示

紧接着,根据电路板情况,编写引脚约束文件

1、分配引脚

2、电压设置

3、对生成的bit文件进行压缩

3.SDK部分的搭建

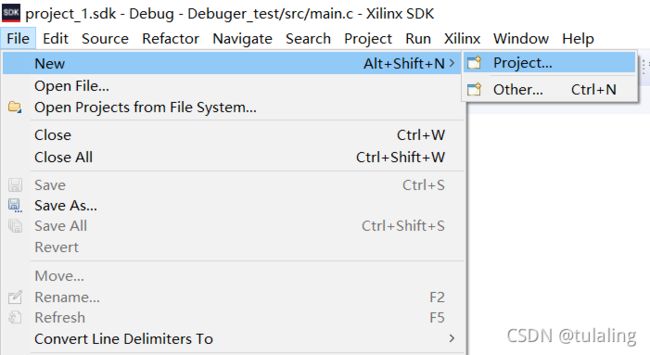

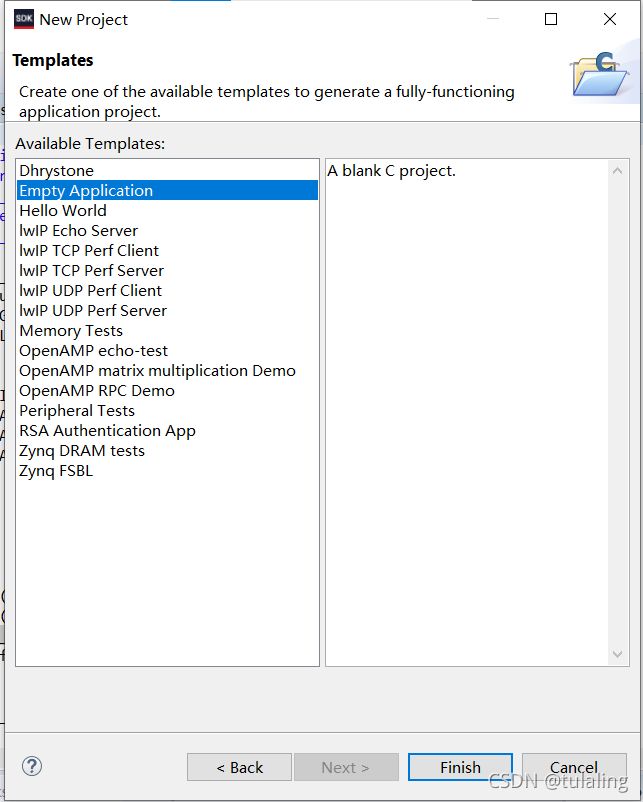

创建一个空的工程

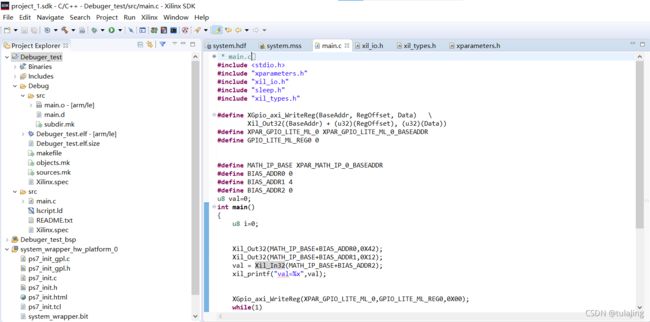

/*

* main.c

*

* Created on: 2016年11月8日

* Author: Administrator

*/

#include

#include "xparameters.h"

#include "xil_io.h"

#include "sleep.h"

#include "xil_types.h"

#define XGpio_axi_WriteReg(BaseAddr, RegOffset, Data) \

Xil_Out32((BaseAddr) + (u32)(RegOffset), (u32)(Data))

#define XPAR_GPIO_LITE_ML_0 XPAR_GPIO_LITE_ML_0_BASEADDR

#define GPIO_LITE_ML_REG0 0

#define MATH_IP_BASE XPAR_MATH_IP_0_BASEADDR

#define BIAS_ADDR0 0

#define BIAS_ADDR1 4

#define BIAS_ADDR2 0

u8 val=0;

int main()

{

u8 i=0;

Xil_Out32(MATH_IP_BASE+BIAS_ADDR0,0X42);

Xil_Out32(MATH_IP_BASE+BIAS_ADDR1,0X12);

val = Xil_In32(MATH_IP_BASE+BIAS_ADDR2);

xil_printf("val=%x",val);

XGpio_axi_WriteReg(XPAR_GPIO_LITE_ML_0,GPIO_LITE_ML_REG0,0X00);

while(1)

{

for(i=0;i<=3;i++)

{

XGpio_axi_WriteReg(XPAR_GPIO_LITE_ML_0,GPIO_LITE_ML_REG0,1< 对代码进行一定的解释,这是一段很简单的给加法器送数据和读数据的代码,while循环里放的是GPIO口值移位的程序。对总线概念不是很明确的同学可能不是很明白,去学习总线的相关概念后,整体就明朗了。

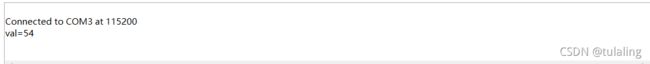

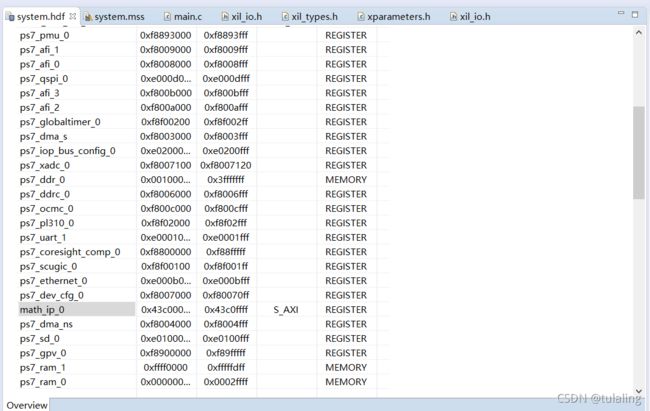

可以看到math IP的基地址为0x43C00000,所以在main中进行这个设置。两个地址偏移量和读地址偏移量是在IP核自定义时设置的,在后续我们也会分享如何自定义IP核心。

可以看到math IP的基地址为0x43C00000,所以在main中进行这个设置。两个地址偏移量和读地址偏移量是在IP核自定义时设置的,在后续我们也会分享如何自定义IP核心。

为了方便调试,我们可以在代码中添加一些断点,只需要双击main函数左边的蓝色框,即可在你期望的位置停下来。

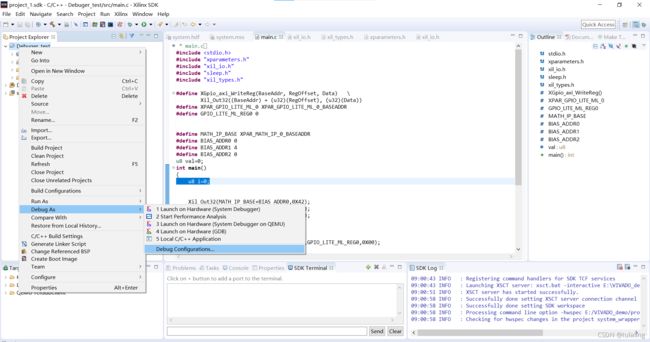

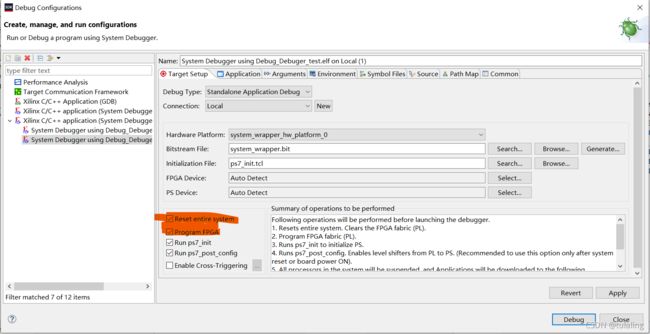

准备工作都玩成了,我们连接上JTAC准备进入到调试模式。调试模式的打开方式如下图。

双击下图蓝色框部分

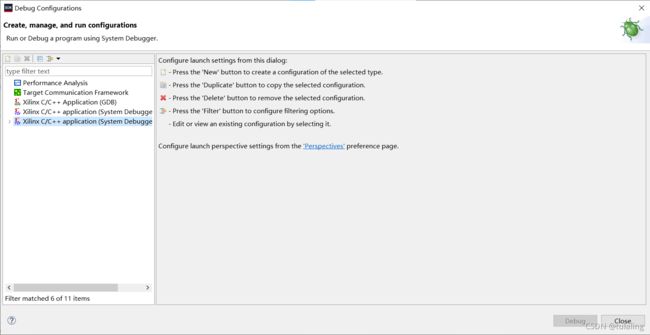

勾选下面两个选项,然后单击Apply,单机Debug

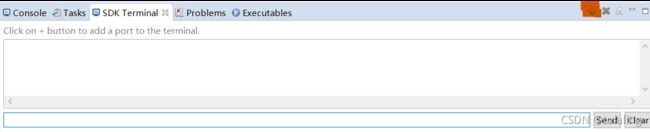

点击加号后,设置串口的端口号和波特率,方便接受我们在main中写的print函数打印出的结果。

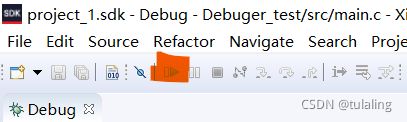

点击此处可以开始运行软核代码

4.观察时序图

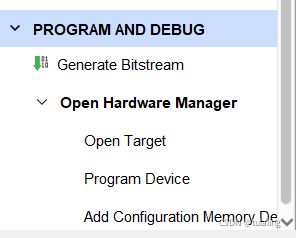

点击Open Taeget打开逻辑分析仪

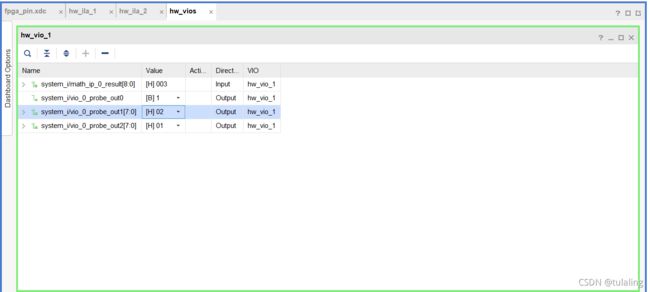

可以看到我们打开了三个调试块,

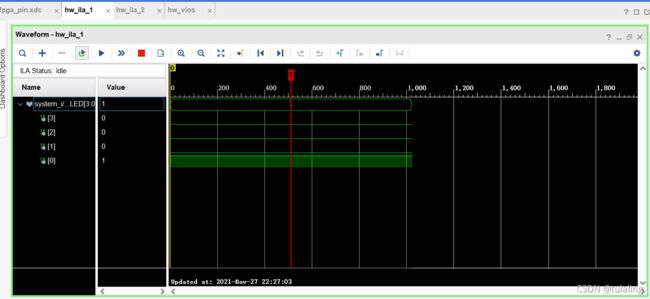

第一部分是GPIO口的部分,运行后可以看到它会定时跳转。

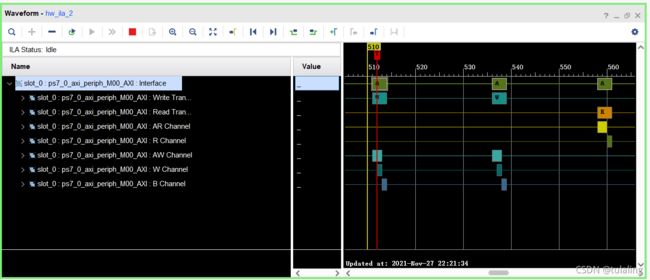

第二部分是我们添加的AXI4总线部分可以设置好触发条件后,观察自己想了解的信号,同样这部分需要有一些总线基础知识。

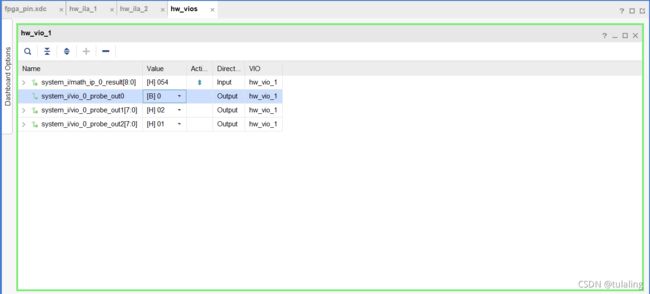

第三部分为VIO部分,我们也可以通过关闭片选信号,来测试逻辑的正确性

逻辑分析仪调用这部分就到此为止了,希望对大家有一点参考价值,下面是打包好的工程的链接,顺带安利一下不限速的阿里云盘。

「project_1」,点击链接保存,或者复制本段内容,打开「阿里云盘」APP ,无需下载极速在线查看,视频原画倍速播放。 链接:https://www.aliyundrive.com/s/PxfVVkj9s4g