matlab获取选中的点_matlab+vivado设计数字滤波器

这两个月在做数字信号处理方面的工作,也是从一个小白刚刚起步,这两天才把fir滤波器给跑通,写文记录下。希望大家欢迎,多多支持。关注公众号【数字积木】,可获取本教程的源代码工程文件。

2020-05-15

1,MATLAB代码仿真。

首先介绍下信号混频的相关概念。混频就是把两个不同频率的信号混合,得到第三个频率。数字电路中最常见的混频方法就是将两个信号相乘。将两个频率为 f0,f1 的正弦波进行相乘,根据积化和差公式,得到两个频率分量为 f0+f1 ,f0-f1 的信号。数字混频在通信的调制,解调,DUC(数字上变频),DDC(数字下变频)等系统中应用广泛。通常把其中一个信号称为本振信号( local oscillator ),另一个我信号称为混频器的输入信号。

下面的matlab代码用于验证混频器的设计。

%%信号混频

%%将两个频率为 f0,f1 的正弦波进行相乘,根据积化和差公式,得到两个频率分量为 f0+f1 ,f0-f1 的信号

clear all;close all;clc;

fs = 100*10e6; %采样频率 100MHz

f1 = 2*10e6; %信号0的频率 2MHz

f0 = 1.5*10e6; %信号1的频率 1.5MHz

fpass =1.7*10e6; %低通滤波器通带频率

fstop =1.9*10e6; %低通滤波器截止频率

DIV = 16

N = 4096; %采样点数

t = 0 : 1/fs : (N-1)/fs; %设置采样时间

Sig0 = sin (2*pi*f0*t); %生成信号0

Sig1 = sin (2*pi*f1*t); %生成信号1

Sig = Sig0 .*Sig1; %两个信号进行相乘

% 进行快速傅里叶变化,得到频谱

XK0 = fft(Sig0);

XK1 = fft(Sig1);

XK = fft(Sig);

%设置频率

f = ( 0:N/DIV-1 )*fs/( N * 10e6 ); %单位设置为MHz

Amax = max (abs( XK(1:N/DIV)));

f0 = [0 fpass/(10e6 ) fstop/(10e6 ) ( N/DIV-1 )*fs/( N * 10e6 ) ];

A = [ Amax Amax 0 0 ];

%绘制时域波形图

figure(1);

subplot(3,1,1); plot(t,Sig0); title("频率为1.5MHz的正弦信号");xlabel("时间(s)");ylabel("幅度");

subplot(3,1,2); plot(t,Sig1); title("频率为2.0MHz的正弦信号");xlabel("时间(s)");ylabel("幅度");

subplot(3,1,3); plot(t,Sig); title("1.5MHz和2.0MHz正弦波相乘得到的信号");xlabel("时间(s)");ylabel("幅度");

%绘制频域图

figure(2);

subplot(3,1,1); plot(f, ( abs( XK0(1:N/DIV) ) ) );title("1.5MHz正弦信号的频谱");xlabel("频率(MHz)");ylabel("幅度");

subplot(3,1,2); plot(f, ( abs( XK1(1:N/DIV) ) ) );title("2.0MHz正弦信号的频谱");xlabel("频率(MHz)");ylabel("幅度");

subplot(3,1,3); plot(f, ( abs( XK(1:N/DIV) ) ) );title("1.5MHz和2.0MHz正弦波相乘得到的信号的频谱");xlabel("频率(MHz)");ylabel("幅度");

hold on;

%低通滤波器示意图

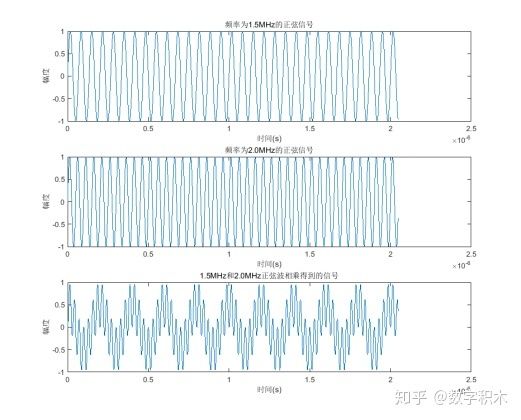

plot( f0 ,A );在该仿真代码中,设置采样时钟为100MHz,两个信号的频率分别为1.5MHz 和2.0 MHz 。两个信号相乘后,产生一个频率分量为 0.5MHz ( 2.0MHz - 1.5MHz ) 和3.5MHz ( 2.0MHz + 1.5MHz ) 的信号。时域图显示如下:

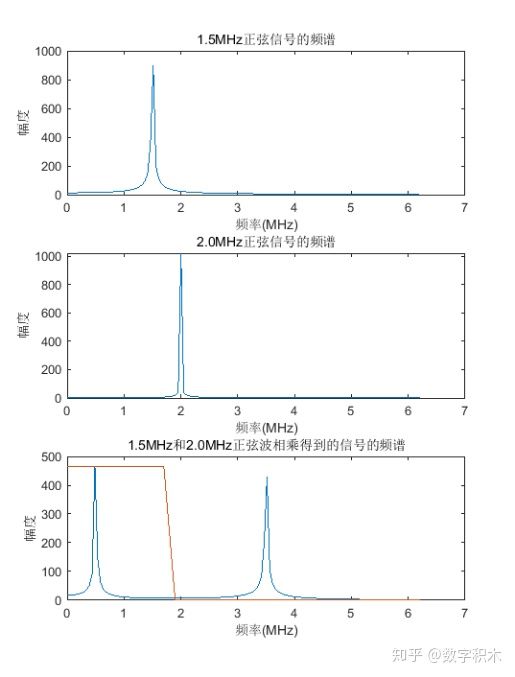

频域图显示如下:

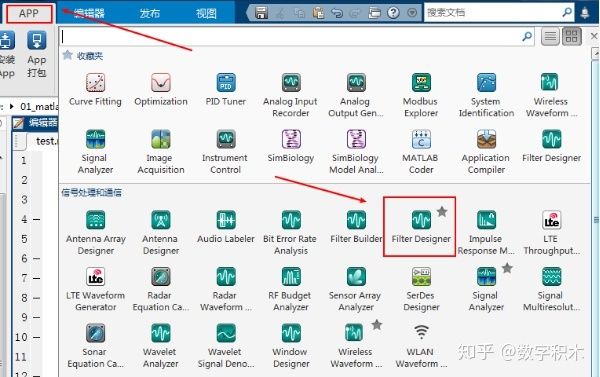

如图上所示,混频后得到了两个频率频率分量为 0.5MHz 和 3.5 MHz的信号。将该信号通过一个截止频率为2.0MHz左右的滤波器中,即可过滤掉 3.5 MHz的高频信号,只留下 0.5MHz的信号。即如上图橙色曲线所示。 2.MATLAB设计滤波器系数。 利用matlab的 滤波器设计工具箱( Filter Designer )可以非常方便地设计出符合工程要求的滤波器,在该工具箱中可以直接导出用于FPGA 滤波器设计的系数文件。

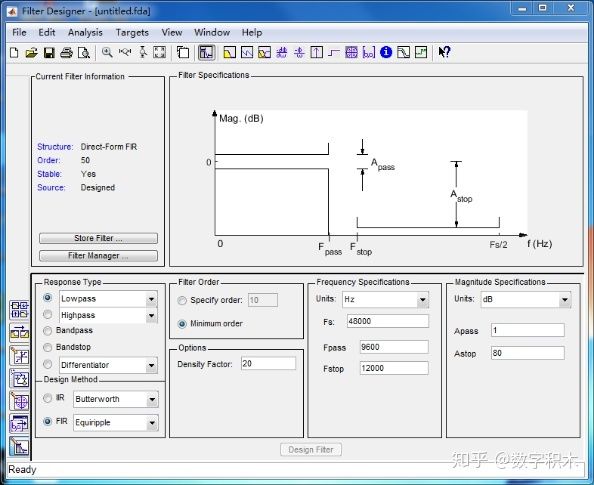

打开该工具箱后,默认显示如下:

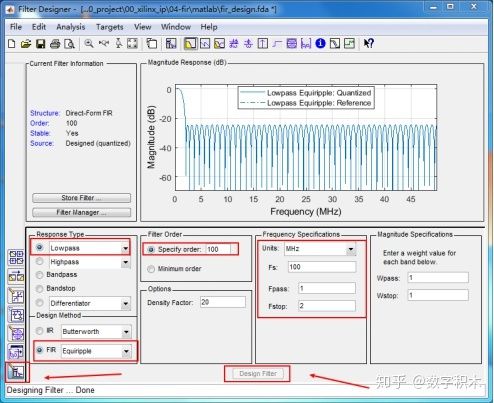

进行简单的设置:

- 滤波器类型:低通滤波器

- 滤波器形式:fir

- 滤波器阶数:100

- 频率单位:MHz

- 采样频率:100MHz

- 通带频率:1MHz

- 截止频率:2MHz

滤波器参数设置好后,点击 Designer Filter 按钮,稍等片刻,即可出现设计好的滤波器的频幅相应曲线。【注】由于是初学乍练,以上的参数设计的不一定合理,其中某些概念还不是很懂,还望通信大神指点。

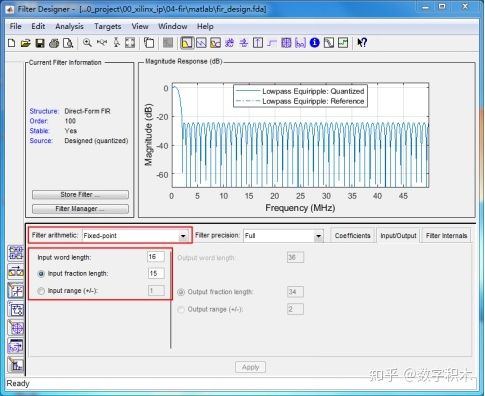

由于要在FPGA中使用,还要将浮点型的系数转化为定点数。如下图设置,设置输出格式为定点数,位宽为16bit.

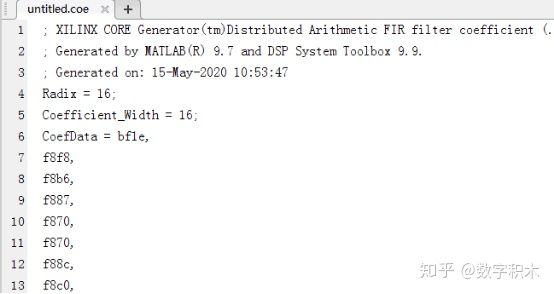

接下来就可以生成用于FPGA设计的系数文件了。在菜单【 Targets 】下点击【 XILINX coefficient(.coe)file 】,保存即可。

.coe文件中的内容大致如下,存储了滤波器的各个系数,用16进制表示。

至此,滤波器就设置完成了。 3.建立FPGA工程。 利用xilinx 的vivado工具来建立 fir 滤波器系统,对上述的matlab 程序进行硬件验证。两路正弦波信号可以用vivado 的DDS IP生成,乘法操作用乘法器IP实现,用vivado自带的fir 滤波器实现滤波。

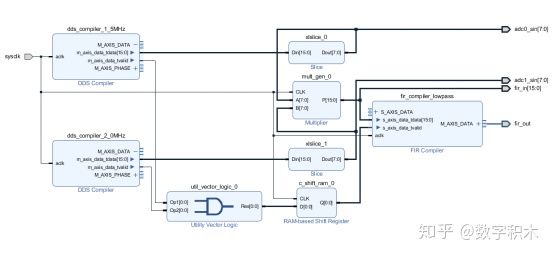

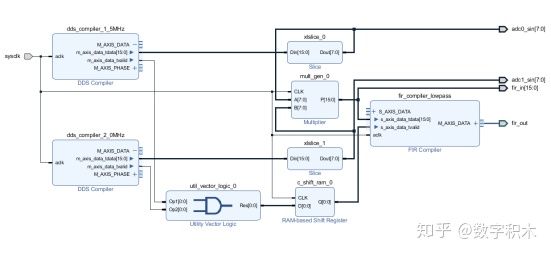

利用vivado 的 block design 工具,可以不写一行代码,实现FPGA系统的搭建。先预览下搭建好的一个简单的fir 系统工程。

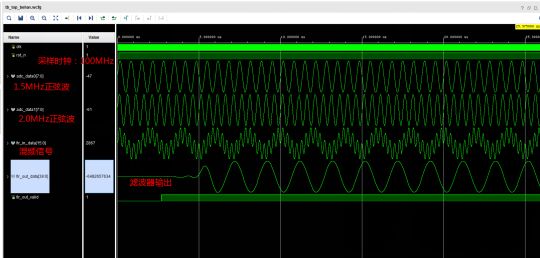

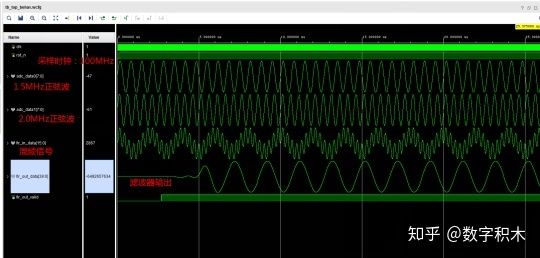

该工程中,利用两个DDS 输出 1.5MHz 和 2.0MHz 的正弦波,利用乘法器IP进行两路信号的相乘,实现混频操作。再讲混频的信号通过一个fir滤波器,实现滤波操作。 先亮以下仿真结果,漂亮的波形图。

滤波器完美输出了0.5MHz的波形,滤掉了3.5MHz的高频波。不过这是在仿真中的结果,在实际工程中,输入的信号可能含有噪声,失真等缺陷,实际效果不可能如此完美,但这个仿真结果也可以说明问题,在理想的输入下,该滤波器可以完美地滤掉高频波。

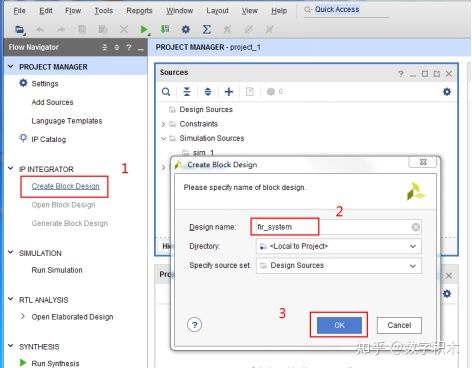

下面详细介绍 FPGA 工程的搭建。 1,建立 block design 工程。 在vivado 工具中点击 create block design ,输入 fir_system ( 该名称可以任意指定 )。

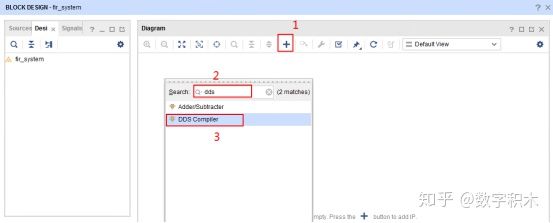

2,添加IP。 在新打开的 Diagram 视图中,添加IP 块。点击 “ + ”号,在弹出的对话框中输入DDS,双击DDS compiler ,即可将DDS IP 加入到块图中。

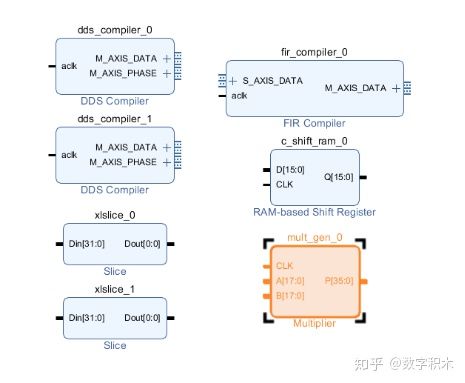

按照上面的方法依次添加两个 DDS( DDS compiler ) IP ,两个截位( slice )IP ,一个fir滤波器(fir compiler) IP,一个乘法器( mult )IP,如下图。

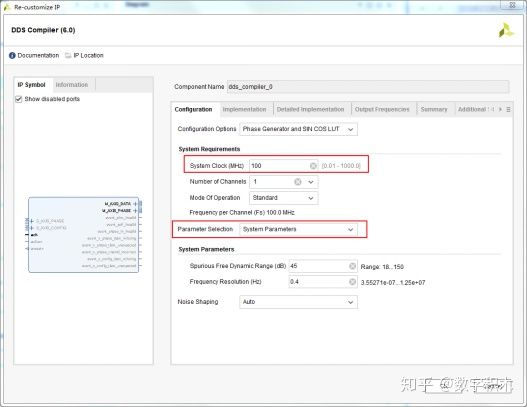

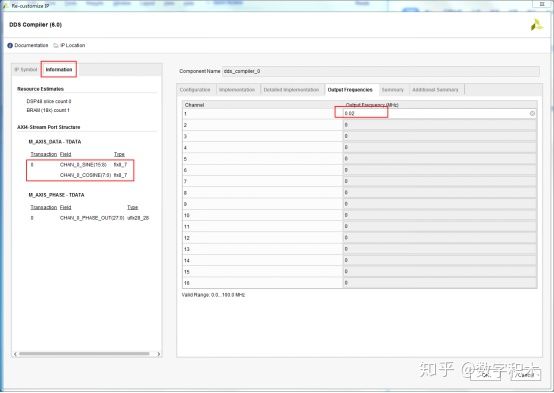

3,设置IP。 IP添加后,还有经过配置参数才能使用。双击IP 块即可进行配置。 (1)DDS配置。 两个DDS模块,一块设置输出为2.0MHz,一个设置输出为1.5MHZ,其余设置保持相同即可。时钟频率一定要设置为100MHz,和前面matlab仿真保持一致。

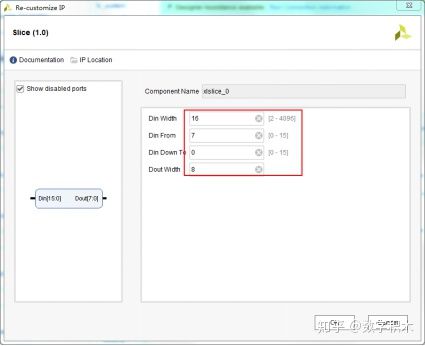

另一个DDS设置为1.5MHz 。设置方法同上。需要注意的是,如上图显示,输出数据端口(M_AXIS_DATA_TDATA)为16bit ,高8位为 正弦波(sin)数据,低8位为余弦波(cos)数据。 (2)slice IP设置。 该IP用于截位操作,设置如下,输入为16bit,输出为8bit,为16bit的bit7到bit0.位宽为8bit.该IP用于截取从DDS输出的正弦波数据。

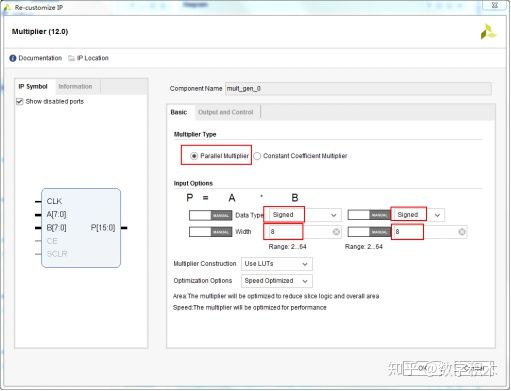

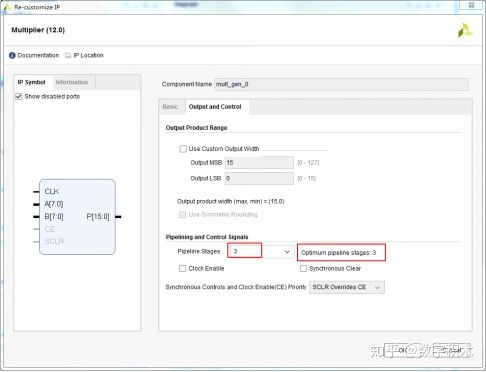

(3)乘法器IP配置。 输入位宽设置为8bit 有符号数,流水线级数采用建议的延时,设置为3.表示从输入到乘法结果输出经过3个时钟周期延时。其余可保持默认。

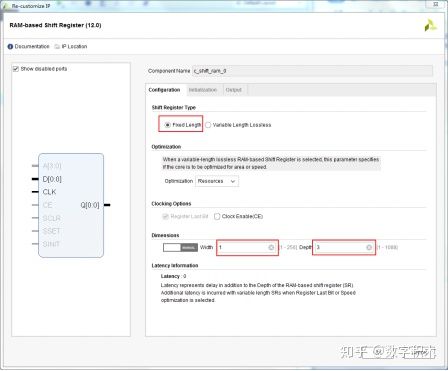

(4)移位寄存器设置。 移位寄存器用以延时数据有效信号,使其与乘法器的输出保持同步。由于乘法器有3个时钟的延迟,故将移位寄存器深度也设置为3,使其输出比输入延迟3个时钟周期。其余可保持默认。

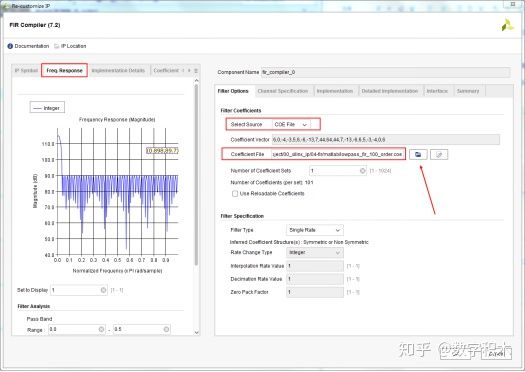

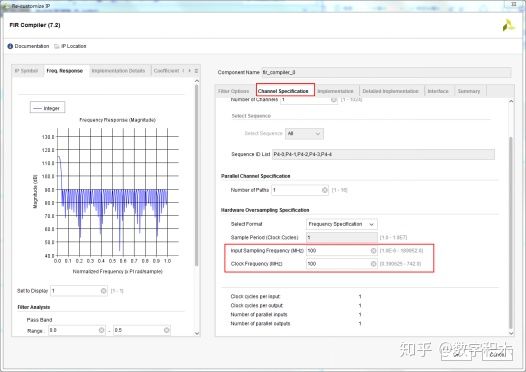

(5)fir滤波器配置。 滤波器的系数设置为coe文件,加载前面在matlab生成的coe文件,稍等片刻即可在左边窗口看到该滤波器的幅频响应曲线。将输入采样频率和时钟频率都设置为100MHz。其余可默认。

4,引出端口。 鼠标选中端口,右键选择 make external,即可导出端口。

5,IP连接。

IP最终连接如下图。

6,生成代码。

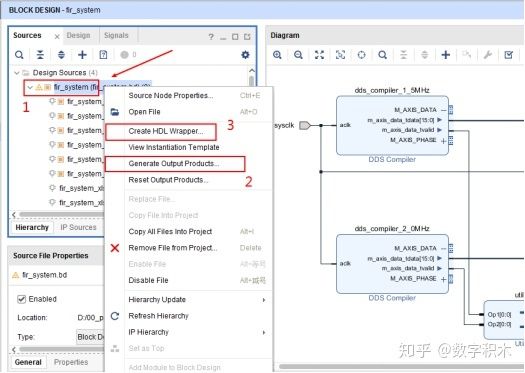

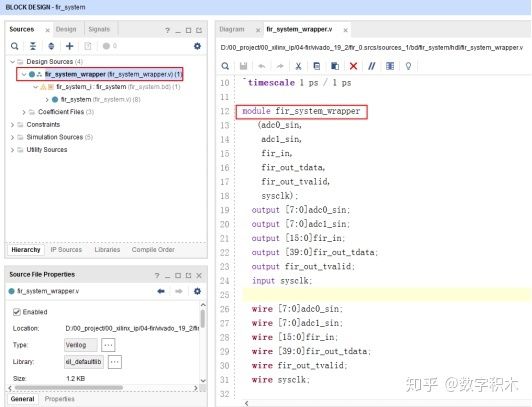

按照下图,选中块设计,右键先选择 “ generate output product...”,等待完成后在选择 “create HDL wrapper...”,即可自动生成顶层代码。

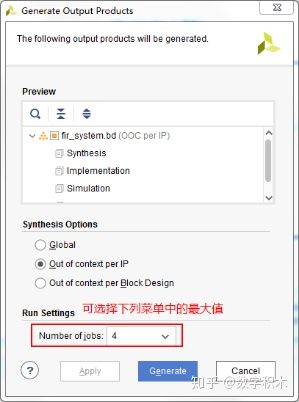

如果出现下面的界面,可选择下拉菜单中的最大值,这个选项表示运行时vivado软件可使用的最大核心数。

最终自动生成的顶层代码如下,就是对建立的原理图工程做了模块调用,其本质还是Verilog代码。

4,FPGA仿真验证。 建立如下的测试文件:

module tb_fir( );

wire [7:0]adc0_sin;

wire [7:0]adc1_sin;

wire [15:0]fir_in;

wire [39:0]fir_out_tdata;

wire fir_out_tvalid;

reg sysclk;

fir_system_wrapper fir_system_wrapper

(

.adc0_sin ( adc0_sin ),

.adc1_sin ( adc1_sin ),

.fir_in ( fir_in ),

.fir_out_tdata ( fir_out_tdata ),

.fir_out_tvalid ( fir_out_tvalid ),

.sysclk ( sysclk )

);

initial

begin

sysclk = 0;

#50000 $stop(2);

end

always #5 sysclk = ~sysclk;

Endmodule由于该工程的逻辑已在源代码中完成,故在测试文件只是对顶层模块做了例化和产生时钟信号。 最后仿真结果如下图:

滤波器完美输出了0.5MHz的波形,滤掉了3.5MHz的高频波。