verilog | 十二、状态机

-分类

根据状态机的输出是否与输入条件相关,可将状态机分为两大类:摩尔(Moore)型状态机和米勒(Mealy)型状态机。

-摩尔状态机:摩尔状态机的输出仅仅依赖于当前状态,而与输入条件无关。

-米勒型状态机:米勒型状态机的输出不仅依赖于当前状态,而且取决于该状态的输入条件。

根据状态机的数量是否为有限个,可将状态机分为有限状态机(Finite State Machine,FSM)和无限状态机(Infinite State Machine,ISM)。逻辑设计中一般所涉及的状态都是有限的,即FSM。

-FSM描述评判标准

1、FSM要安全、稳定性高。

2、FSM 速度快,满足设计的频率要求。

3、FSM 面积小,满足设计的面积要求。

4、FSM 设计要清晰易懂、易维护。

-举例

①两段式状态机描述方法

module state2 ( nrst,clk,

i1,i2,

o1,o2,

err

);

input nrst,clk;

input i1,i2;

output o1,o2,err;

reg o1,o2,err;

reg [2:0] NS,CS;

//one hot with zero idle

parameter [2:0]

IDLE = 3'b000,

S1 = 3’b001,

S2 = 3’b010,

ERROR = 3’b100;

//sequential state transition

always @ (posedge clk or negedge nrst)

if (!nrst)

CS <= IDLE;

else

CS <= NS;

//combinational condition judgment

always @ (CS or i1 or i2)

begin

NS = 3'bx;

ERROR_out;

case (CS)

IDLE : begin

IDLE_out;

if (~i1) NS = IDLE;

if (i1 && i2) NS = S1;

if (i1 && ~i2) NS = ERROR;

end

S1 : begin

S1_out;

if (~i2) NS = S1;

if (i2 && i1) NS = S2;

if (i2 && (~i1)) NS = ERROR;

end

S2 : begin

S2_out;

if (i2) NS = S2;

if (~i2 && i1) NS = IDLE;

if (~i2 && (~i1)) NS = ERROR;

end

ERROR : begin

ERROR_out;

if (i1) NS = ERROR;

if (~i1) NS = IDLE;

end

endcase

end

//output task

task IDLE_out;

{o1,o2,err} = 3'b000;

endtask

task S1_out;

{o1,o2,err} = 3'b100;

endtask

task S2_out;

{o1,o2,err} = 3'b010;

endtask

task ERROR_out;

{o1,o2,err} = 3'b111;

endtask

endmodule

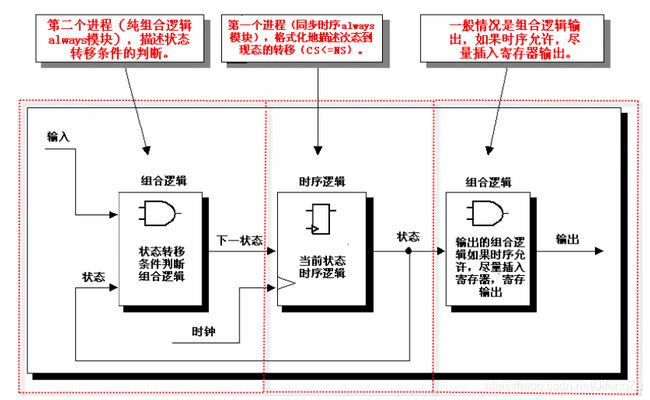

②三段式状态机描述方法

module state2 ( nrst,clk,

i1,i2,

o1,o2,

err

);

input nrst,clk;

input i1,i2;

output o1,o2,err;

reg o1,o2,err;

reg [2:0] NS,CS;

//one hot with zero idle

parameter [2:0]

IDLE = 3'b000,

S1 = 3'b001,

S2 = 3'b010,

ERROR = 3'b100;

//1st always block, sequential state transition

always @ (posedge clk or negedge nrst)

if (!nrst)

CS <= IDLE;

else

CS <=NS;

//2nd always block, combinational condition judgment

always @ (nrst or CS or i1 or i2)

begin

NS = 3'bx;

case (CS)

IDLE : begin

if (~i1) NS = IDLE;

if (i1 && i2) NS = S1;

if (i1 && ~i2) NS = ERROR;

end

S1 : begin

if (~i2) NS = S1;

if (i2 && i1) NS = S2;

if (i2 && (~i1)) NS = ERROR;

end

S2 : begin

if (i2) NS = S2;

if (~i2 && i1) NS = IDLE;

if (~i2 && (~i1)) NS = ERROR;

end

ERROR : begin

if (i1) NS = ERROR;

if (~i1) NS = IDLE;

end

endcase

end

//3rd always block, the sequential FSM output

always @ (posedge clk or negedge nrst)

if (!nrst)

{o1,o2,err} <= 3'b000;

else

begin

{o1,o2,err} <= 3'b000;

case (NS)

IDLE: {o1,o2,err}<=3'b000;

S1: {o1,o2,err}<=3'b100;

S2: {o1,o2,err}<=3'b010;

ERROR: {o1,o2,err}<=3'b111;

endcase

end

endmodule -注意事项

1、编码:

Binary(二进制编码)、gray-code(格雷码)编码使用最少的触发器,较多的组合逻辑,而 one-hot(独热码)编码反之。one-hot 编码的最大优势在于状态比较时仅仅需要比较一个 bit,一定程度上从而简化了比较逻辑,减少了毛刺产生的概率。由于 CPLD 更多地提供组合逻辑资源,而FPGA 更多地提供触发器资源,所以 CPLD 多使用 gray-code,而 FPGA 多使用 one-hot 编码。另一方面,对于小型设计使用 gray-code 和 binary 编码更有效,而大型状态机使用one-hot 更高效。

2、初始化状态:

一个完备的状态机(健壮性强)应该具备初始化状态和默认状态。当芯片加电或者复位后,状态机应该能够自动将所有判断条件复位,并进入初始化状态。

3、默认状态:

完整的状态机应该包含一个默认(default)状态,当转移条件不满足,或者状态发生了突变时,要能保证逻辑不会陷入“死循环”。这是对状态机健壮性的一个重要要求,也就是常说的要具备“自恢复”功能。