RISC-V 架构及MRS 开发环境介绍

一. RISC-V架构介绍

1. RISC 架构的起源

1981年,在David Patterson(大卫·帕特森)的 带领下,美国加州大学伯克利分校的一个研究团队起 草了RISC-I,是今天RISC架构的基础。随后在1983年 发布了RISC-II原型芯片,1984年和1988年发布了 RISC-III和RISC-IV。RISC的设计理念也催生了一系列 新架构,如MIPS、服务器的王者IBM PowerPC以及 现在统治嵌入式市场的ARM。

2. 什么是RISC-V

RISC全名Reduced Instruction Set Computer,即精简指令集计算机;V是罗马字母,代表第五代。 RISC-V,是一种特定指令集架构。RISC-V指令集,类似于INTEL的X86、ARM指令集,是一个被CPU读取到内存后,指导计算机运行的指令集合。使用该指令集的CPU,能执行指令集中规定的所有基本指令。按该套指令集编译的程序能够无 障碍运行,且具有同系列CPU可移植性和兼容性。 开源指令集RISC-V允许任何人设计、制造和销售 RISC-V芯片和软件。

3.RISC-V 的优点

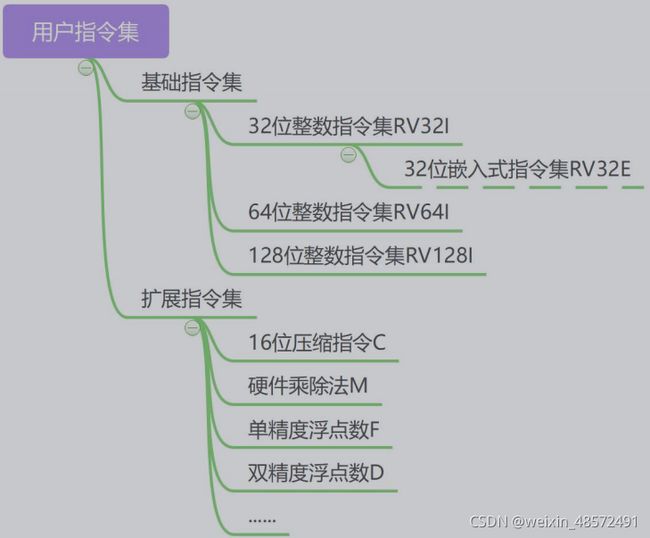

1. 模块化设计

RISC-V的指令集使用模块化的方式进行组织,每一个模块使用一个英文字母来表示。RISC-V最基本也是唯一强 制要求实现的指令集部分是由I字母表示的基本整数指令子集,使用该整数指令子集,便能够实现完整的软件编译器 。其他的指令子集部分均为可选的模块,使得RISC-V具有了袖珍化、低能耗的特点。把代表扩展的字母附加到指令 集名称之后,例如,乘法(RV32M),单精度浮点(RV32F)和双精度浮点(RV32D),可扩展添加到基础指令集 (RV32I)中。

2.规整的指令编码

RISC-V的指令集编码非常的规整,指令所需的通用 寄存器的索引(Index)都被放在固定的位。因此指令译码器(Instruction Decoder)可以非常便 捷的译码出寄存器索引,然后读取通用寄存器组(Register File)。

3.开源和免费

RISC-V最大的优势就是开源和免费。免费意味着RISC-V可以帮助开发者低成本完成CPU设计,如果最终量产, 那么就免去面对版税纠纷。对RISC-V指令集来说,RISC-V的标准化工作由RISC-V基金会主持,对任何想要用 RISC-V设计实现处理器的公司与个人,都不会受到来自RISC-V基金会的限制,也无须向RISC-V基金会支付授权费用。 基金会各会员公司也承诺不会就RISC-V的基本议题向其他成员发起诉讼。这使得RISC-V处理器的设计者无须 再担心与指令集本身相关的专利诉讼,这也是RISC-V被称为开放指令集的主要原因。

4.RISC-V目前的应用

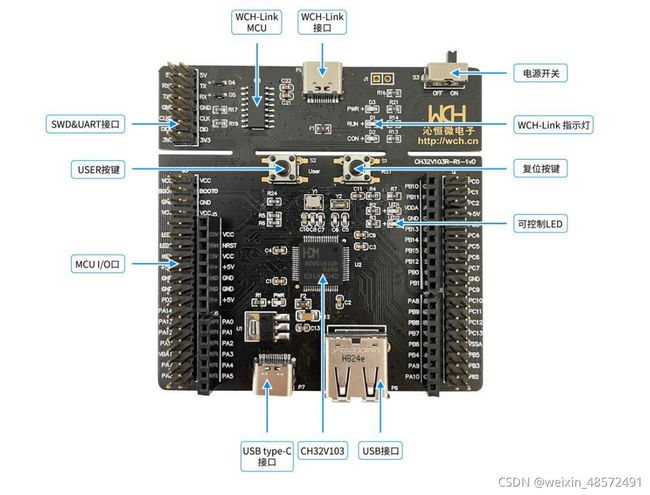

沁恒微电子于2020年2月24日发布了首款基于 RISC-V架构,自主设计的RISC-V3A处理器内核及 其硬件产品—— CH32V103系列MCU。 作为长久以来对RISC-V架构关注和研究的成果, RISC-V3A处理器支持IMAC指令子集,内嵌了PFIC 中断控制器,提供硬件加速中断进出栈模式、快速 中断通道(硬件获取中断源)等设计,加快了中断 服务函数响应;集成了2线方式的调试接口,方便运 行的跟踪和调试。

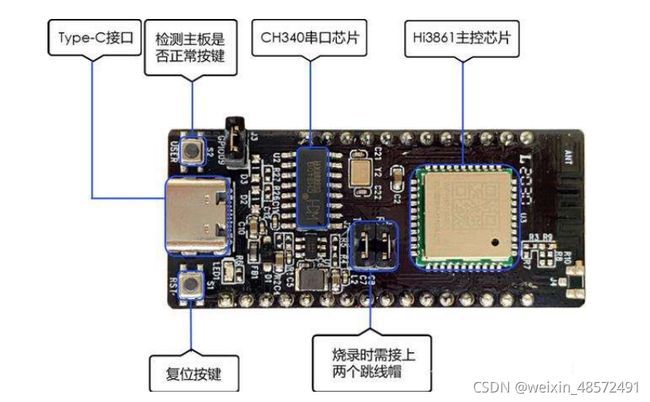

2021年5月,为了克服美国对使用最新 ARM 设计的限制,华为海思转向了开源指令集架构 RISC-V,针对鸿蒙操作系统的开发者发布了首款 RISC-V 开发板 Hi3861。Hi3861 针对的是物联网市场,突破ARM限制。

5.RISC-V架构应用前景

RISC-V的应用之一:手机市场

根据SiFive首席执行官Naveed Sherwani的预测, RISC-V将会进军手机市场,与高通、苹果、三星、联发科 等ARM公司抢智能手机处理器市场,同时有可能威胁低功 耗笔记本处理器。

RISC-V的应用之二:服务器市场

虽然目前RISC-V的高性能市场一片空白,但RISC-V 本身用来设计高性能芯片是没有问题的,学术界已经有基 于RISC-V架构的511核处理器(Celerity)。只是基于 RISC-V的低门槛特点,进入的企业体量较为小巧,没有足 够的资金做长期布局与研发,高性能等需要较长研发时间 的领域尚无人尝试。 根据SiFive首席执行官Naveed Sherwani的预测,5年 后RISC-V指令的处理器就有可能进军服务器市场。

RISC-V的应用之三:存储市场

硬盘本身并不需要像SSD那样庞大的计算资源,但是由 于新的磁记录技术,更复杂的功能(例如,基于NAND Flash 的缓存,健康管理,服务质量),它们的处理要求也在增长 增强等。这对存储器中控制芯片的计算能力要求变高了。 2017年,根据IDC和希捷的数据,2016年全球产生了16.1个 ZB(ZetaBytes)数据,到2025年全球数据球体将增长一个 数量级到163个ZB。并且需要实时处理和低延迟的数据量正 在增长。 虽然数据可以就近传输到附近的服务器汇总进行处理, 这需要更为强大的服务器,但服务器本身对处理快数据的效 率不高,因此硬盘不仅存储数据,还需要进行处理。

6.RISC-V 带来的机遇和挑战

中国工程院倪光南院士:RISC-V架构未来将会和X86以及ARM在CPU领域“三分天下”

中国工程院 倪光南院士 在RISC-V2021中国峰会上发表演讲: RISC-V是未来推动新一代信息技术发展的动力。对于RISC-V的重视,不仅是芯片设计和学校教学方面,我们必 须提到一个新的高度,CPU架构对芯片产业有引领作用。芯 片的设计采用不同架构,生态就不一样。光是把CPU架构看作影响芯片设计还不够,而是对整个芯片产业,芯片架构是 源头,它会影响到人才培养,IP库,EDA工具、芯片生产制造,测试封装等等。中国适当聚焦RISC-V,有助于中国芯片产业实现自立自强。

二. MRS 开发环境介绍

MounRiver Studio(MRS)是一款针对RISC-V/ARM双核MCU的嵌入式集成开发环境,由MounRiver 团队基于GNU

Eclipse深度定制而成,提供了包括定制版GCC、宏汇编、链接器、调试器、下载器等在内的完整开发资源。

一. MRS 安装说明

MRS安装推荐配置:

CPU主频: 2 GHz及以上

系统内存: 2GB及以上

硬盘剩余空间:2GB及以上

操作系统:Windows7及以上

注意事项:

安装路径:不能带有空格及特殊字符,支持中英文

工程路径:不支持中文/空格/特殊字符

官网:www.mounriver.com

二. MRS 界面展示

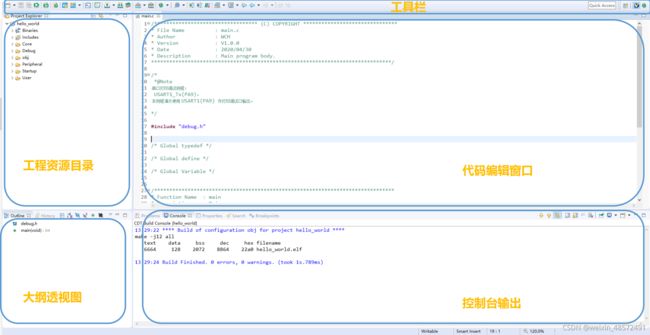

MounRiver Studio(MRS)是基于Eclipse GNU版本 开发,进行了一系列界面、功能、操作方面的修改与优化,以 RISC-V内核为主的嵌入式集成开发环境。

主界面

调试界面

Debug界面下,通过菜单栏Window->Show View,添加更多的监控窗口:

1.“Breakpoints”断点管理窗口。标识了当前工程中所有断点的位置,通过勾选 断点复选框来启用或失效当前断点,各断点位置跳转,删除等等。

2.“Disassembly”汇编窗口。同步当前代码运行位置。

3.“Expressions”全局变量监视窗口。在里面可输入代码中的全局变量进行观察。

4.“Memory”内存查看窗口。可添加要观察的存储器地址,支持多种显示格式, 各自独立窗口显示。

5.“Peripherals”外设管理窗口。查看当前硬件平台的外设寄存器各个位,勾选 相应外设模块,可以在“Memory”窗口中看到详细信息。

6.“Project Explorer”工程大纲窗口。工程目录。

7.“Registers”寄存器窗口。查看硬件平台内核通用寄存器及系统寄存器。

8.“Variables”局部变量监视窗口。会自动识别当前函数内部变量进行添加查看。

三. MRS 使用方法

MRS具体下载步骤以及使用方法请大家参考如下链接:

下载安装及更新

新建工程及文件操作

代码烧录

工具链及编译参数