数字集成电路与系统设计基础知识

数字集成电路与系统设计基础知识(一)

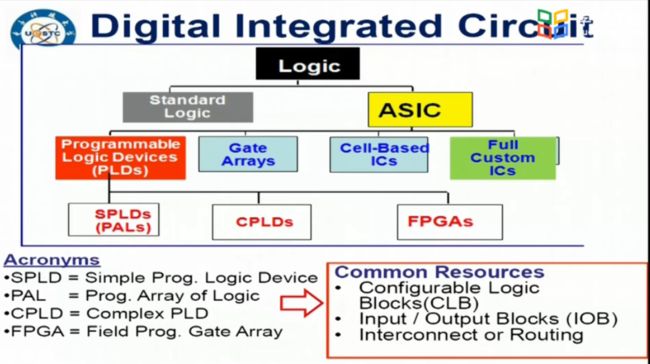

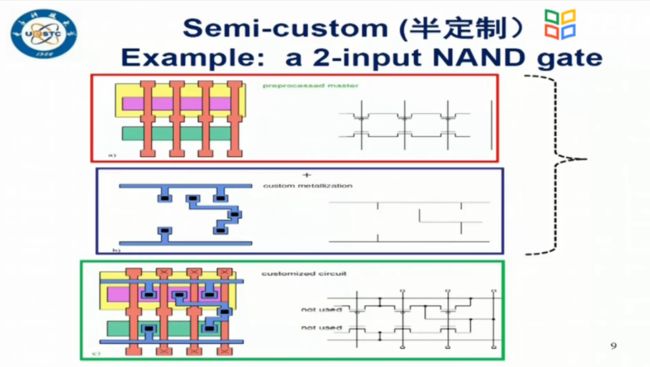

ASIC可分为全定制和半定制。

半定制是调配厂家的设计资源(库单元),全定制是全部自己做。

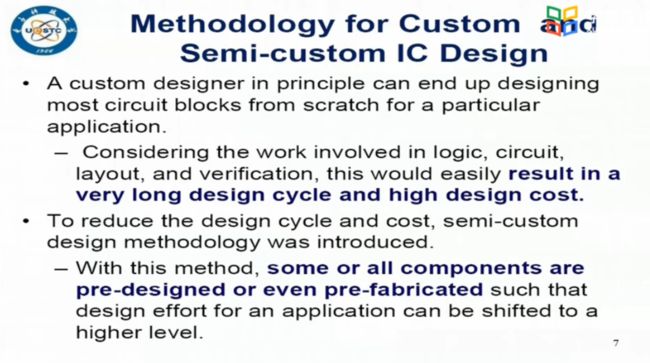

from scratch:白手起家、从头开始。

such that:使得;这样。

design effort:可理解为设计工作。

手绘Geometry(在光掩模上成像的预期图案);

所有层定制;(构成设备的一系列重叠光掩模或光掩模图像中的一个)

数字和模拟;

晶体管级仿真(模拟);

高密度;

高性能;

设计时间长。

PS:对密度的理解

-

光掩模上图案与无图案区域的相对程度,如电路密度(circuit density)

-

给定尺寸下允许的缺陷数,如缺陷密度(defect density)

门阵列:只需要连接现成的门。

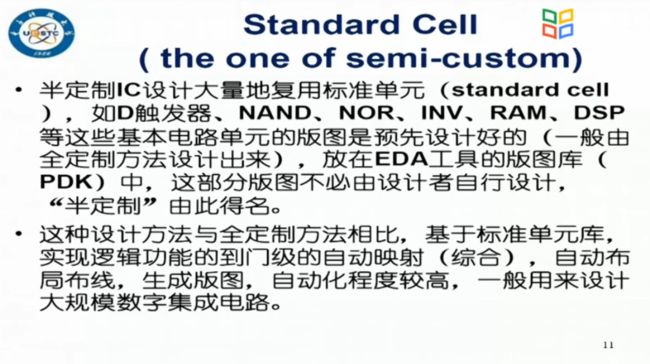

标准单元库:直接用厂家写好的lib库。

PLD:可编程逻辑器件,使用术语PLD来表示低密度结构。

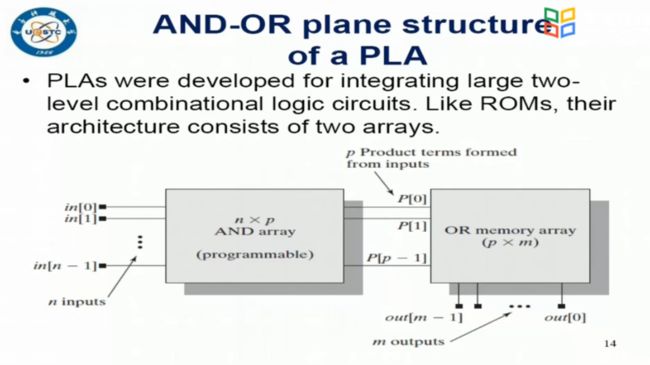

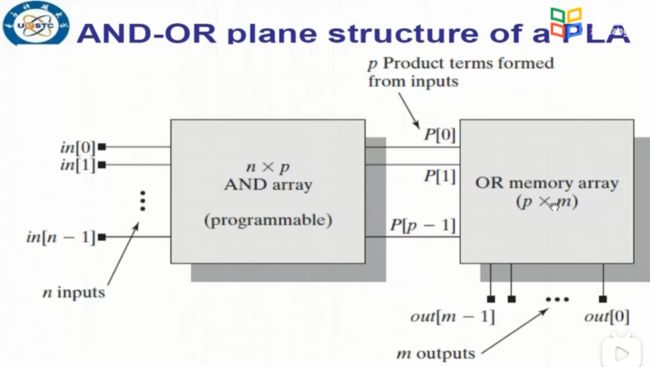

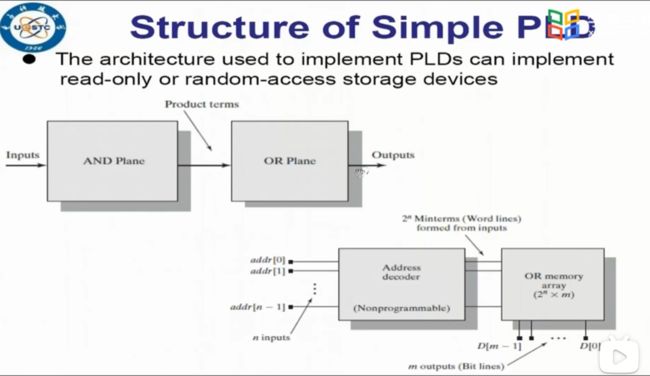

PLA是为集成大型两电平组合逻辑电路而开发的,与ROM一样,它们的体系结构由二维数组组成。

简单的PLD(SPLD):用与或门搭出来的PLA。

复杂的PLD:一个芯片中放很多PLA,互联矩阵。

FPGA 适用于中高密度应用,它们与CPLD在两个重要方面有所不同:

(1)它们的性能取决于设备中针对特定应用实现的路由;

(2)它们的功能由LUT实现,而不是由类似PAL的宽输入与门实现。

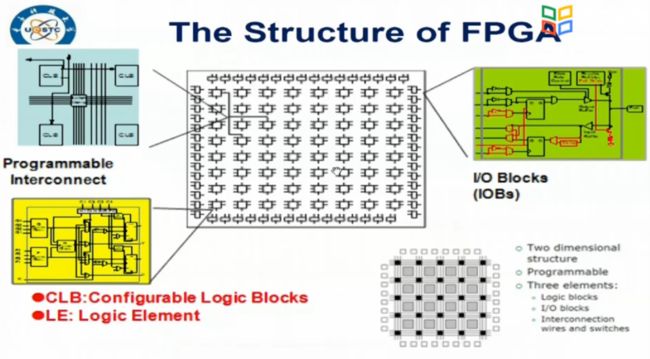

FPGA有三种可编程结构(逻辑资源):

互联矩阵,即连线可编程;

CLB:可重构的逻辑功能块=LE:逻辑单元,可编程;

输出可编程(双向),I/O。

根据开发时间、性能、成本、风险、功能考虑选择全定制还是半定制。

可编程资源(同那三个结构):可编程逻辑块,输入输出块,接口。

存储设备被认为是PLD(可编程逻辑器件)

因为它们可以实现组合逻辑,将函数的值存储在内存里,由函数输入寻址,从而实现了函数的真值表。

PLD的可编程性:PLD可分为ROM、PLA和PLD,都采用了类似的阵列结构实现。

PLA最灵活,用于大型,复杂的组合逻辑电路,各种PLD的可编程选项如表所示。

PLA:可编程逻辑阵列

PLAs是为集成大型二值组合逻辑电路而开发的,与ROM一样,它们的体系结构由两个数组组成。一个数组实现与操作,生成一个乘积项(例如,一个布尔立方体,可能是一个最小项);另一个数组实现形成SOP(sum of product)或操作。

可编程逻辑阵列的基本结构如上,与门和或门可以搭成各种逻辑。(SOP)

左边是与逻辑,右边是或逻辑。

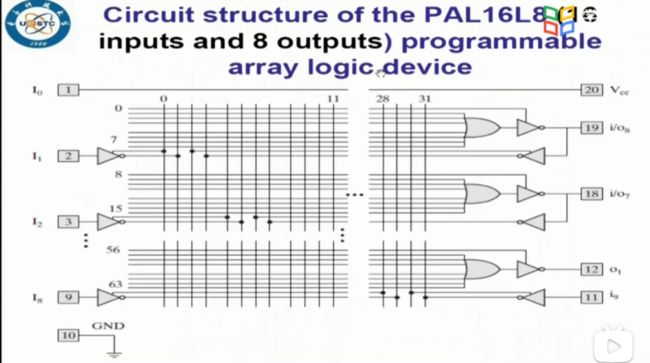

可编程阵列逻辑(PAL):

PAL技术出现在PLA之后,并且通过固定或平面以及只允许对与平面进行编程,简化了双阵列结构。

每个输出由特定数量的行组成,每个行由一些乘积项组成。

一个比较流行的设备是PAL16L8,该设备有16个输入、8个输出;它的封装有20个引脚,包括电源和接地。

一个存储器实现了一个真值表,这也是为什么存储器能做可编程器件。

简单PLD:可以实现只读或随机访问的存储设备。

逻辑有两种:与或逻辑、译码器+或逻辑。

复杂PLD是几个简单PLD堆积起来。

FPGA的基本架构:FPGA有一个固定的体系结构,它是为特定的应用程序在现场编程的。

(1) 可编程功能单元数组 (FU):用于实现组合逻辑和时序逻辑;

(2) 固定但可编程的互连结构:建立信号路由;

(3) 可配置内存:对设备的功能进行编程;

(4) l/O资源:在设备和环境之间提供接口。

FPGA的特点:编程功能强,是结构接近基于库单元的一种ASIC。

功能块可编程,且是阵列结构(FU是基本的功能块);

互联是可编程的;

存储器部分可编程;

数据IO可编程。

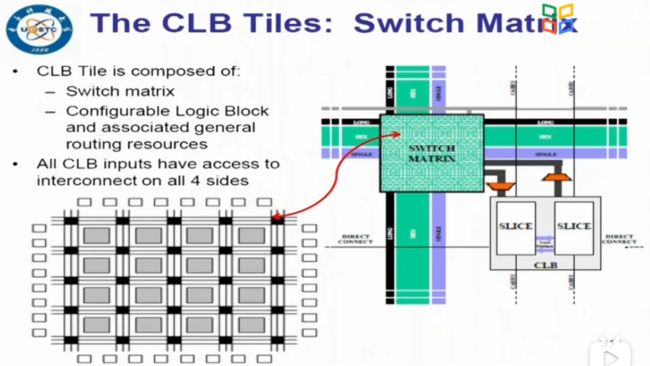

FPGA由三个部分构成:整体是阵列结构。

可编程的功能单元(CLB/LE):核心是黄色部分,基于存储器的,叫查找表,左边是两个存储器,右边是两个寄存器。

可编程的连线:蓝色是路由器,一个小块是一个功能单元,靠连线开关(蓝色)连起来,并路由。

可编程的I/O:绿色是输出IO,可编程(单向、双向、缓冲、寄存)。

FPGA有两种:一种是基于存储器的(基于LUT查找表的),另一种是基于多路选通器的(MUX)。

基于存储器的是主流。

FPGA/PLD把一个真值表(也叫烧写文件、配置文件)放入存储器里,逻辑功能实现可编程。

LUT(查找表):存储器的地址对应LUT的输入,输出对应LUT的输出Z。

CLB:=LE,可编程逻辑模块是FPGA中的核心可配置逻辑单元,FPGA的逻辑功能就是靠CLB单元的配置以及大规模的CLB单元级联来实现的。

只有组合电路才能实现逻辑功能,时序电路只是一个记忆的作用。

使用每个函数发生器(G)作为4输入逻辑(LUT),或高速同步双端口的RAM。

基于查找表的FPGA:

查找表是实现组合逻辑的,不管时序电路;由于输入有限,功能比较简单,容量受限于输入的数量,而不是复杂性;四条地址16个存储单元,延时(输入到输出耗时,代表数据吞吐量)一定。

基于开关的FPGA:根据S的0、1取值选择一个输出,即多路开关,通过a、b值的变化得到与、或功能,得到了基本的逻辑功能。

总结:

基于查找表的:由可编程的功能单元、可编程的连线、可编程的I/O三部分组成。

基于逻辑单元的FPGA:也叫CLB、LE,一个蓝色小块构成一个完整的数字逻辑单元(查找表+D触发器,逻辑+时序)。

寄存器链构成一个移位寄存器。

一般一个查找表对应一个寄存器。

BUFT:Xilinx的原语,表示一个三态缓冲器。

Carry Logic:进位逻辑,存在于每个slice中,是(主要)用于实现算术逻辑功能的专用逻辑。进位逻辑(或称进位链)在Xilinx器件中垂直分布、向上传递。

开关矩阵:小黑块,相当于交换机和路由器功能,在找路。

可编程的互联:白色点把他们连起来,红框是查找表寄存器,通过它找线,线有本地的,也有全局的。

I/O部分也可以编程:

- 快速I/O驱动程序

- 独立的输入、输出和三态控制寄存器

- 异步/同步设置或复位

- 共用时钟和单独时钟可以提高可用性

- 配置为FF(触发器)或latch(锁存器)

- 可编程的转换速率以及可变输入延迟

- 可选择的I/O标准支持

课程来源于互联网,主讲教师李广军。