5-2中央处理器-指令周期的数据流

文章目录

- 一.指令周期

- 二.数据流向

-

- 1.取指周期

- 2.间址周期

- 3.执行周期

- 4.中断周期

- 三.指令执行方案

-

- 1.单指令周期

- 2.多指令周期

- 3.流水线方案

一.指令周期

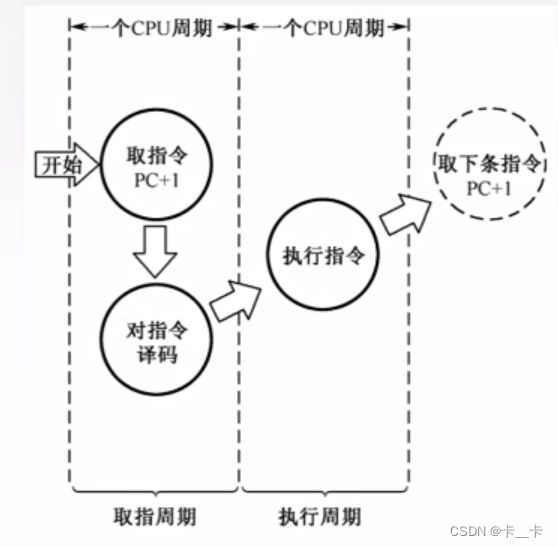

指令周期:CPU从主存中每取出并执行一条指令所需的全部时间。

此处:取指周期=取指令+指令译码

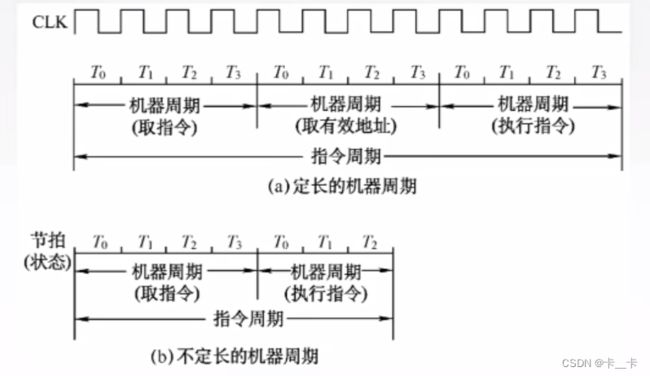

指令周期常用若干机器周期/CPU周期表示,一个机器周期包含若干时钟周期/节拍/T周期/CPU时钟周期,时钟周期是CPU操作的最基本单位

回顾:CPU执行时间=时钟周期数×时钟周期=CPI×指令条数×时钟周期

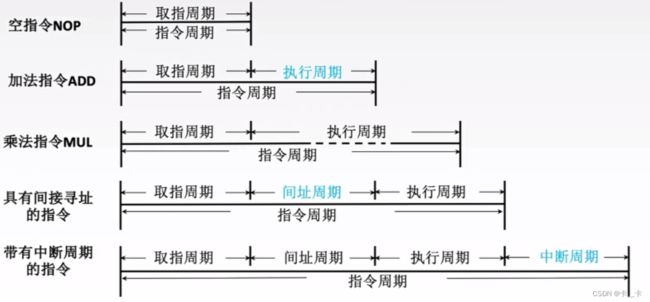

可以看出,每个指令周期内机器周期数可以不等,每个机器周期内的节拍数也可以不等。下面进行举例

1.空指令NOP

取指令,不进行操作。即指令周期=取指周期(包含取指周期和分析指令)。包含1个机器周期

2.加法指令ADD

指令周期=取指周期+执行周期

包含2个机器周期,两个机器周期包含的节拍数可能不同

(若为乘法指令,则执行周期更长)

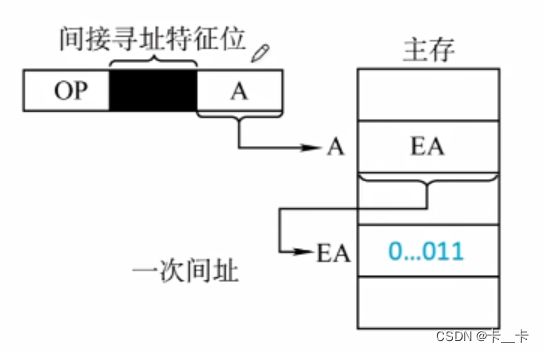

3.具有间接寻址的指令

指令周期=取指周期+间址周期+执行周期

包含3个机器周期,三个机器周期包含的节拍数可能不同

(图:一次间接寻址)

4.带有中断周期的指令

指令周期=取指周期+间址周期+执行周期+中断周期

每一条指令末尾都要检查中断

包含4个机器周期,四个机器周期包含的节拍数可能不同

总结

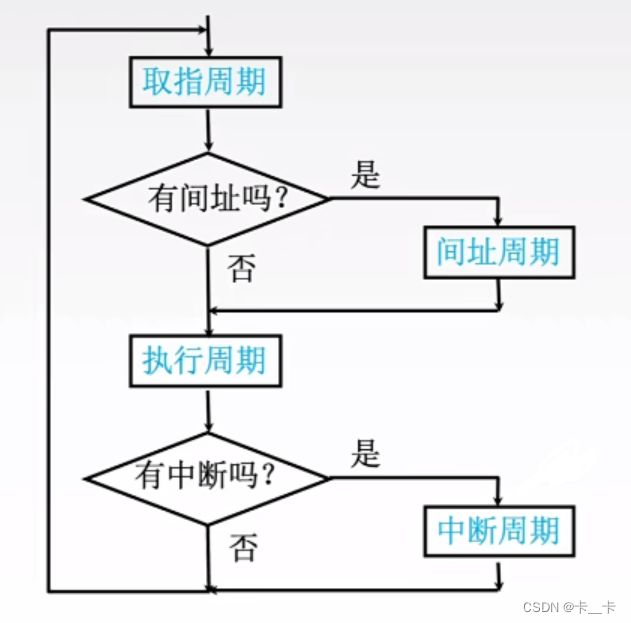

可以通过触发器判断当前处于那个周期

二.数据流向

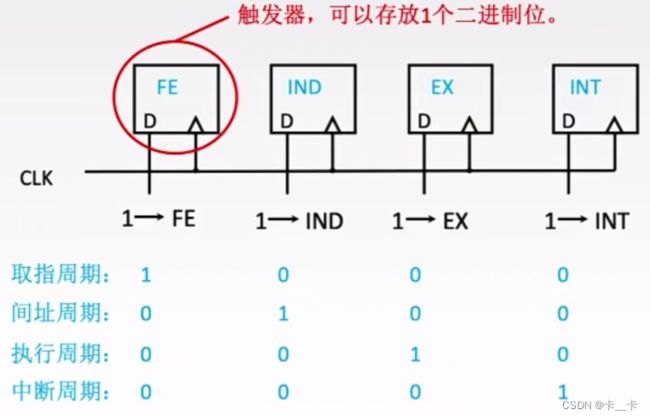

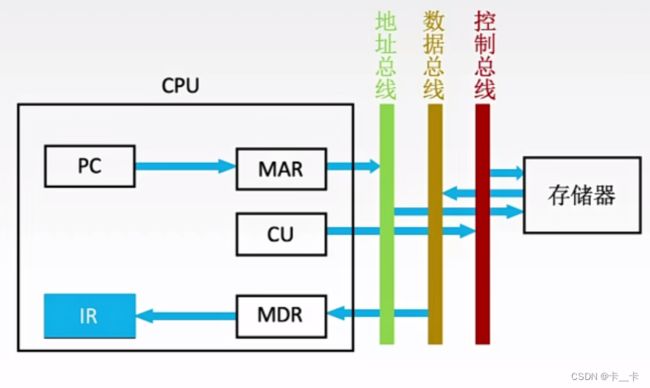

1.取指周期

把PC中的内容从主存取出指令代码并存放到IR中,可能因为取指令进行访存。

数据流向:

①PC指向的内容通过地址总线传送到MAR,即(PC)→MAR

②CU通过控制总线给主存发出控制信号(如:读信号)

③主存储器根据MAR记录的地址信息去存储体中找出该地址对应的二进制数据,通过数据总线将数据放到MDR中,即M(MAR)→MDR

④MDR中的指令通过内部总线放到IR(此处MDR属于CPU),即(MDR)→IR

⑤每取出一条指令,CU发出控制信号,形成下一条指令地址,让PC指向,即(PC)+"1"→PC

或

PC→MAR→地址总线→主存

CU发出控制信号→控制总线→主存

主存→数据总线→MDR→IR

CU发出读命令→PC内容加1

2.间址周期

间址周期的任务是取操作数的有效地址,可能因为取有效地址而访存。

数据流向:

①将指令中的地址码Ad送到MAR并送至地址总线,即Ad(IR)→MAR→地址总线

注:此处的IR可改为MDR,二者当前存放相同的内容

②CU通过控制总线发出控制信号(如读命令)给主存,即CU发出控制信号→控制总线→主存

③主存储器根据MAR记录的地址信息去存储体中找出该地址对应的二进制数据,通过数据总线将数据放到MDR中,即M(MAR)→MDR

④将有效地址送至指令的地址码字段,即(MDR)→Ad(IR)

3.执行周期

执行周期的任务是根据IR中的指令字的操作码和操作数通过ALU操作产生执行结果。可能因为取操作数而访存

不同指令的执行周期操作不同,没有统一的数据流向

4.中断周期

暂停当前任务去完成其他任务,可能因为保存程序断电而访存

为了能够恢复当前任务,需要保存断点。一般使用堆栈来保存断点,这里用SP指向栈顶存储单元的地址,堆栈的地址空间从高到低排列,假设SP指向栈顶元素,进栈时SP-1,再存入数据。

数据流向:

PC自动加“1”,指向下一条待执行指令,此时发送中断。为保存断点,需将PC的值压入主存,然后转向指向中断处理程序

①CU控制SP-1,在当前SP指向的地址插入PC,需将SP所指向的地址送MAR并送至地址总线,即(SP)-1→SP、(SP)→MAR

②CU通过控制总线发出控制信号(写命令)给主存,即CU发出写命令→控制总线→主存

③将PC写入主存,即(PC)→MDR→数据总线→主存

④CU将PC改为中断处理程序的第一条指令地址,即CU→PC

三.指令执行方案

一个指令周期通常要包括几个时间段(执行步骤),每个步骤完成指令的一部分功能,几个依次执行的步骤完成这条指令的全部功能。

可以选用3种方案来安排指令的执行步骤:

1.单指令周期

所有指令选用相同的执行时间。指令之间串行执行,即下一条指令只能在前一条指令执行结束后才能启动。为保证每条指令都在固定的时钟周期内完成,在设计执行时间时需选择最长指令的执行时间,这样会导致本来可以在更短时间内完成的指令,要使用较长的周期来完成,降低了整个系统的运行速度。

2.多指令周期

对不同类型的指令选用不同的执行步骤。指令之间串行执行,但不再要求所有指令占用相同的执行时间,即按需分配。但需要更复杂的硬件设计,成本较高。

3.流水线方案

指令之间可以并行执行的方案。该方案通过在每个时钟周期启动一条指令,尽量让多条指令同时运行,但各自处在不同的执行步骤中。其追求的目标是力争在每个时钟脉冲周期完成一条指令的执行过程。

- 解释时钟周期,指令周期,机器周期以及它们之间的关系

①CPU每取出并执行一条指令所需的全部时间称为指令周期,指令周期常由若干机器周期组成;②机器周期是在同步控制的机器中,执行指令周期中一步相对完整的操作所需的时间,如取指令、取有效地址、执行指令。通常机器周期长度=主存周期。一个机器周期包含若干时钟周期;③时钟周期是指计算机主时钟的周期时间,它是CPU操作的最基本单位,对应完成一个微操作所需的时间,通常时钟周期=计算机主频的倒数。 - 计算机的一条指令有几个机器周期?

一条指令包含的机器周期最多有4个。如空指令包含1个,加法指令包含2个,具有间址寻址的指令包含3个,再带有中短周期的指令包含4个。 - 什么是指令周期?指令周期是否有一个固定值?为什么?

指令周期是指取出并执行完一条指令所需的时间。由于计算机中各种指令执行所需的时间差异很大,因此为了提高CPU运行效率,即使在同步控制的机器中,不同指令的指令周期长度都是不一致的,也就是说指令周期对于不同的指令来说不是一个固定值。